|

|

PDF IDT74LVCH162244A Data sheet ( Hoja de datos )

| Número de pieza | IDT74LVCH162244A | |

| Descripción | 3.3V CMOS 16-BIT BUFFER/DRIVER | |

| Fabricantes | Integrated Device Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IDT74LVCH162244A (archivo pdf) en la parte inferior de esta página. Total 6 Páginas | ||

|

No Preview Available !

IDT74LVCH162244A

3.3V CMOS 16-BIT BUFFER/DRIVER WITH 3-STATE OUTPUTS

INDUSTRIALTEMPERATURERANGE

3.3V CMOS 16-BIT

IDT74LVCH162244A

BUFFER/DRIVER WITH 3-STATE

OUTPUTS, 5 VOLT TOLERANT I/O,

AND BUS-HOLD

FEATURES:

• Typical tSK(o) (Output Skew) < 250ps

• ESD > 2000V per MIL-STD-883, Method 3015; > 200V using

machine model (C = 200pF, R = 0)

• VCC = 3.3V ± 0.3V, Normal Range

• VCC = 2.7V to 3.6V, Extended Range

• CMOS power levels (0.4μ W typ. static)

www.Data•ShAeellt4inUp.cuotsm, outputs, and I/O are 5V tolerant

• Available in SSOP and TSSOP packages

DRIVE FEATURES:

• Balanced Output Drivers: ±12mA

• Full internal series termination

APPLICATIONS:

• 5V and 3.3V mixed voltage systems

• Data communication and telecommunication systems

FUNCTIONAL BLOCK DIAGRAM

DESCRIPTION:

The LVCH162244A 16-bit buffer/driver is built using advanced dual

metal CMOS technology. The LVCH162244A is designed specifically to

improve both the performance and density of 3-state memory address

drivers, clock drivers, and bus-oriented receivers and transmitters. The

device can be used as four 4-bit buffers, two 8-bit buffers, or one 16-bit buffer.

This device provides true outputs and symmetrical active-low output-enable

(OE) inputs.

All pins of this 16-bit buffer/driver can be driven from either 3.3V or 5V

devices. This feature allows the use of this device as a translator in a mixed

3.3V/5V supply system.

The LVCH162244A has series resistors in the device output structure

which will significantly reduce line noise when used with light loads. This

driver has been developed to drive ±12mA at the designated threshold

levels.

The LVCH162244A has “bus-hold” which retains the inputs’ last state

whenever the input goes to a high impedance. This prevents floating inputs

and eliminates the need for pull-up/down resistors.

1OE 1

3OE 25

1A1 47

1A2 46

1A3 44

1A4 43

2 1Y1

3 1Y2

5

1Y3

6 1Y4

3A1 36

3A2 35

3A3 33

3A4 32

13 3Y1

14 3Y2

16

3Y3

17 3Y4

2OE 48

2A1 41

2A2 40

2A3 38

2A4 37

8 2Y1

9 2Y2

11 2Y3

12 2Y4

4OE 24

4A1 30

4A2 29

4A3 27

4A4 26

19 4Y1

20 4Y2

22

4Y3

23 4Y4

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

INDUSTRIAL TEMPERATURE RANGE

© 1999 Integrated Device Technology, Inc.

1

MARCH 1999

DSC-4727/4

1 page

IDT74LVCH162244A

3.3V CMOS 16-BIT BUFFER/DRIVER WITH 3-STATE OUTPUTS

INDUSTRIALTEMPERATURERANGE

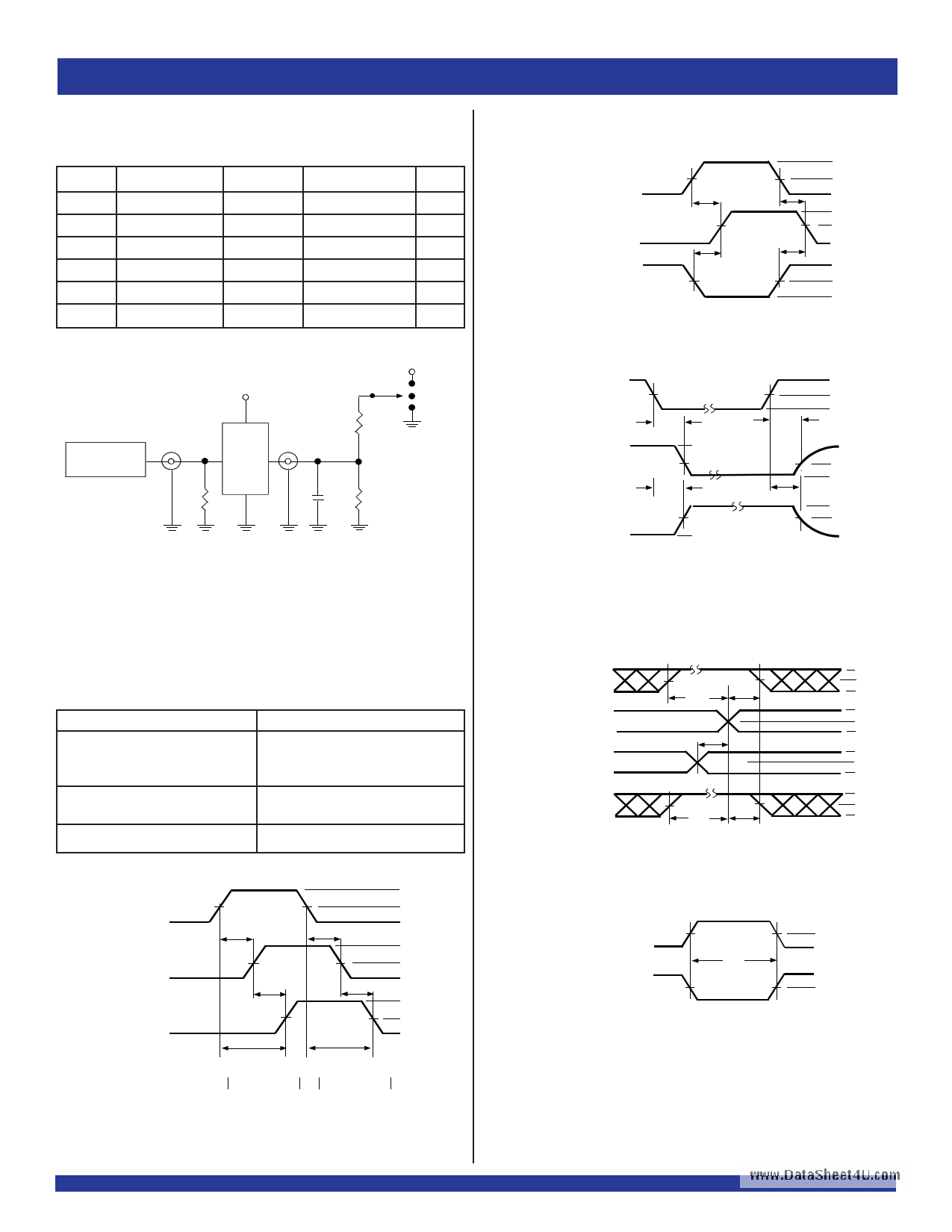

TEST CIRCUITS AND WAVEFORMS

TEST CONDITIONS

Symbol VCC(1)= 3.3V±0.3V VCC(1)= 2.7V

VLOAD

6

6

VIH 2.7

2.7

VT 1.5

1.5

VLZ 300

300

VHZ 300

300

CL 50

50

VCC(2)= 2.5V±0.2V

2 x Vcc

Vcc

Vcc / 2

150

150

30

Unit

V

V

V

mV

mV

pF

SAME PHASE

INPUT TRANSITION

OUTPUT

tPLH

OPPOSITE PHASE

INPUT TRANSITION

tPLH

tPHL

tPHL

VIH

VT

0V

VOH

VT

VOL

VIH

VT

0V

LVC Link

www.DataSheet4U.com

VIN

Pulse (1, 2)

Generator

VCC

VOUT

D.U.T.

500Ω

VLOAD

Open

GND

RT

500Ω

CL

Test Circuit for All Outputs

LVC Link

DEFINITIONS:

CL = Load capacitance: includes jig and probe capacitance.

RT = Termination resistance: should be equal to ZOUT of the Pulse Generator.

NOTES:

1. Pulse Generator for All Pulses: Rate ≤ 10MHz; tF ≤ 2.5ns; tR ≤ 2.5ns.

2. Pulse Generator for All Pulses: Rate ≤ 10MHz; tF ≤ 2ns; tR ≤ 2ns.

SWITCH POSITION

Test

Open Drain

Disable Low

Enable Low

Disable High

Enable High

All Other Tests

Switch

VLOAD

GND

Open

Propagation Delay

CONTROL

INPUT

ENABLE

tPZL

DISABLE

tPLZ

OUTPUT

NORMALLY

LOW

SWITCH

CLOSED

tPZH

OUTPUT SWITCH

NORMALLY OPEN

HIGH

VLOAD/2

VT

tPHZ

VT

0V

VIH

VT

0V

VLOAD/2

VLZ

VOL

VOH

VHZ

0V

LVC Link

Enable and Disable Times

NOTE:

1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

DATA

INPUT

TIMING

INPUT

ASYNCHRONOUS

CONTROL

SYNCHRONOUS

CONTROL

tSU tH

tREM

tSU tH

VIH

VT

0V

VIH

VT

0V

VIH

VT

0V

VIH

VT

0V

LVC Link

INPUT

OUTPUT 1

OUTPUT 2

tPLH1

tPHL1

tSK (x)

tSK (x)

VIH

VT

0V

VOH

VT

VOL

VOH

VT

VOL

tPLH2

tPHL2

tSK(x) = tPLH2 - tPLH1 or tPHL2 - tPHL1

Output Skew - tSK(X)

LVC Link

NOTES:

1. For tSK(o) OUTPUT1 and OUTPUT2 are any two outputs.

2. For tSK(b) OUTPUT1 and OUTPUT2 are in the same bank.

5

Set-up, Hold, and Release Times

LOW-HIGH-LOW

PULSE

HIGH-LOW-HIGH

PULSE

tW

VT

VT

LVC Link

Pulse Width

5 Page | ||

| Páginas | Total 6 Páginas | |

| PDF Descargar | [ Datasheet IDT74LVCH162244A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IDT74LVCH162244A | 3.3V CMOS 16-BIT BUFFER/DRIVER | Integrated Device Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |