|

|

PDF HYI18T1G800B Data sheet ( Hoja de datos )

| Número de pieza | HYI18T1G800B | |

| Descripción | 1-Gbit Double-Data-Rate-Two SDRAM | |

| Fabricantes | Qimonda | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HYI18T1G800B (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

July 2007

HY[B/I]18T1G400B[F/C](L)

HY[B/I]18T1G800B[F/C](L)

HY[B/I]18T1G16[0/7]B[F/C](L/V)

www.DataSheet4U.com

1-Gbit Double-Data-Rate-Two SDRAM

DDR2 SDRAM

RoHS Compliant Products

Internet Data Sheet

Rev. 1.3

1 page

Internet Data Sheet

HY[B/I]18T1G[40/80/16]0B[C/F](L/V)

1-Gbit Double-Data-Rate-Two SDRAM

1.2 Description

The 1-Gbit DDR2 DRAM is a high-speed Double-Data-Rate-

Two CMOS Synchronous DRAM device, containing

1,073,741,824 bits and internally configured as anoctal

quadbank DRAM. The 1-Gbit device is organized as either

32 Mbit ×4 I/O ×8 banks, 16 Mbit ×8 I/O ×8 banks or 8 Mbit

www.DataShe×e1t46UI.c/Oom×8 banks chip. These devices achieve high speed

transfer rates starting at 400 Mb/sec/pin for general

applications.

The device is designed to comply with all DDR2 SDRAM key

features:

1. Posted CAS with additive latency,

2. Write latency = read latency - 1,

3. Normal and weak strength data-output driver,

4. Off-Chip Driver (OCD) impedance adjustment

5. On-Die Termination (ODT) function.

All of the control and address inputs are synchronized with a

pair of externally supplied differential clocks. Inputs are

latched at the cross point of differential clocks (CK rising and

CK falling). All I/Os are synchronized with a single ended

DQS or differential DQS-DQS pair in a source synchronous

fashion.

A 17-bit address bus for ×4 and ×8 organised components

and a 16 bit address bus for ×16 components is used to

convey row, column and bank address information in a RAS-

CAS multiplexing style.

The DDR2 device operates with a 1.8 V ± 0.1 V power

supply. An Auto-Refresh and Self-Refresh mode is provided

along with various power-saving power-down modes.

The functionality described and the timing specifications

included in this data sheet are for the DLL Enabled mode of

operation.

The DDR2 SDRAM is available in P(G)-TFBGA-68 and P(G)-

TFBGA-84 packages.

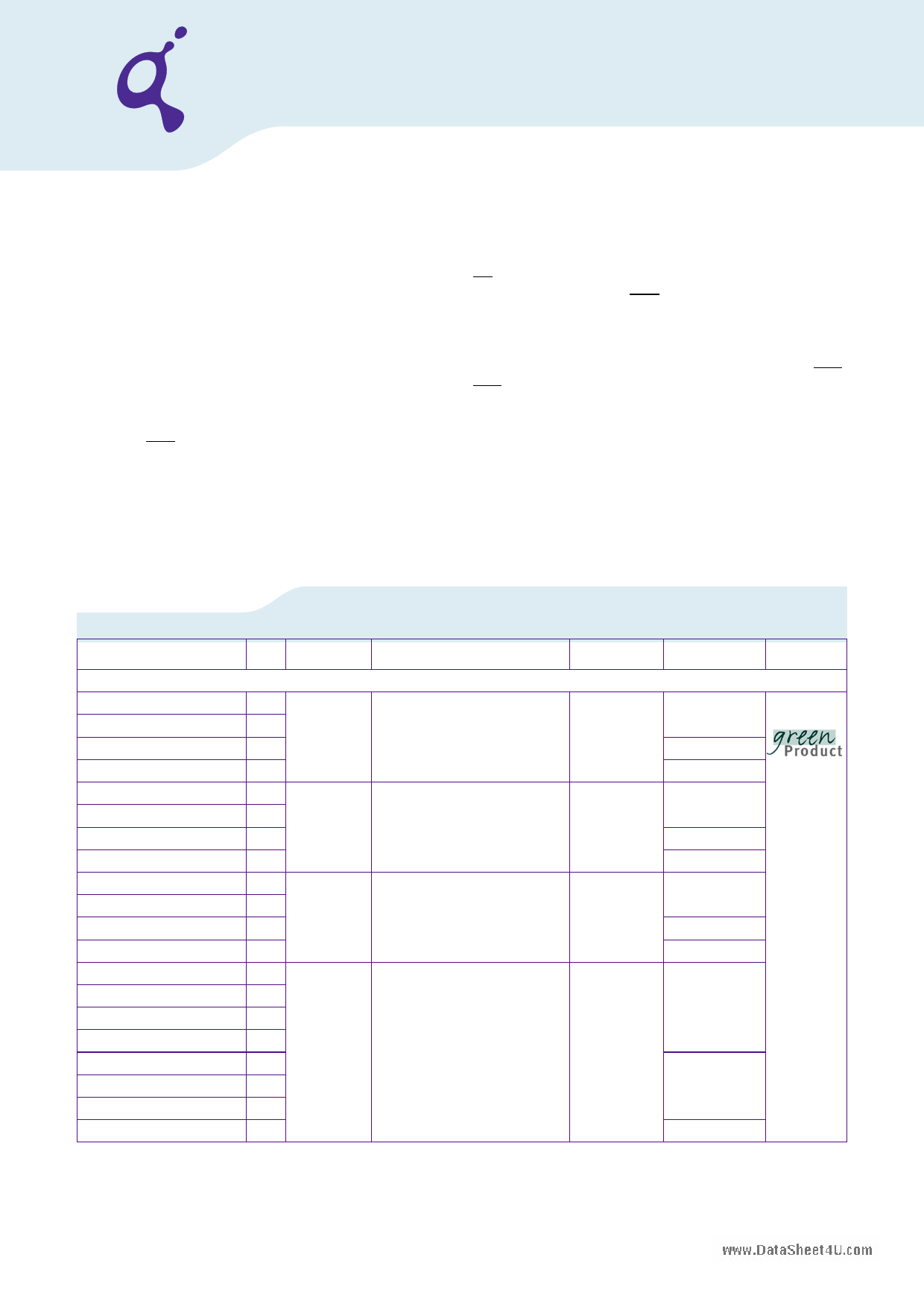

Product Type

Org. Speed

TABLE 5

Ordering Information for Lead-Free Products (RoHS Compliant)

CAS-RCD-RP Latencies1)2)3) Clock (MHz) Package

Note

Standard Temperature Range (0 °C - +70 °C)

HYB18T1G400BF-2.5F ×4 DDR2-800D 5-5-5

HYB18T1G800BF-2.5F ×8

HYB18T1G160BF-2.5F ×16

HYB18T1G167BF-2.5F ×16

HYB18T1G400BF-2.5 ×4 DDR2-800E 6-6-6

HYB18T1G800BF-2.5 ×8

HYB18T1G160BF-2.5 ×16

HYB18T1G167BF-2.5 ×16

HYB18T1G400BF-3

×4 DDR2-667C 4-4-4

HYB18T1G800BF-3

×8

HYB18T1G160BF-3

×16

HYB18T1G167BF-3

×16

HYB18T1G400BF-3S

×4 DDR2-667D 5-5-5

HYB18T1G400BFL-3S ×4

HYB18T1G800BF-3S

×8

HYB18T1G800BFL-3S ×8

HYB18T1G160BF-3S

×16

HYB18T1G160BFL-3S ×16

HYB18T1G160BFV-3S ×16

HYB18T1G167BF-3S

×16

400 PG-TFBGA-68 4)

PG-TFBGA-84

PG-TFBGA-92

400 PG-TFBGA-68

PG-TFBGA-84

PG-TFBGA-92

333 PG-TFBGA-68

PG-TFBGA-84

PG-TFBGA-92

333 PG-TFBGA-68

PG-TFBGA-84

PG-TFBGA-92

Rev. 1.3, 2007-07

03062006-ZNH8-HURV

5

5 Page

Internet Data Sheet

HY[B/I]18T1G[40/80/16]0B[C/F](L/V)

1-Gbit Double-Data-Rate-Two SDRAM

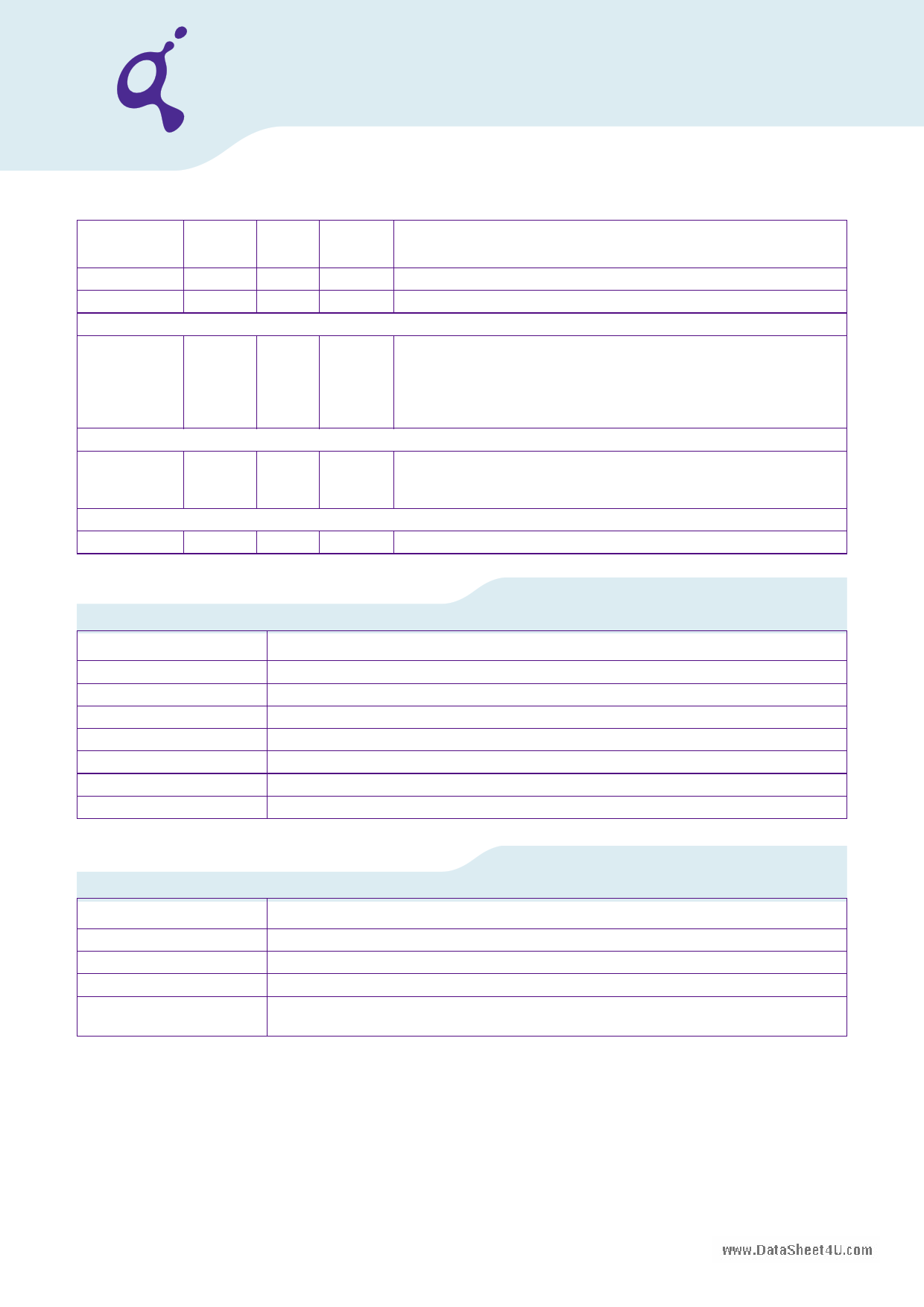

Ball#

Name

Ball

Type

J1

VDDL

PWR

J7

VSSDL

PWR

Not Connected ×4 Organizations

A1, A2, A8, A9,

www.DataSheeEt42U, .Fc9o,mH1,F1,

R7, H9, W1,

W2, W8, W9,

R3

NC

NC

Not Connected ×8 Organization

A1, A2, A8, A9, NC

R7, W1, W2,

W8, W9, R3

NC

Other Balls ×4×8 Organizations

K9

ODT

I

Buffer

Type

—

—

—

—

SSTL

Function

Power Supply

Power Supply

Not Connected

Not Connected

On-Die Termination Control

Abbreviation

I

O

I/O

AI

PWR

GND

NC

Description

Standard input-only ball. Digital levels.

Output. Digital levels.

I/O is a bidirectional input/output signal.

Input. Analog levels.

Power

Ground

Not Connected

TABLE 8

Abbreviations for Ball Type

Abbreviation

SSTL

LV-CMOS

CMOS

OD

TABLE 9

Abbreviations for Buffer Type

Description

Serial Stub Terminated Logic (SSTL_18)

Low Voltage CMOS

CMOS Levels

Open Drain. The corresponding ball has 2 operational states, active low and tristate, and

allows multiple devices to share as a wire-OR.

Rev. 1.3, 2007-07

03062006-ZNH8-HURV

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HYI18T1G800B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HYI18T1G800B | 1-Gbit Double-Data-Rate-Two SDRAM | Qimonda |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |