|

|

PDF DS1497 Data sheet ( Hoja de datos )

| Número de pieza | DS1497 | |

| Descripción | (DS1495 / DS1497) RAMified Real Time Clock | |

| Fabricantes | Dallas Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DS1497 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

DS1495/DS1497

DS1495/DS1497

RAMified Real Time Clock

FEATURES

• Ideal for EISA bus PCs

• Functionally compatible with MC146818 in 32 KHz

mode

• Totally nonvolatile with over 10 years of operation in

www.DataSheet4U.comthe absence of power

• Self-contained subsystem includes lithium, quartz,

and support circuitry

• Counts seconds, minutes, hours, day of the week,

date, month, and year with leap year compensation

• Binary or BCD representations of time, calendar, and

alarm

• 12- or 24-hour clock with AM and PM in 12-hour mode

• Daylight Savings Time option

• Interfaced with software as 64 register/RAM locations

plus 8K x 8 of static RAM

– 14 bytes of clock and control registers

– 50 bytes of general and control registers

– Separate 8K x 8 nonvolatile SRAM

• Programmable square wave output signal

• Bus-compatible interrupt signals (IRQ)

• Three interrupts are separately software-maskable

and testable:

– Time-of-day alarm once/second to once/day

– Periodic rates from 122 µs to 500 ms

– End-of-clock update cycle

• 28-pin JEDEC footprint

• Available as chip (DS1495/DS1495S) or stand alone

module with embedded lithium battery and crystal

(DS1497)

ORDERING INFORMATION

DS1495

DS1495S

DS1497

RTC Chip; 28–pin DIP

RTC Chip; 28–pin SOIC

RTC Module; 28–pin DIP

PIN ASSIGNMENT

A0

A1

X2

X1

STBY

D0

D1

D2

D3

D4

D5

D6

D7

VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28 A2

27 A3

26 VDD

25 SQW

24 A4

23 A5

22 VBAT

21 IRQ

20 RESET

19 RD

18 BGND

17 WR

16 XRAM

15 RTC

DS1495S 28-Pin SOIC (330 mil)

A0

A1

X2

X1

STBY

D0

D1

D2

D3

D4

D5

D6

D7

VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28 A2

27 A3

26 VDD

25 SQW

24 A4

23 A5

22 VBAT

21 IRQ

20 RESET

19 RD

18 BGND

17 WR

16 XRAM

15 RTC

DS1495 28-Pin DIP (600 mil)

A0

A1

NC

NC

STBY

D0

D1

D2

D3

D4

D5

D6

D7

V SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28 A2

27 A3

26 VDD

25 SQW

24 A4

23 A5

22 NC

21 IRQ

20 RESET

19 RD

18 NC

17 WR

16 XRAM

15 RTC

DS1497 28-Pin Encapsulated Package (720 mil)

ECopyright 1995 by Dallas Semiconductor Corporation.

All Rights Reserved. For important information regarding

patents and other intellectual property rights, please refer to

Dallas Semiconductor databooks.

020894 1/19

1 page

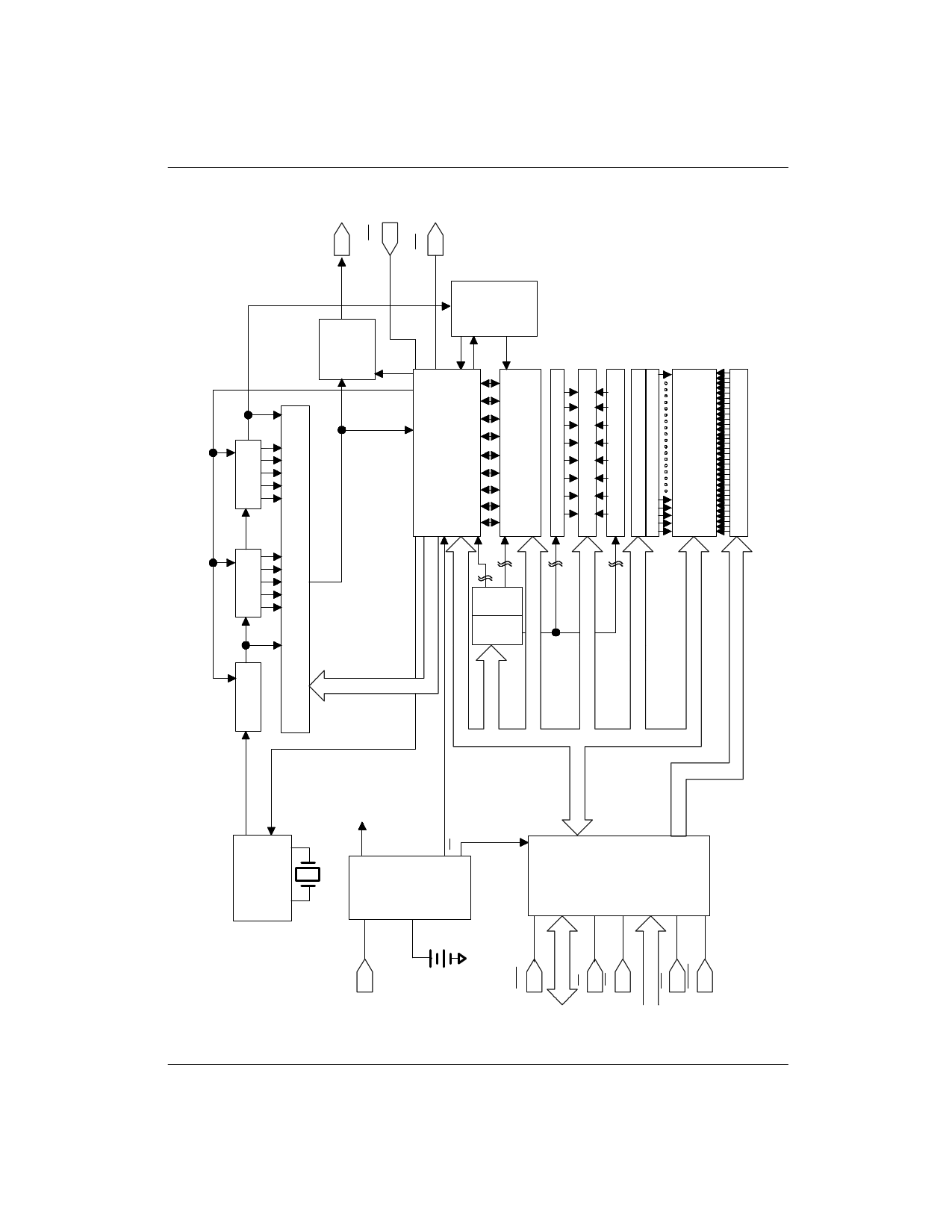

DS149X BLOCK DIAGRAM Figure 1

www.DataSheet4U.com

DS1495/DS1497

020894 5/19

5 Page

DS1495/DS1497

DSE - The Daylight Savings Enable (DSE) bit is a read/

write bit which enables two special updates when DSE

is set to one. On the first Sunday in April the time incre-

ments from 1:59:59 AM to 3:00:00 AM. On the last

Sunday in October when the time first reaches 1:59:59

AM it changes to 1:00:00 AM. These special updates do

not occur when the DSE bit is a zero. This bit is not af-

fected by internal functions.

REGISTER C

MSB

BIT 7 BIT 6

IRQF PF

BIT 5

AF

BIT 4

UF

BIT 3

0

BIT 2

0

BIT 1

0

LSB

BIT 0

0

IRQF – The Interrupt Request Flag (IRQF) bit is set to a

www.DataSheet4U.coomne when one or more of the following are true:

PF = PIE = 1

AF = AIE = 1

UF = UIE = 1

i.e., IRQF = (PF • PIE) + (AF • AIE) + (UF • UIE)

Any time the IRQF bit is a one, the IRQ pin is driven low.

All flag bits are cleared after Register C is read by the

program or when the RESET pin is low.

PF – The Periodic Interrupt Flag (PF) is a read-only bit

which is set to a one when an edge is detected on the

selected tap of the divider chain. The RS3 through RS0

bits establish the periodic rate. PF is set to a one inde-

pendent of the state of the PIE bit. When both PF and

PIE are ones, the IRQ signal is active and will set the

IRQF bit. The PF bit is cleared by a software read of

Register C or by RESET.

AF – A one in the Alarm Interrupt Flag (AF) bit indicates

that the current time has matched the alarm time. If the

AIE bit is also a one, the IRQ pin will go low and a one will

appear in the IRQF bit. A read of Register C or a RESET

will clear AF.

UF – The Update Ended Interrupt Flag (UF) bit is set af-

ter each update cycle. When the UIE bit is set to one, the

one in UF causes the IRQF bit to be a one which will as-

sert the IRQ pin. UF is cleared by reading Register C or

by RESET.

BIT 0 THROUGH BIT 3 – These are reserved bits of the

status Register C. These bits always read zero and can-

not be written.

REGISTER D

MSB

BIT 7 BIT 6

VRT

0

BIT 5

0

BIT 4

0

BIT 3

0

BIT 2

0

BIT 1

0

LSB

BIT 0

0

VRT – The Valid RAM and Time (VRT) bit is set to the

one state by Dallas Semiconductor Corporation prior to

shipment. This bit is not writable and should always be a

one when read. If a zero is ever present, an exhausted

internal lithium energy source is indicated and both the

contents of the RTC data and RAM data are question-

able.

BIT 6 THROUGH BIT 0 – The remaining bits of Register

D are reserved and not usable. They cannot be written

and, when read, they will always read zero.

020894 11/19

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet DS1497.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS1490F | 2-in-1 Fob | Dallas Semiconductor |

| DS1495 | (DS1495 / DS1497) RAMified Real Time Clock | Dallas Semiconductor |

| DS1497 | (DS1495 / DS1497) RAMified Real Time Clock | Dallas Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |