|

|

PDF K4H560438D-TCB3 Data sheet ( Hoja de datos )

| Número de pieza | K4H560438D-TCB3 | |

| Descripción | 256Mb D-die DDR Sdram | |

| Fabricantes | Samsung Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de K4H560438D-TCB3 (archivo pdf) en la parte inferior de esta página. Total 25 Páginas | ||

|

No Preview Available !

256Mb

Key Features

• Double-data-rate architecture; two data transfers per clock cycle

• Bidirectional data strobe(DQS)

• Four banks operation

• Differential clock inputs(CK and CK)

• DLL aligns DQ and DQS transition with CK transition

• MRS cycle with address key programs

-. Read latency 2, 2.5 (clock)

www.DataShee-t4. UB.ucrosmt length (2, 4, 8)

-. Burst type (sequential & interleave)

• All inputs except data & DM are sampled at the positive going edge of the system clock(CK)

• Data I/O transactions on both edges of data strobe

• Edge aligned data output, center aligned data input

• LDM,UDM/DM for write masking only

• Auto & Self refresh

• 7.8us refresh interval(8K/64ms refresh)

• Maximum burst refresh cycle : 8

• 66pin TSOP II package

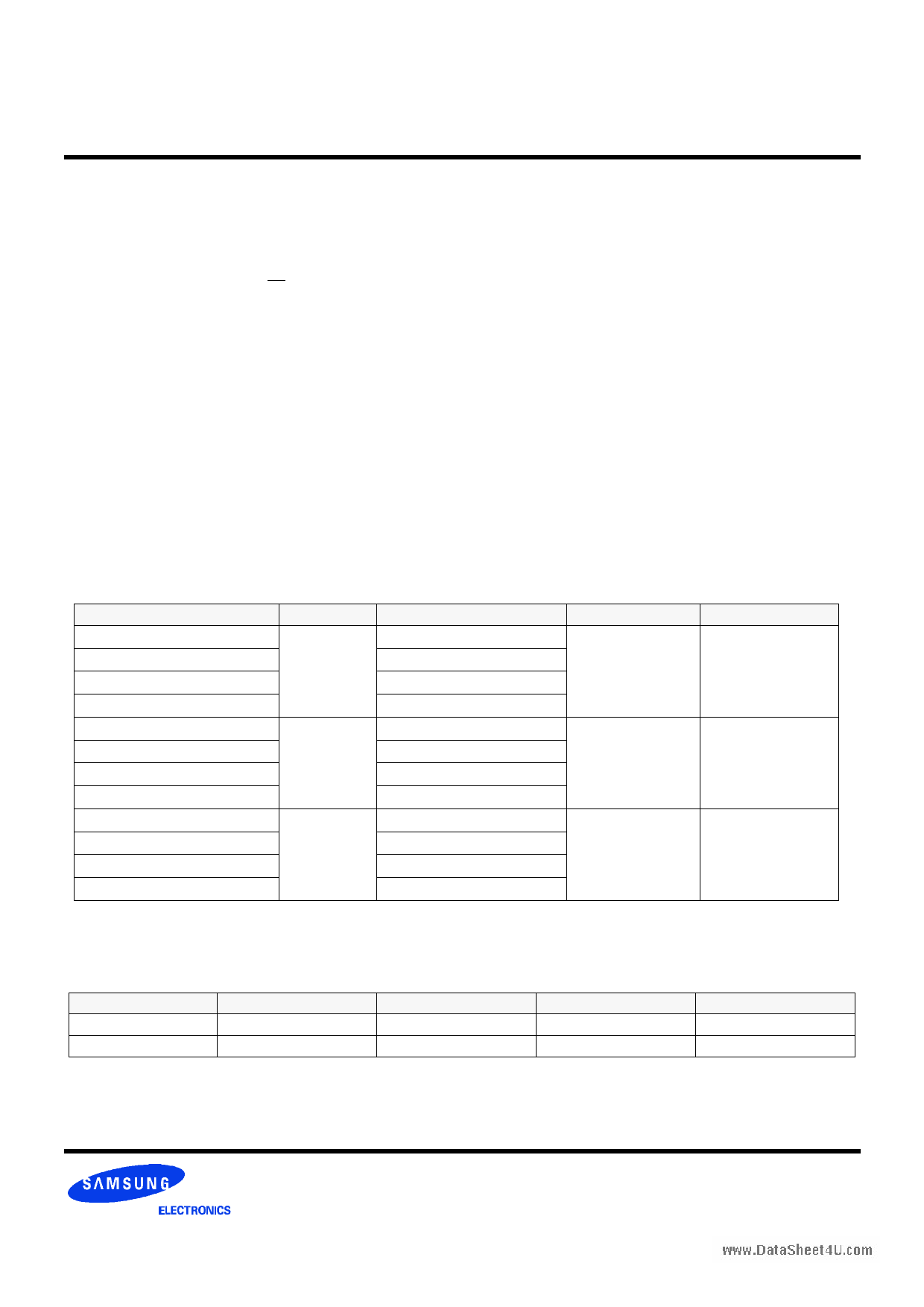

ORDERING INFORMATION

Part No.

K4H560438D-TC/LB3

K4H560438D-TC/LA2

K4H560438D-TC/LB0

K4H560438D-TC/LA0

K4H560838D-TC/LB3

K4H560838D-TC/LA2

K4H560838D-TC/LB0

K4H560838D-TC/LA0

K4H561638D-TC/LB3

K4H561638D-TC/LA2

K4H561638D-TC/LB0

K4H561638D-TC/LA0

Org.

64M x 4

32M x 8

16M x 16

Max Freq.

B3(DDR333@CL=2.5)

A2(DDR266@CL=2)

B0(DDR266@CL=2.5)

A0(DDR200@CL=2)

B3(DDR333@CL=2.5)

A2(DDR266@CL=2)

B0(DDR266@CL=2.5)

A0(DDR200@CL=2)

B3(DDR333@CL=2.5)

A2(DDR266@CL=2)

B0(DDR266@CL=2.5)

A0(DDR200@CL=2)

Interface

SSTL2

SSTL2

SSTL2

DDR SDRAM

Package

66pin TSOP II

66pin TSOP II

66pin TSOP II

Operating Frequencies

Speed @CL2

Speed @CL2.5

- B3(DDR333)

133MHz

166MHz

*CL : Cas Latency

- A2(DDR266A)

133MHz

133MHz

- B0(DDR266B)

100MHz

133MHz

- A0(DDR200)

100MHz

-

Rev. 0.4 May. 2002

-1-

1 page

256Mb

Block Diagram (4Mbit x 16 I/O x 4 Banks)

DDR SDRAM

www.DataSheet4U.com

ADD

Bank Select

CK, CK

16

Data Input Register

Serial to parallel

LWE

LDM

32

2Mx32

2Mx32

2Mx32

2Mx32

32 16

x16

DQi

Column Decoder

Latency & Burst Length

LCKE

LRAS LCBR LWE

Programming Register

LCAS

LWCBR

Timing Register

CK, CK

LDM

Data Strobe

CK, CK CKE CS RAS CAS WE L(U)DM

Rev. 0.4 May. 2002

-5-

5 Page

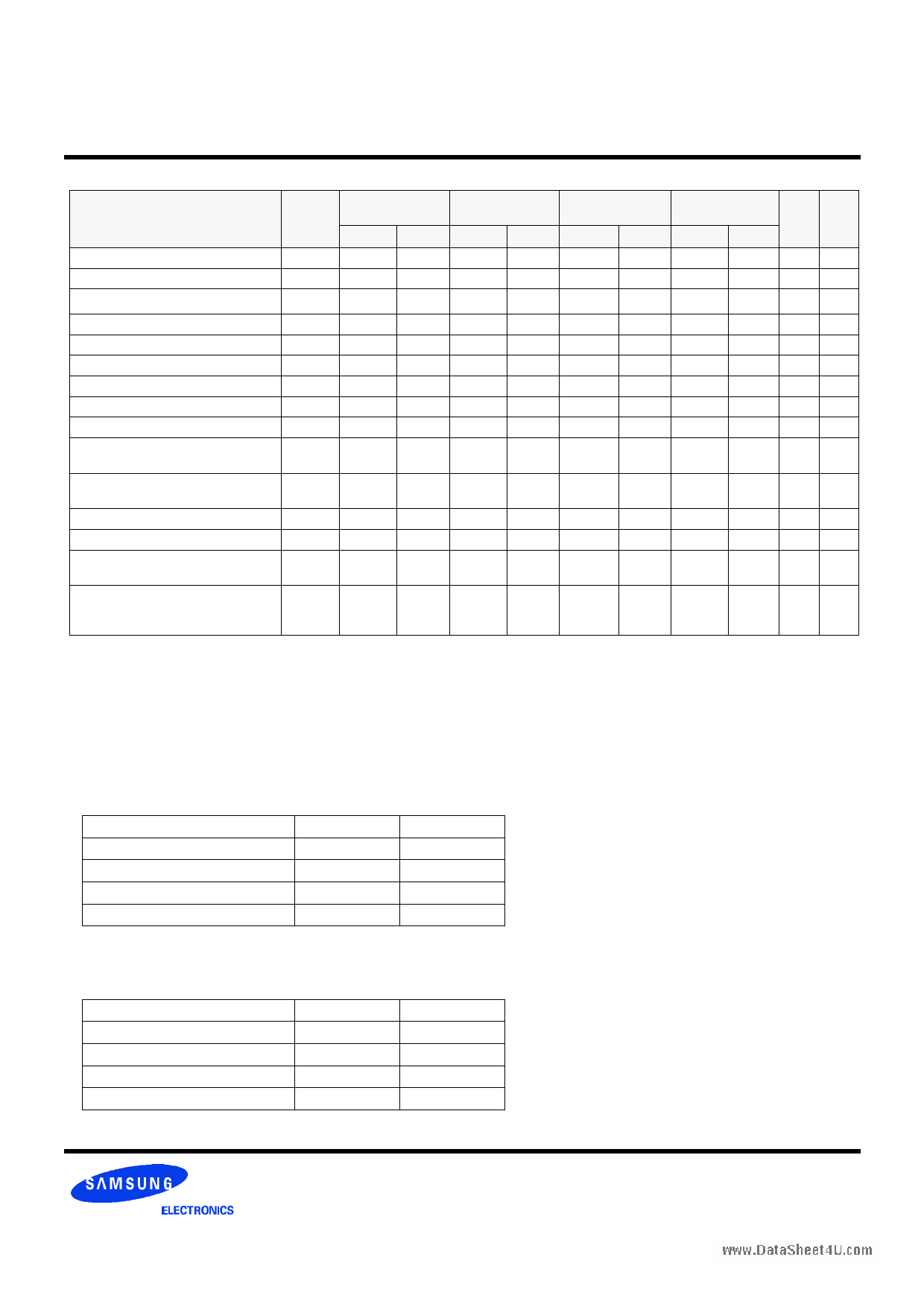

K4H560438D

DDR SDRAM

Parameter

Symbol

-TC/LB3

(DDR333)

Min Max

-TC/LA2

(DDR266A)

Min Max

-TC/LB0

(DDR266B)

Min Max

-TC/LA0

(DDR200)

Min Max

Unit Note

Mode register set cycle time

tMRD

12

15

15

16 ns

DQ & DM setup time to DQS

tDS 0.45

0.5

0.5

0.6 ns 7,8,9

DQ & DM hold time to DQS

tDH 0.45

0.5

0.5

0.6 ns 7,8,9

Control & Address input pulse width

tIPW

2.2

2.2

2.2

2.5 ns

DQ & DM input pulse width

www.DataShPeoewt4eUr .dcoowmn exit time

tDIPW

tPDEX

1.75

6

1.75

7.5

1.75

7.5

2 ns

10 ns

Exit self refresh to non-Read command tXSNR

75

75

75

80 ns 4

Exit self refresh to read command

tXSRD

200

200

200

200 tCK

Refresh interval time

tREFI

7.8

7.8

7.8

7.8 us 1

Output DQS valid window

tQH

tHP

-tQHS

-

tHP

-tQHS

-

tHP

-tQHS

-

tHP

-tQHS

-

ns 5

Clock half period

tHP

tCLmin

or tCHmin

-

tCLmin

or tCHmin

-

tCLmin

or tCHmin

-

tCLmin

or tCHmin

-

ns

Data hold skew factor

tQHS

0.55

0.75

0.75

0.8 ns

DQS write postamble time

tWPST

0.4

0.6

0.4

0.6

0.4

0.6

0.4 0.6 tCK 3

Active to Read with Auto precharge

command

tRAP

18

20

20

20

Autoprecharge write recovery +

Precharge time

tDAL

(tWR/tCK)

+

(tRP/tCK)

(tWR/tCK)

+

(tRP/tCK)

(tWR/tCK)

+

(tRP/tCK)

(tWR/tCK)

+

(tRP/tCK)

tCK 11

1. Maximum burst refresh cycle : 8

2. The specific requirement is that DQS be valid(High or Low) on or before this CK edge. The case shown(DQS going from

High_Z to logic Low) applies when no writes were previously in progress on the bus. If a previous write was in progress,

DQS could be High at this time, depending on tDQSS.

3. The maximum limit for this parameter is not a device limit. The device will operate with a great value for this parameter,

but system performance (bus turnaround) will degrade accordingly.

4. A write command can be applied with tRCD satisfied after this command.

5. For registered DIMMs, tCL and tCH are ≥ 45% of the period including both the half period jitter (tJIT(HP)) of the PLL and the half period

jitter due to crosstalk (tJIT(crosstalk)) on the DIMM.

6. Input Setup/Hold Slew Rate Derating

Input Setup/Hold Slew Rate

∆tIS

∆tIH

(V/ns)

(ps) (ps)

0.5 0 0

0.4 +50 +50

0.3

+100

+100

This derating table is used to increase tIS/tIH in the case where the input slew rate is below 0.5V/ns. Input setup/hold slew rate

based on the lesser of AC-AC slew rate and DC-DC slew rate.

7. I/O Setup/Hold Slew Rate Derating

I/O Setup/Hold Slew Rate

∆tDS

∆tDH

(V/ns)

(ps) (ps)

0.5 0 0

0.4 +75 +75

0.3

+150

+150

This derating table is used to increase tDS/tDH in the case where the I/O slew rate is below 0.5V/ns. I/O setup/hold slew rate

based on the lesser of AC-AC slew rate and DC-DC slew rate.

Rev. 0.4 May. 2002

- 11 -

11 Page | ||

| Páginas | Total 25 Páginas | |

| PDF Descargar | [ Datasheet K4H560438D-TCB3.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K4H560438D-TCB0 | 128Mb DDR SDRAM | Samsung |

| K4H560438D-TCB3 | 256Mb D-die DDR Sdram | Samsung Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |