|

|

PDF UDA1355H Data sheet ( Hoja de datos )

| Número de pieza | UDA1355H | |

| Descripción | Stereo audio codec | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de UDA1355H (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

www.DataSheet4U.com

UDA1355H

Stereo audio codec with SPDIF

interface

Preliminary specification

2003 Apr 10

1 page

Philips Semiconductors

Stereo audio codec with SPDIF interface

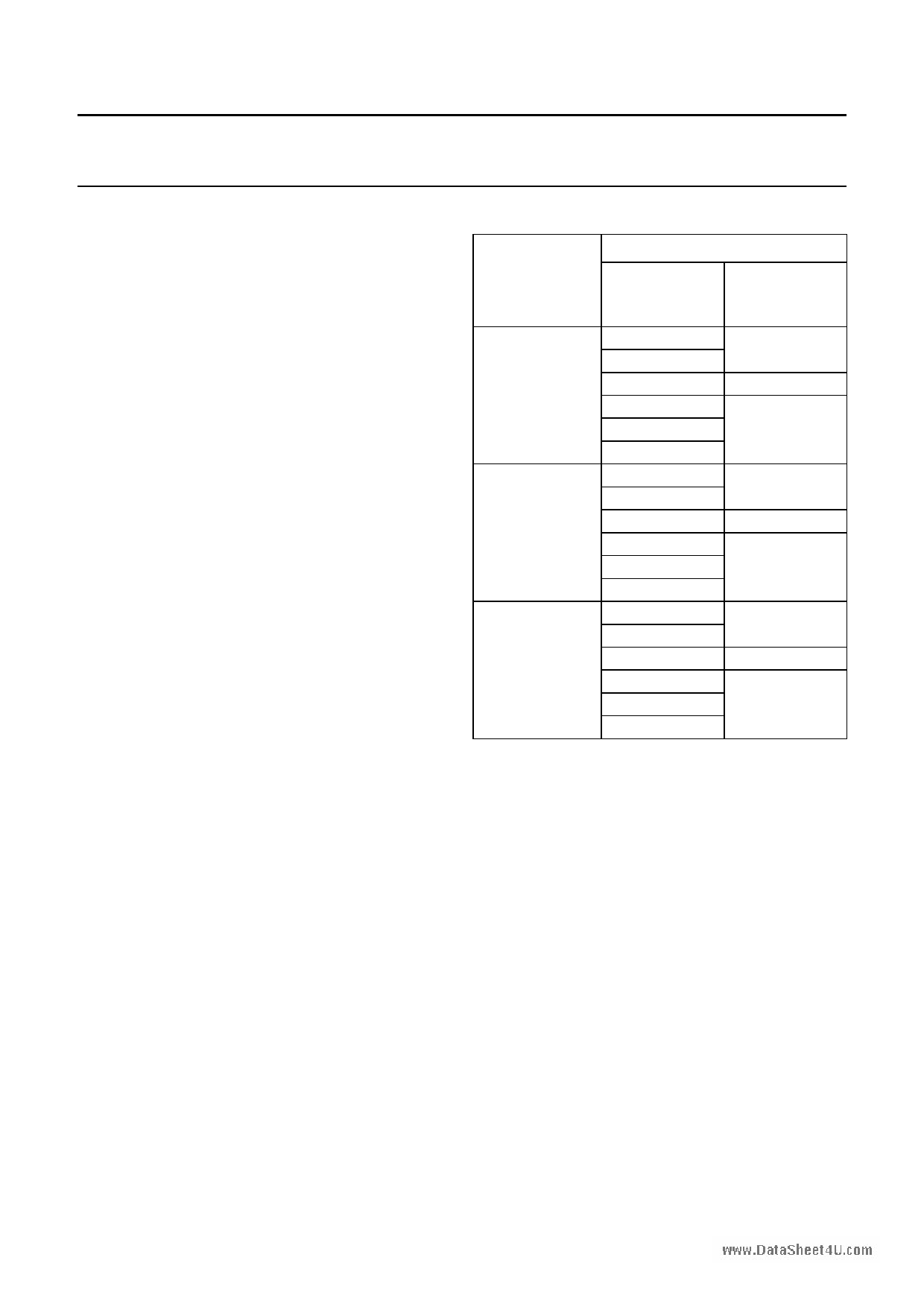

4 QUICK REFERENCE DATA

SYMBOL

PARAMETER

CONDITIONS

Supplies

VDDA1

VDDA2

www.DataSheeVt4DUD.Xcom

DAC supply voltage

ADC supply voltage

crystal oscillator and PLL

supply voltage

VDDI

VDDE

IDDA1

IDDA2

IDDX

IDDI

IDDE

Tamb

digital core supply voltage

digital pad supply voltage

DAC supply current

ADC supply current

crystal oscillator and PLL

supply current

digital core supply current

digital pad supply current

ambient temperature

fs = 48 kHz; power-on

fs = 96 kHz; power-on

fs = 48 kHz; power-down

fs = 96 kHz; power-down

fs = 48 kHz; power-on

fs = 96 kHz; power-on

fs = 48 kHz; power-down

fs = 96 kHz; power-down

fs = 48 kHz; power-on

fs = 96 kHz; power-on

fs = 48 kHz; all on

fs = 96 kHz; all on

fs = 48 kHz; all on

fs = 96 kHz; all on

Digital-to-analog converter; fi = 1 kHz; VDDA1 = 3.0 V

Vo(rms)

output voltage (RMS

value)

∆Vo

(THD+N)/S

output voltage unbalance

total harmonic

distortion-plus-noise to

signal ratio

IEC 60958 input; fs = 48 kHz

at 0 dB

at −20 dB

at −60 dB; A-weighted

IEC 60958 input; fs = 96 kHz

at 0 dB

at −60 dB; A-weighted

S/N

signal-to-noise ratio

IEC 60958 input; code = 0;

A-weighted

fs = 48 kHz

fs = 96 kHz

αcs channel separation

Preliminary specification

UDA1355H

MIN. TYP. MAX. UNIT

2.7 3.0

2.7 3.0

2.7 3.0

3.6 V

3.6 V

3.6 V

2.7 3.0

3.6 V

2.7 3.0

3.6 V

− 4.7 − mA

− 4.7 − mA

− 1.7 − µA

− 1.7 − µA

− 10.2 − mA

− 10.4 − mA

− 0.2 − µA

− 0.2 − µA

− 0.9 − mA

− 1.2 − mA

− 18.2 − mA

− 34.7 − mA

− 0.5 − mA

− 0.7 − mA

−40 −

+85 °C

− 900 − mV

− 0.1 − dB

− −88 − dB

− −75 − dB

− −37 − dB

− −83 − dB

− −37 − dB

− 98 − dB

− 96 − dB

− 100 − dB

2003 Apr 10

5

5 Page

Philips Semiconductors

Stereo audio codec with SPDIF interface

Preliminary specification

UDA1355H

• Set two times 40 bits of channel status bits of the SPDIF

output

• Select one of four SPDIF input sources

• Enable digital mixer inside interpolator

• Control mute and mixer volumes of digital mixer

• Selection of filter mode and settings of treble and bass

www.DataSheet4bUo.ocosmt for the interpolator (DAC) section

• Volume settings of interpolator

• Selection of soft mute via cosine roll-off (only effective in

L3-bus control mode) and bypass of auto mute

• Selection of de-emphasis

• Enable and control of digital mixer inside interpolator.

The readable settings are:

• Mute status of interpolator

• PLL lock and adaptive lock

• Two times 40 bits of channels status bits of the SPDIF

input signal.

7.3 Clock systems

The UDA1355H has two clock systems.

The first system uses an external crystal of 12.288 MHz to

generate the audio related system clocks. Only a crystal

with a frequency of 12.288 MHz is allowed.

The second system is a PLL which locks on the SPDIF or

incoming digital audio signal (e.g. I2S-bus) and recovers

the system clock.

7.3.1 CRYSTAL OSCILLATOR CLOCK SYSTEM

The crystal oscillator and the on-chip PLL and divider

circuit can be used to generate internal and external clock

signals related to standard audio sampling frequencies

(such as 32, 44.1 and 48 kHz including half and double of

these frequencies).

The audio frequencies supported in either microcontroller

mode or static mode are given in Table 3.

Table 3 Output frequencies

BASIC AUDIO

FREQUENCY

32 kHz

44.1 kHz

48 kHz

OUTPUT FREQUENCY

MICRO-

CONTROLLER

MODE

256 × 16 kHz

384 × 16 kHz

256 × 32 kHz

384 × 32 kHz

256 × 64 kHz

384 × 64 kHz

256 × 22.05 kHz

384 × 22.05 kHz

256 × 44.1 kHz

384 × 44.1 kHz

256 × 88.2 kHz

384 × 88.2 kHz

256 × 24 kHz

384 × 24 kHz

256 × 48 kHz

384 × 48 kHz

256 × 96 kHz

384 × 96 kHz

STATIC MODE

256 × 32 kHz

256 × 44.1 kHz

256 × 48 kHz

Remarks:

• If an application mode is selected which does not need

a crystal oscillator, the crystal oscillator cannot be

omitted. The reason is that the interpolator switches to

the crystal clock when an SPDIF input signal is

removed. This switch prevents the noise shaper noise

from moving inside the audio band as the PLL gradually

decreases in frequency.

• If no accurate output frequency is needed, the crystal

can be replaced with a resonator.

• Instead of the crystal, a 12.288 MHz system clock can

be applied to pin XTALIN.

The block diagram of the crystal oscillator and the PLL

circuit is given in Fig.3.

2003 Apr 10

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet UDA1355H.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UDA1355H | Stereo audio codec | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |