|

|

PDF XC5VLX30 Data sheet ( Hoja de datos )

| Número de pieza | XC5VLX30 | |

| Descripción | Platform Flash In-System Programmable Configuration PROMS | |

| Fabricantes | Xilinx | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XC5VLX30 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

<BL Blue>

R

DS123 (v2.9) May 09, 2006

0

Features

• In-System Programmable PROMs for Configuration of

Xilinx FPGAs

• Low-Power Advanced CMOS NOR FLASH Process

• Endurance of 20,000 Program/Erase Cycles

• Operation over Full Industrial Temperature Range

(–40°C to +85°C)

w w w . •D a ItEaEES Sh teanedat r4d U11.4c9.o1/m1532 Boundary-Scan (JTAG)

Support for Programming, Prototyping, and Testing

• JTAG Command Initiation of Standard FPGA

Configuration

• Cascadable for Storing Longer or Multiple Bitstreams

• Dedicated Boundary-Scan (JTAG) I/O Power Supply

(VCCJ)

• I/O Pins Compatible with Voltage Levels Ranging From

1.5V to 3.3V

• Design Support Using the Xilinx Alliance ISE and

Foundation ISE Series Software Packages

Platform Flash In-System

Programmable Configuration

PROMS

Product Specification

• XCF01S/XCF02S/XCF04S

♦ 3.3V supply voltage

♦ Serial FPGA configuration interface (up to 33 MHz)

♦ Available in small-footprint VO20 and VOG20

packages.

• XCF08P/XCF16P/XCF32P

♦ 1.8V supply voltage

♦ Serial or parallel FPGA configuration interface

(up to 33 MHz)

♦ Available in small-footprint VO48, VOG48, FS48,

and FSG48 packages

♦ Design revision technology enables storing and

accessing multiple design revisions for

configuration

♦ Built-in data decompressor compatible with Xilinx

advanced compression technology

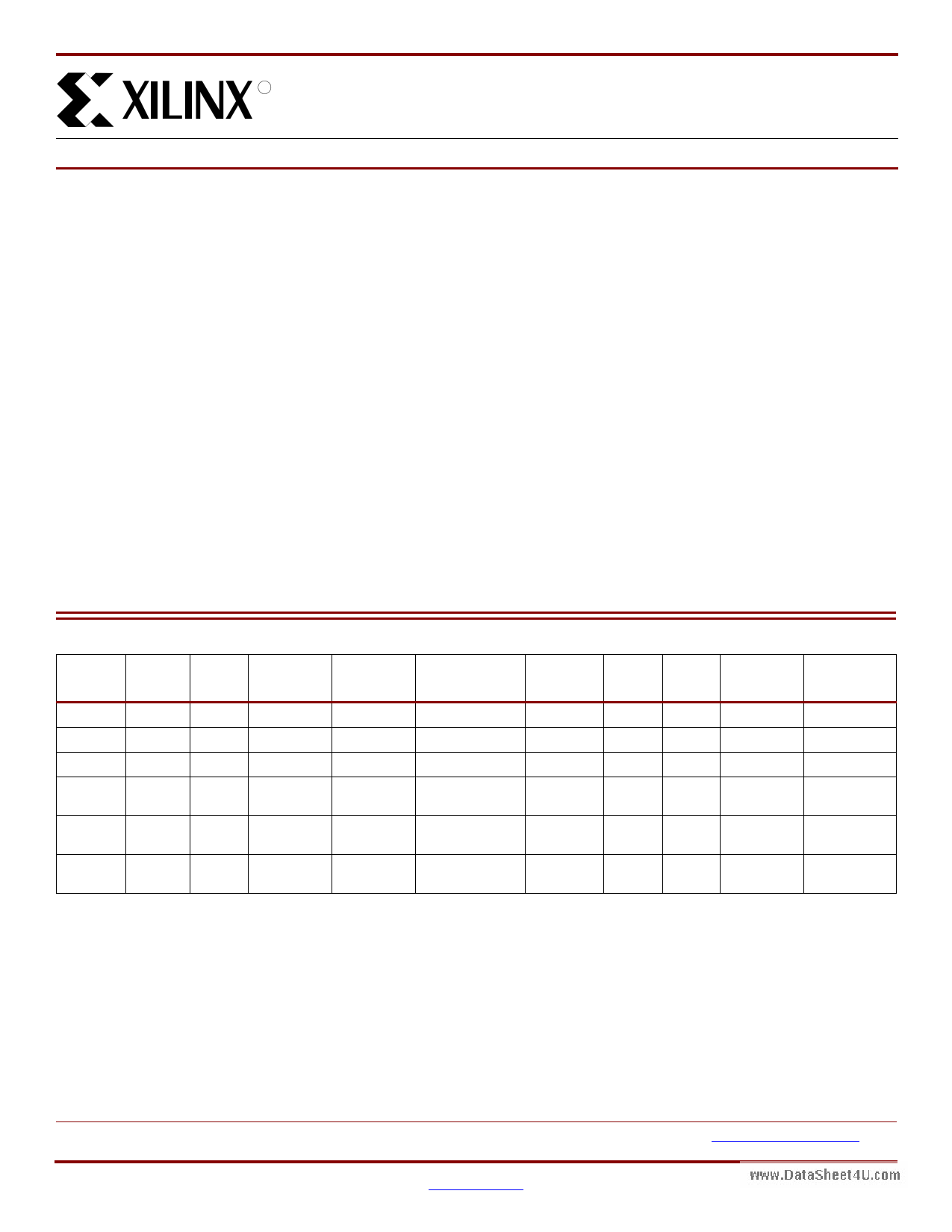

Table 1: Platform Flash PROM Features

Device Density VCCINT VCCO Range VCCJ Range

Packages

XCF01S

XCF02S

XCF04S

XCF08P

1 Mbit

2 Mbit

4 Mbit

8 Mbit

XCF16P 16 Mbit

XCF32P 32 Mbit

3.3V

3.3V

3.3V

1.8V

1.8V

1.8V

1.8V – 3.3V 2.5V – 3.3V

1.8V – 3.3V 2.5V – 3.3V

1.8V – 3.3V 2.5V – 3.3V

1.5V – 3.3V 2.5V – 3.3V

1.5V – 3.3V 2.5V – 3.3V

1.5V – 3.3V 2.5V – 3.3V

VO20/VOG20

VO20/VOG20

VO20/VOG20

VO48/VOG48

FS48/FSG48

VO48/VOG48

FS48/FSG48

VO48/VOG48

FS48/FSG48

Program

In-system

via JTAG

✓

✓

✓

Serial

Config.

Parallel

Config.

Design

Revisioning

Compression

✓

✓

✓

✓ ✓✓ ✓

✓

✓ ✓✓ ✓

✓

✓ ✓✓ ✓

✓

Description

Xilinx introduces the Platform Flash series of in-system

programmable configuration PROMs. Available in 1 to 32

Megabit (Mbit) densities, these PROMs provide an

easy-to-use, cost-effective, and reprogrammable method

for storing large Xilinx FPGA configuration bitstreams. The

Platform Flash PROM series includes both the 3.3V

XCFxxS PROM and the 1.8V XCFxxP PROM. The XCFxxS

version includes 4-Mbit, 2-Mbit, and 1-Mbit PROMs that

support Master Serial and Slave Serial FPGA configuration

modes (Figure 1, page 2). The XCFxxP version includes

32-Mbit, 16-Mbit, and 8-Mbit PROMs that support Master

Serial, Slave Serial, Master SelectMAP, and Slave

SelectMAP FPGA configuration modes (Figure 2, page 2).

A summary of the Platform Flash PROM family members

and supported features is shown in Table 1.

© 2003-2006 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

PowerPC is a trademark of IBM, Inc. All other trademarks are the property of their respective owners. All specifications are subject to change without notice.

DS123 (v2.9) May 09, 2006

www.xilinx.com

1

1 page

R Platform Flash In-System Programmable Configuration PROMS

Reliability and Endurance

Xilinx in-system programmable products provide a

guaranteed endurance level of 20,000 in-system

program/erase cycles and a minimum data retention of 20

years. Each device meets all functional, performance, and

data retention specifications within this endurance limit.

Design Security

The Xilinx in-system programmable Platform Flash PROM

devices incorporate advanced data security features to fully

protect the FPGA programming data against unauthorized

reading via JTAG. The XCFxxP PROMs can also be

w w wpr.ogrDamametd tao pSrevhenteinaedvtert4entUwr.itincg voia mJTAG.

Table 4 and Table 5 show the security settings available for

the XCFxxS PROM and XCFxxP PROM, respectively.

Read Protection

The read protect security bit can be set by the user to

prevent the internal programming pattern from being read or

copied via JTAG. Read protection does not prevent write

operations. For the XCFxxS PROM, the read protect

security bit is set for the entire device, and resetting the read

protect security bit requires erasing the entire device. For

the XCFxxP PROM the read protect security bit can be set

for individual design revisions, and resetting the read

protect bit requires erasing the particular design revision.

Write Protection

The XCFxxP PROM device also allows the user to write

protect (or lock) a particular design revision to prevent

inadvertent erase or program operations. Once set, the

write protect security bit for an individual design revision

must be reset (using the UNLOCK command followed by

ISC_ERASE command) before an erase or program

operation can be performed.

Table 4: XCFxxS Device Data Security Options

Read Protect

Read/Verify

Inhibited

Program

Inhibited

Erase

Inhibited

Reset (default)

Set ✓

Table 5: XCFxxP Design Revision Data Security Options

Read Protect

Reset (default)

Reset (default)

Set

Set

Write Protect

Reset (default)

Set

Reset (default)

Set

Read/Verify

Inhibited

Program Inhibited Erase Inhibited

✓✓

✓

✓✓✓

IEEE 1149.1 Boundary-Scan (JTAG)

The Platform Flash PROM family is compatible with the IEEE

1149.1 boundary-scan standard and the IEEE 1532

in-system configuration standard. A Test Access Port (TAP)

and registers are provided to support all required boundary

scan instructions, as well as many of the optional

instructions specified by IEEE Std. 1149.1. In addition, the

JTAG interface is used to implement in-system programming

(ISP) to facilitate configuration, erasure, and verification

operations on the Platform Flash PROM device. Table 6,

page 6 lists the required and optional boundary-scan

instructions supported in the Platform Flash PROMs. Refer

to the IEEE Std. 1149.1 specification for a complete

description of boundary-scan architecture and the required

and optional instructions.

Caution! The XCFxxP JTAG TAP pause states are not fully compliant with

the JTAG 1149.1 specification. If a temporary pause of a JTAG shift operation is

required, then stop the JTAG TCK clock and maintain the JTAG TAP within the

JTAG Shift-IR or Shift-DR TAP state. Do not transition the XCFxxP JTAG TAP

through the JTAG Pause-IR or Pause-DR TAP state to temporarily pause a

JTAG shift operation.

Instruction Register

The Instruction Register (IR) for the Platform Flash PROM

is connected between TDI and TDO during an instruction

scan sequence. In preparation for an instruction scan

sequence, the instruction register is parallel loaded with a

fixed instruction capture pattern. This pattern is shifted out

onto TDO (LSB first), while an instruction is shifted into the

instruction register from TDI.

XCFxxS Instruction Register (8 bits wide)

The Instruction Register (IR) for the XCFxxS PROM is eight

bits wide and is connected between TDI and TDO during an

instruction scan sequence. The detailed composition of the

instruction capture pattern is illustrated in Table 7, page 6.

The instruction capture pattern shifted out of the XCFxxS

device includes IR[7:0]. IR[7:5] are reserved bits and are set

to a logic 0. The ISC Status field, IR[4], contains logic 1 if

the device is currently in In-System Configuration (ISC)

mode; otherwise, it contains logic 0. The Security field,

IR[3], contains logic 1 if the device has been programmed

with the security option turned on; otherwise, it contains

DS123 (v2.9) May 09, 2006

www.xilinx.com

5

5 Page

R Platform Flash In-System Programmable Configuration PROMS

at a slow default frequency. The FPGA’s bitstream contains

configuration bits which can switch CCLK to a higher

frequency for the remainder of the Master Serial

configuration sequence. The desired CCLK frequency is

selected during bitstream generation.

Connecting the FPGA device to the configuration PROM for

Master Serial Configuration Mode (Figure 6, page 14):

• The DATA output of the PROM(s) drive the DIN input of

the lead FPGA device.

• The Master FPGA CCLK output drives the CLK input(s)

of the PROM(s)

• The CEO output of a PROM drives the CE input of the

next PROM in a daisy chain (if any).

www.DataSheet4U.com

• The OE/RESET pins of all PROMs are connected to

the INIT_B pins of all FPGA devices. This connection

assures that the PROM address counter is reset before

the start of any (re)configuration.

• The PROM CE input can be driven from the DONE pin.

The CE input of the first (or only) PROM can be driven

by the DONE output of all target FPGA devices,

provided that DONE is not permanently grounded. CE

can also be permanently tied Low, but this keeps the

DATA output active and causes an unnecessary ICC

active supply current ("DC Characteristics Over

Operating Conditions," page 26).

• The PROM CF pin is typically connected to the FPGA's

PROG_B (or PROGRAM) input. For the XCFxxP only,

the CF pin is a bidirectional pin. If the XCFxxP CF pin is

not connected to the FPGA's PROG_B (or PROGRAM)

input, then the pin should be tied High.

FPGA Slave Serial Mode

In Slave Serial mode, the FPGA loads the configuration

bitstream in bit-serial form from external memory

synchronized by an externally supplied clock. Upon

power-up or reconfiguration, the FPGA's mode select pins

are used to select the Slave Serial configuration mode.

Slave Serial Mode provides a simple configuration interface.

Only a serial data line, a clock line, and two control lines

(INIT and DONE) are required to configure an FPGA. Data

from the PROM is read out sequentially on a single data line

(DIN), accessed via the PROM's internal address counter

which is incremented on every valid rising edge of CCLK.

The serial bitstream data must be set up at the FPGA’s DIN

input pin a short time before each rising edge of the

externally provided CCLK.

Connecting the FPGA device to the configuration PROM for

Slave Serial Configuration Mode (Figure 7, page 15):

• The DATA output of the PROM(s) drive the DIN input of

the lead FPGA device.

• The PROM CLKOUT (for XCFxxP only) or an external

clock source drives the FPGA's CCLK input.

• The CEO output of a PROM drives the CE input of the

next PROM in a daisy chain (if any).

• The OE/RESET pins of all PROMs are connected to

the INIT_B (or INIT) pins of all FPGA devices. This

connection assures that the PROM address counter is

reset before the start of any (re)configuration.

• The PROM CE input can be driven from the DONE pin.

The CE input of the first (or only) PROM can be driven

by the DONE output of all target FPGA devices,

provided that DONE is not permanently grounded. CE

can also be permanently tied Low, but this keeps the

DATA output active and causes an unnecessary ICC

active supply current ("DC Characteristics Over

Operating Conditions," page 26).

• The PROM CF pin is typically connected to the FPGA's

PROG_B (or PROGRAM) input. For the XCFxxP only,

the CF pin is a bidirectional pin. If the XCFxxP CF pin is

not connected to the FPGA's PROG_B (or PROGRAM)

input, then the pin should be tied High.

Serial Daisy Chain

Multiple FPGAs can be daisy-chained for serial

configuration from a single source. After a particular FPGA

has been configured, the data for the next device is routed

internally to the FPGA’s DOUT pin. Typically the data on the

DOUT pin changes on the falling edge of CCLK, although

for some devices the DOUT pin changes on the rising edge

of CCLK. Consult the respective device data sheets for

detailed information on a particular FPGA device. For

clocking the daisy-chained configuration, either the first

FPGA in the chain can be set to Master Serial, generating

the CCLK, with the remaining devices set to Slave Serial

(Figure 8, page 16), or all the FPGA devices can be set to

Slave Serial and an externally generated clock can be used

to drive the FPGA's configuration interface (Figure 7,

page 15 or Figure 12, page 20).

FPGA Master SelectMAP (Parallel) Mode

(XCFxxP PROM Only)

In Master SelectMAP mode, byte-wide data is written into

the FPGA, typically with a BUSY flag controlling the flow of

data, synchronized by the configuration clock (CCLK)

generated by the FPGA. Upon power-up or reconfiguration,

the FPGA's mode select pins are used to select the Master

SelectMAP configuration mode. The configuration interface

typically requires a parallel data bus, a clock line, and two

control lines (INIT and DONE). In addition, the FPGA’s Chip

Select, Write, and BUSY pins must be correctly controlled to

enable SelectMAP configuration. The configuration data is

read from the PROM byte by byte on pins [D0..D7],

accessed via the PROM's internal address counter which is

incremented on every valid rising edge of CCLK. The

bitstream data must be set up at the FPGA’s [D0..D7] input

pins a short time before each rising edge of the FPGA's

DS123 (v2.9) May 09, 2006

www.xilinx.com

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet XC5VLX30.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XC5VLX30 | Platform Flash In-System Programmable Configuration PROMS | Xilinx |

| XC5VLX30 | Fpga Integrated Circuit | Xilinx |

| XC5VLX30T | Fpga Integrated Circuit | Xilinx |

| XC5VLX330 | Platform Flash In-System Programmable Configuration PROMS | Xilinx |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |