|

|

PDF W65C21S Data sheet ( Hoja de datos )

| Número de pieza | W65C21S | |

| Descripción | Peripheral Interface Adapter | |

| Fabricantes | WDC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de W65C21S (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

The Western Design Center, Inc.

W65C21S Data Sheet

www.DataSheet4U.com

Peripheral Interface Adapter (PIA)

W65C21S

The Western Design Center

W65C21S

1

1 page

The Western Design Center, Inc.

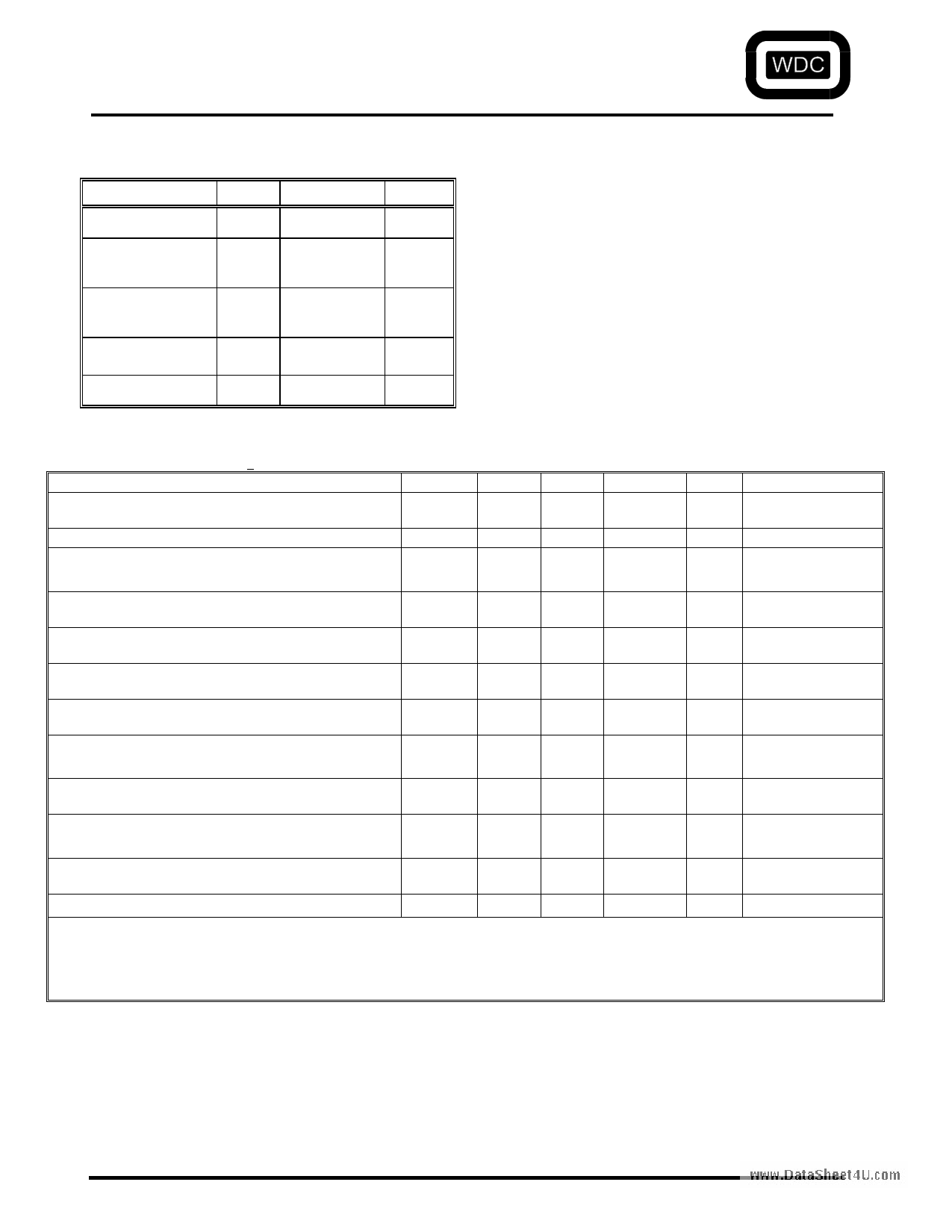

ABSOLUTE MAXIMUM RATINGS*

Parameter

Symbol

Value

Supply Voltage

Input Voltage

VDD

VIN

-0.3 to +7.0

-0.3 to VDD

+0.3

Output Voltage

VOUT

-0.3 to VDD

+0.3

www.DataSheet4OUpeI.nrcadotuimnstgriTalemp. Range

Storage Temperature

TA

TSTG

-40 to +85

-55 to +150

Unit

Vdc

Vdc

Vdc

°C

°C

W65C21S Data Sheet

This device contains input protection against damage due to

high static voltages or electric fields; however, precautions

should be taken to avoid application of voltages higher than

the maximum rating.

Notes:

1. Exceeding these ratings may cause permanent damage,

functional operation under these conditions is not implied.

DC CHARACTERISTICS (VDD = 5.0V + 10%, VSS = 0, TA = -40ºCto +85ºC)

Parameter

Symbol

Input High Voltage

VIH

Input Low Voltage

Input Leakage Current

CA1, CB1, CS0, CS1, CS2B, RESB, RS0, RS1, RWB ,

PHI2

Three-State (Off State), Leakage Current

CB2, D0-D7, PB0-PB7

Input High Current

CA2, PA0-PA7

Input Low Current

CA2, PA0-PA7

Output High Voltage

D0-D7, PA0-PA7, PB0-PB7

Output Low Voltage

CA2, CB2, D0-D7, IRQAB, IRQBB, PA0-PA7, PB0-

PB7

Output High Current (Sourcing)

CB2 (Darlington Drive), PB0-PB7

Output Low Current (Sinking)

CA2, CB2, D0-D7, IRQAB, IRQBB, PA0-PA7, PB0-

PB7

Output Leakage Current (Off State)

IRQAB, IRQBB

Power Dissipation

Notes:

1. All units are direct current (DC) except for capacitance.

2. Negative sign indicates outward current flow, positive indicates inward flow.

3. Typical values are shown for VDD = 5.0V and TA = 25○ C

4. All production test loads use test machine capacitance (~30pF) only.

5. Capacitance of all pins is estimated 5.0pF at a 1MHz sample.

VIL

IIN

ITSI

IIH

IIL

VOH

VOL

tCH

tOL

tOFF

IDD

Min2

2.0

-0.3

--

--

-100

--

2.4

--

-3.0

3.2

--

--

Typ.2,3

--

--

--

--

--

--

--

--

--

--

< .1

100

Max2

VDD +0.3

0.8

±10.0

±10.0

--

-500

--

0.4

-20.0

--

10.0

500

Unit1

V

V

nA

nA

µA

uA

V

V

mA

mA

nA

uA

Test Conditions

VDD = 5.5V

VDD = 4.5V

VIN = .4V to 2.4V, VDD

= 5.5V

VIN = 0.4V to 2.4V,

VDD = 5.5V

VIH = 2.4V,

VDD

= 4.5V

VIL = 0.4V,

VDD =

5.5V

IOH = -200µA, VDD

= 4.5V

IOL = 3.2mA,

= 4.5V

VOH = 1.5V,

= 4.5V

VDD

VDD

VOL = 0.4V,

VDD

= 4.5V

VOH = 2.4V

VDD = 5.5V

The Western Design Center

W65C21S

5

5 Page

The Western Design Center, Inc.

IRQB1, IRQB2) are normally interrogated by the

microprocessor during the interrupt service routine to

determine the source of an active interrupt. These two

interrupt lines drive the interrupt input (IRQB or NMIB) of

the microprocessor.

DATA BUS BUFFERS (DBB)

The Data Bus Buffers are 8-bit bidirectional buffers used for

data exchange, on the D0-D7 Data Bus, between the

microprocessor and the PIA. These buffers are tri-state and

are capable of driving a two TTL load (when operating in an

output mode.

www.DataSheet4U.com

DATA DIRECTION REGISTERS (DDRA, DDRB)

The Data Direction Registers (DDRA, DDRB) allow the

processor to program each line in the 8-bit Peripheral I/O

port to be either an input or an output. Each bit in DDRA

controls the corresponding line in the Peripheral A port and

each bit in DDRB controls the corresponding line in the

Peripheral B port. Writing a “0” in a bit position in the Data

Direction Register causes the corresponding Peripheral I/O

line to act as in input; a “1” results in the line being an

output.

Bit 2 (DDRA, DDRB) in each Control Register (CRA and

CRB) controls the accessing to the Data Direction Register or

the Peripheral interface. If bit 2 is a “1”, a Peripheral Output

register (ORA, ORB) is selected, and if bit 2 is a “0”, a Data

Direction Register (DDRA, DDRB) is selected. The Data

Direction Register Access Control bit, together with the

Register Select lines (RS0, RS1) selects the various internal

registers as shown in Table 2.

In order to write data into DDRA, ORA, DDRB or ORB

registers, bit 2 in the proper Control Register must first be

set. The desired register may then be accessed with the

address determined by the address interconnect technique

used.

DATA INPUT REGISTER (DIR)

During a Write data operation, the microprocessor writes data

into the W65C21S by placing data on the Data Bus. This

data is then latched into the Data Input Register by the Phase

Two (PHI2) clock. Once in the DIR, this data byte is

transferred into one of six internal registers. This data

transfer occurs after the trailing edge of the PHI2 clock pulse

that latched the data into the DIR. This timing delay

guarantees the data on the peripheral output lines (PA or PB)

will make a smooth transition from low to high or high to

low, and the output voltage will remain stable when there is

to be no change in polarity.

INTERRUPT INPUT/PERIPHERAL CONTROL LINES

(CA1, CA2, CB1, CB2)

The four interrupt input/peripheral control lines provide a

number of special control functions. These lines greatly

enhance the power of the two general purpose interface ports

(PA0-PA7, PB0-PB7). Figure 5 summarizes the operation of

these control lines.

W65C21S Data Sheet

CA1 is an interrupt input only. An active transition of the

signal on this input will set bit 7 of the Control Register A to

a logic 1. The active transition can be programmed by

setting a “0” in bit 1 of the CRA if the interrupt flag (bit7 of

CRA) is to be set on a negative transition of the CA1 signal

or a “1” if it is to be set on a positive transition

NOTE:

A negative transition is defined as a transition from a high to

a low and a positive transition is defined as a transition from

a low to a high voltage.

CA2 can act as a totally independent interrupt or as a

peripheral control output. As an input (CRA, bit 5=0) it acts

to set the interrupt flag, bit 6 of CRA, to a logic on 1 on the

active transition selected by bit 4 of CRA.

These control register bits and interrupt inputs serve the same

basic function as that described above for CA1. The input

signal sets the interrupt flag which serves as the link between

the peripheral device and the processor interrupt structure.

The interrupt disable bits allows the processor to exercise

control over the system interrupt.

In the output mode (CRA, bit 5=1), CA2 can operate

independently to generate a simple pulse each time the

microprocessor is selected by setting CRA bit 4 to a 0 and

CRA bit 3 to a 1. This pulse output can be used to control

the counters, shift registers, etc., which make sequential data

available on the Peripheral input lines.

A second output mode allows CA2 to be used in conjunction

with CA1 to “handshake” between the processor and the

peripheral device. On the A side, this technique allows

positive control of data transfers from the peripheral device

into the microprocessor. The CA1 input signals the

processor that data is available by interrupting the processor.

The processor reads the data and sets CA2 low. This signals

the peripheral device that it can make new data available.

The final output mode can be selected by setting bit 4 of

CRA to a 1. In this mode, CA2 is a simple peripheral control

output that can be set high or low by setting bit 3 of CRA to a

1 or a 0 respectively.

CB1 operates as an interrupt input only in the same manner

as CA1. Bit 7 of CRB is set by the active transition selected

by bit 0 of CRB. Likewise, the CB2 input mode operates

exactly the same as the CA2 input modes. The CB2 output

modes, CRB bit 5=1, differ somewhat from those of CA2.

The pulse output occurs when the processor writes data into

the Peripheral B Output Register. Also, the “handshaking”

operates on data transfers from the processor into the

peripheral device.

INTERRUPT REQUEST (IRQAB, IRQBB)

The active low Interrupt Request lines (IRQAB and IRQBB)

act to interrupt the microprocessor either directly or through

external interrupt priority circuitry. These lines are open

drain and are capable of sinking 3.2 milliamps from an

external source. This permits all interrupt request lines to be

tied together in a wired OR configuration. The A and B in

the titles of these lines correspond to the peripheral port B so

The Western Design Center

W65C21S

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet W65C21S.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| W65C21S | Peripheral Interface Adapter | WDC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |