|

|

PDF HYM71V16635BT8 Data sheet ( Hoja de datos )

| Número de pieza | HYM71V16635BT8 | |

| Descripción | PC133 SDRAM Unbuffered DIMM | |

| Fabricantes | Hynix Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HYM71V16635BT8 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

DESCRIPTION

16Mx64bits

PC133 SDRAM Unbuffered DIMM

based on 16Mx8 SDRAM with LVTTL, 4 banks & 4K Refresh

HYM71V16635BT8 Series

Preliminary

The Hynix HYM71V16635BT8 Series are 16Mx64bits Synchronous DRAM Modules. The modules are composed of eight 16Mx8bits

CMOS Synchronous DRAMs in 400mil 54pin TSOP-II package, one 2Kbit EEPROM in 8pin TSSOP package on a 168pin glass-epoxy

printed circuit board. One 0.22uF and one 0.0022uF decoupling capacitors per each SDRAM are mounted on the PCB.

The Hynix HYM71V16635BT8 Series are Dual In-line Memory Modules suitable for easy interchange and addition of 128Mbytes

memory. The Hynix HYM71V16635BT8 Series are fully synchronous operation referenced to the positive edge of the clock . All inputs

and outputs are synchronized with the rising edge of the clock input. The data paths are internally pipelined to achieve very high band-

width.

FEATURES

• PC133/PC100MHz support

• 168pin SDRAM Unbuffered DIMM

• Serial Presence Detect with EEPROM

• SDRAM internal banks : four banks

• Module bank : one physical bank

• Auto refresh and self refresh

• 1.15” (29.21mm) Height PCB with single sided com- • 4096 refresh cycles / 64ms

ponents

• Programmable Burst Length and Burst Type

• Single 3.3±0.3V power supply

- 1, 2, 4 or 8 or Full page for Sequential Burst

• All device pins are compatible with LVTTL interface

- 1, 2, 4 or 8 for Interleave Burst

• Data mask function by DQM

• Programmable CAS Latency ; 2, 3 Clocks

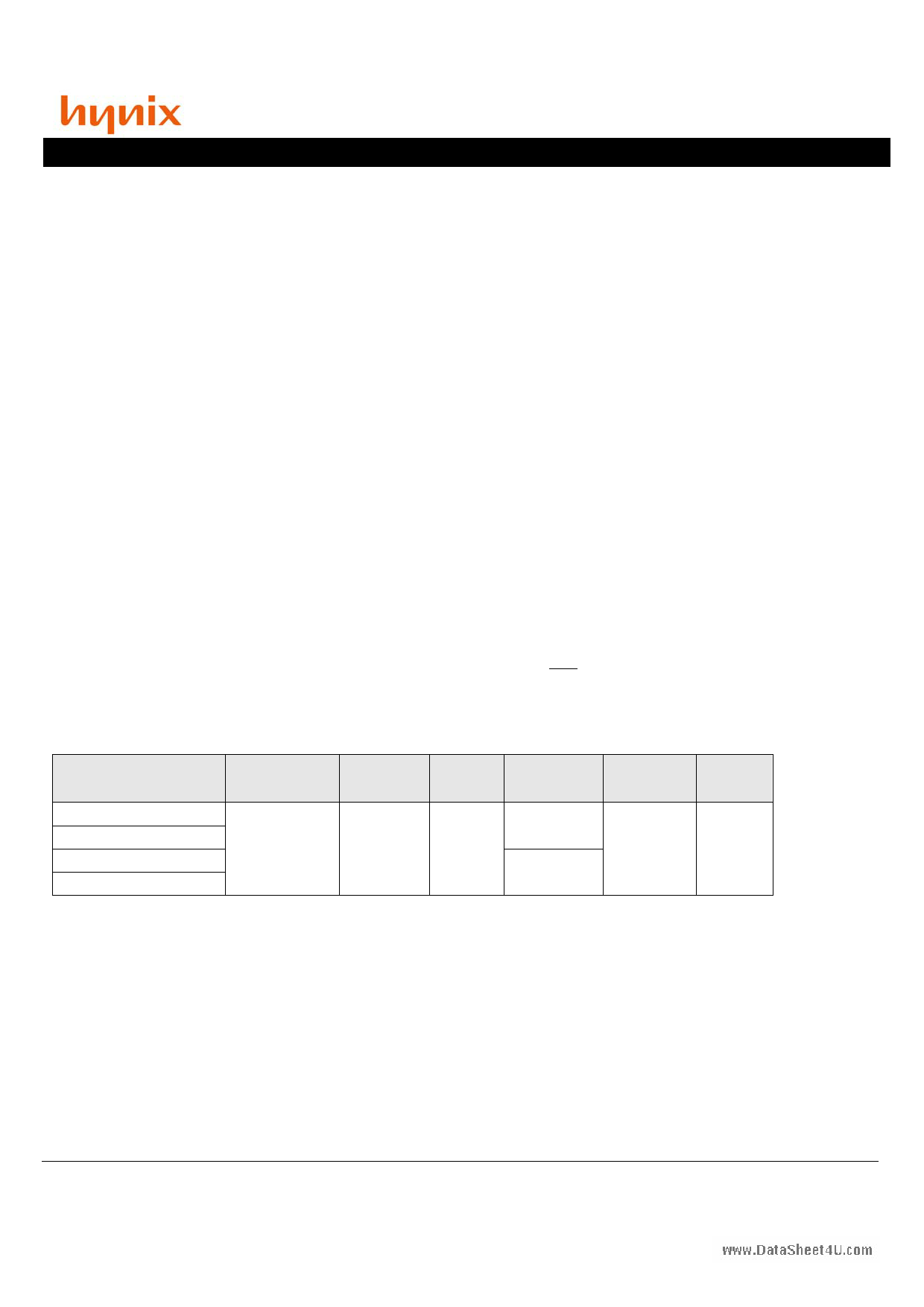

ORDERING INFORMATION

Part No.

HYM71V16635BT8-K

HYM71V16635BT8-H

HYM71V16635BLT8-K

HYM71V16635BLT8-H

Clock

Frequency

Internal

Bank

133MHz

4 Banks

Ref.

4K

Power

Normal

Low Power

SDRAM

Package

Plating

TSOP-II

Gold

This document is a general product description and is subject to change without notice. Hynix Semiconductor Inc. does not assume any responsibility for

use of circuits described. No patent licenses are implied.

Rev. 0.1/Nov. 01

2

1 page

www.DataSheet4U.com

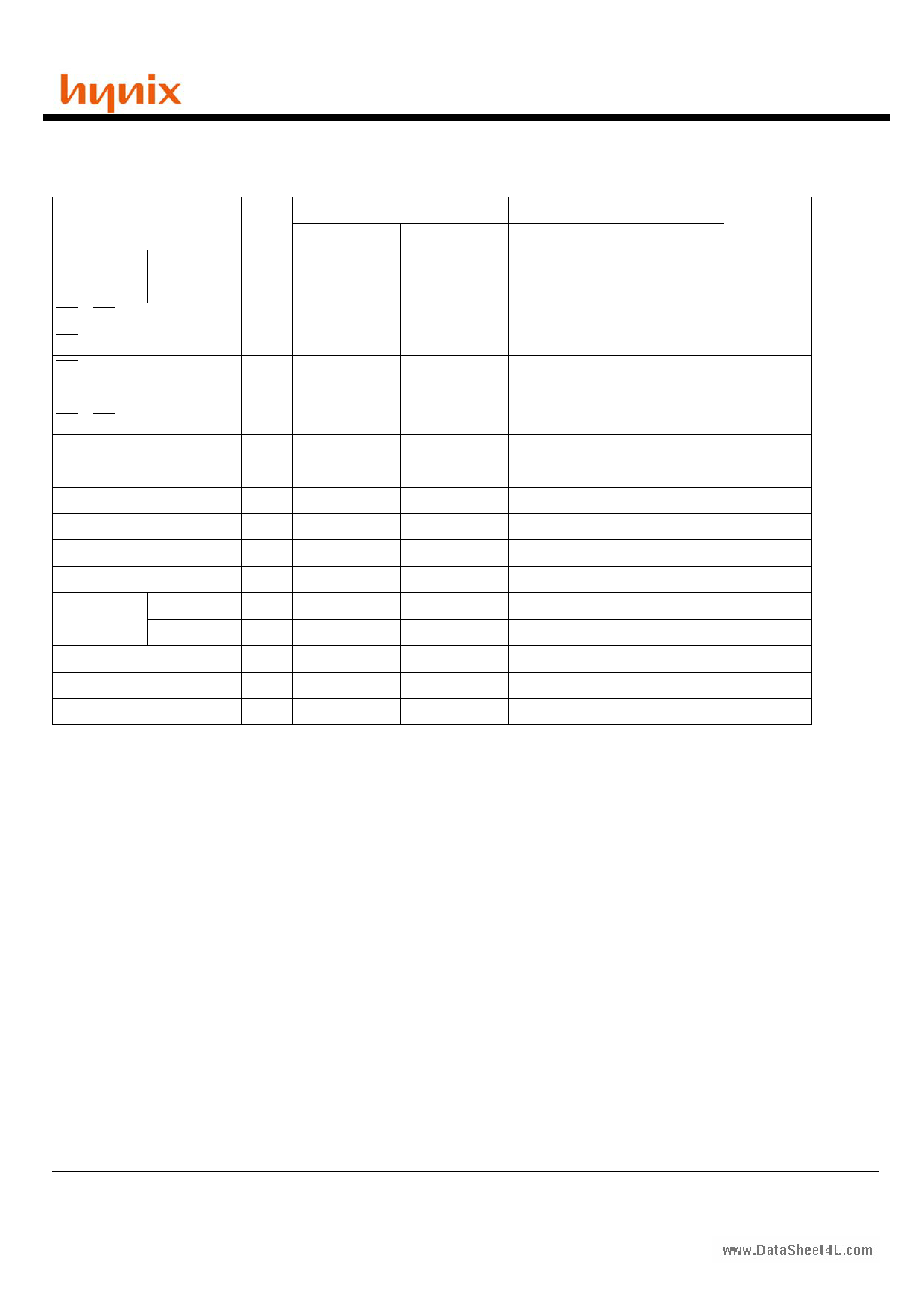

SERIAL PRESENCE DETECT

PC133 SDRAM Unbuffered DIMM

HYM71V16635BT8 Series

BYTE

NUMBER

BYTE0

BYTE1

BYTE2

BYTE3

BYTE4

BYTE5

BYTE6

BYTE7

BYTE8

BYTE9

BYTE10

BYTE11

BYTE12

BYTE13

BYTE14

BYTE15

BYTE16

BYTE17

BYTE18

BYTE19

BYTE20

BYTE21

BYTE22

BYTE23

BYTE24

BYTE25

BYTE26

BYTE27

BYTE28

BYTE29

BYTE30

BYTE31

BYTE32

BYTE33

BYTE34

BYTE35

BYTE36

~61

BYTE62

BYTE63

BYTE64

BYTE65

~71

BYTE72

FUNCTION

DESCRIPTION

# of Bytes Written into Serial Memory at Module

Manufacturer

Total # of Bytes of SPD Memory Device

Fundamental Memory Type

# of Row Addresses on This Assembly

# of Column Addresses on This Assembly

# of Module Banks on This Assembly

Data Width of This Assembly

Data Width of This Assembly (Continued)

Voltage Interface Standard of This Assembly

SDRAM Cycle Time @/CAS Latency=3

Access Time from Clock @/CAS Latency=3

DIMM Configuration Type

Refresh Rate/Type

Primary SDRAM Width

Error Checking SDRAM Width

Minimum Clock Delay Back to Back Random Column

Address

Burst Lenth Supported

# of Banks on Each SDRAM Device

SDRAM Device Attributes, /CAS Lataency

SDRAM Device Attributes, /CS Lataency

SDRAM Device Attributes, /WE Lataency

SDRAM Module Attributes

SDRAM Device Attributes, General

SDRAM Cycle Time @/CAS Latency=2

Access Time from Clock @/CAS Latency=2

SDRAM Cycle Time @/CAS Latency=1

Access Time from Clock @/CAS Latency=1

Minimum Row Precharge Time (tRP)

Minimum Row Active to Row Active Delay (tRRD)

Minimum /RAS to /CAS Delay (tRCD)

Minimum /RAS Pulse Width (tRAS)

Module Bank Density

Command and Address Signal Input Setup Time

Command and Address Signal Input Hold Time

Data Signal Input Setup Time

Data Signal Input Hold Time

Superset Information (may be used in future)

SPD Revision

Checksum for Byte 0~62

Manufacturer JEDEC ID Code

....Manufacturer JEDEC ID Code

Manufacturing Location

FUNCTION

-K -H

128 Bytes

256 Bytes

SDRAM

12

10

1 Bank

64 Bits

-

LVTTL

7.5ns

7.5ns

5.4ns

5.4ns

None

15.625us

/ Self Refresh Supported

x8

None

tCCD = 1 CLK

1,2,4,8,Full Page

4 Banks

/CAS Latency=2,3

/CS Latency=0

/WE Latency=0

Neither Buffered nor Registered

+/- 10% voltage tolerence, Burst Read

Single Bit Write, Precharge All, Auto

Precharge, Early RAS Precharge

7.5s 10ns

5.4ns

6ns

--

--

15ns

20ns

15ns

15ns

15ns

20ns

45ns

45ns

128MB

1.5ns

1.5ns

0.8ns

0.8ns

1.5ns

1.5ns

0.8ns

0.8ns

-

Intel SPD 1.2B

-

Hynix JEDED ID

Unused

HSI (Korea Area)

HSA (United States Area)

HSE (Europe Area)

HSJ (Japan Area)

HSS(Singapore)

ASIA Area

Rev. 0.1/Nov. 01

VALUE

-K -H

80h

08h

04h

0Ch

0Ah

01h

40h

00h

01h

75h 75h

54h 54h

00h

80h

08h

00h

01h

8Fh

04h

06h

01h

01h

00h

0Eh

75h A0h

54h 60h

00h 00h

00h 00h

0Fh 14h

0Fh 0Fh

0Fh 14h

2Dh 2Dh

20h

15h 15h

08h 08h

15h 15h

08h 08h

00h

12h

6Eh AFh

ADh

FFh

0*h

1*h

2*h

3*h

4*h

5*h

NOTE

1

2

3, 8

11

6

5 Page

www.DataSheet4U.com

AC CHARACTERISTICS II

Parameter

Symbol

RAS Cycle Time

Operation

Auto Refresh

tRC

tRRC

RAS to CAS Delay

tRCD

RAS Active Time

tRAS

RAS Precharge Time

tRP

RAS to RAS Bank Active Delay

tRRD

CAS to CAS Delay

tCCD

Write Command to Data-In Delay

tWTL

Data-In to Precharge Command

tDPL

Data-In to Active Command

tDAL

DQM to Data-Out Hi-Z

tDQZ

DQM to Data-In Mask

tDQM

MRS to New Command

tMRD

Precharge to Data CAS Latency = 3 tPROZ3

Output Hi-Z

CAS Latency = 2 tPROZ2

Power Down Exit Time

tPDE

Self Refresh Exit Time

tSRE

Refresh Time

tREF

-K

Min

60

60

15

45

15

15

1

0

2

4

2

0

2

3

2

1

1

-

Note :

1. A new command can be given tRRC after self refresh exit

Max

-

-

-

100K

-

-

-

-

-

-

-

-

-

-

-

-

-

64

PC133 SDRAM Unbuffered DIMM

HYM71V16635BT8 Series

-H

Min Max

65 -

65 -

20 -

45 100K

20 -

15 -

1-

0-

2-

5-

2-

0-

2-

3-

2-

1-

1-

- 64

Unit Note

ns

ns

ns

ns

ns

ns

CLK

CLK

CLK

CLK

CLK

CLK

CLK

CLK

CLK

CLK

CLK

ms

1

Rev. 0.1/Nov. 01

12

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet HYM71V16635BT8.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HYM71V16635BT6 | PC133 SDRAM Unbuffered DIMM | Hynix Semiconductor |

| HYM71V16635BT8 | PC133 SDRAM Unbuffered DIMM | Hynix Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |