|

|

PDF LC898093 Data sheet ( Hoja de datos )

| Número de pieza | LC898093 | |

| Descripción | Write CD-R/RW Encoder/Decoder IC | |

| Fabricantes | Sanyo Semicon Device | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de LC898093 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Ordering number : ENN*6495

CMOS IC

LC898093

40× Playback/12× Write CD-R/RW Encoder/Decoder IC

with Built-in ATAPI Interface

Preliminary

Functions

• CD-ROM decoder/encoder functions

• CD decoder/encoder functions

• Pit and wobble CLV servo

• CAV audio functions

• ATAPI interface (include the register block)

• Subcode encoder/decoder functions

• ATIP demodulator/ATIP decoder

• Write strategy function (CD-R/RW)

Features

• ECC and EDC correction/addition (decoding/encoding)

for CD-ROM data.

• ECC error correction/addition (decoding/encoding) for

subcode data

• Servo control implemented in a digital servo system

(decoding/encoding)

• CLV servo control using ATIP data (encoding)

• ATIP decoding function and CRC check function

(decoding/encoding)

• CIRC code generation and addition and EFM

modulation (encoding)

• CAV audio functions

• Provides high-precision CD-R/RW write strategy signal

output

• Built-in ATAPI interface (with Ultra DMA 33 support)

• Supports 40× decoding and 12× encoding.

Clock frequency: 33.8688 MHz

• Transfer rates: Up to 16.6 MB/s (when 32× IORDY

used), up to 33 MB/s when Ultra DMA used. These

values apply when 16-bit 45 ns EDO DRAM is used.

• From 1 to 64 Mbits of buffer RAM can be used. (16-bit

data bus EDO DRAM)

• The user can freely set up the CD main channel, C2 flag,

and subcode areas in buffer RAM.

• Batch transfer function (Function for transferring the CD

main channel, C2 flag, subcode, and other data in a

single operation)

• Multi-transfer function (Function for automatically

transferring multiple block to the host in a single

operation)

• CAV audio functions

• Supports Ultra DMA modes 0, 1, and 2.

Package Dimensions

unit: mm

3210-SQFP208

156

157

[LC898093]

30.6

28.0

105

104

208

1

(1.25)

(0.5)

53

0.2 52

0.15

“BURN-Proof” stands for Proof against Buffer Under RuN

error, not for proof against burning.

“BURN-Proof” is a trademark of SANYO Electric Co., Ltd.

SANYO: SQFP208

Any and all SANYO products described or contained herein do not have specifications that can handle

applications that require extremely high levels of reliability, such as life-support systems, aircraft’s

control systems, or other applications whose failure can be reasonably expected to result in serious

physical and/or material damage. Consult with your SANYO representative nearest you before using

any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that

exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other

parameters) listed in products specifications of any and all SANYO products described or contained

herein.

SANYO Electric Co.,Ltd. Semiconductor Company

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

83100RM (OT) No. 6495-1/14

1 page

www.DataSheet4U.com

LC898093

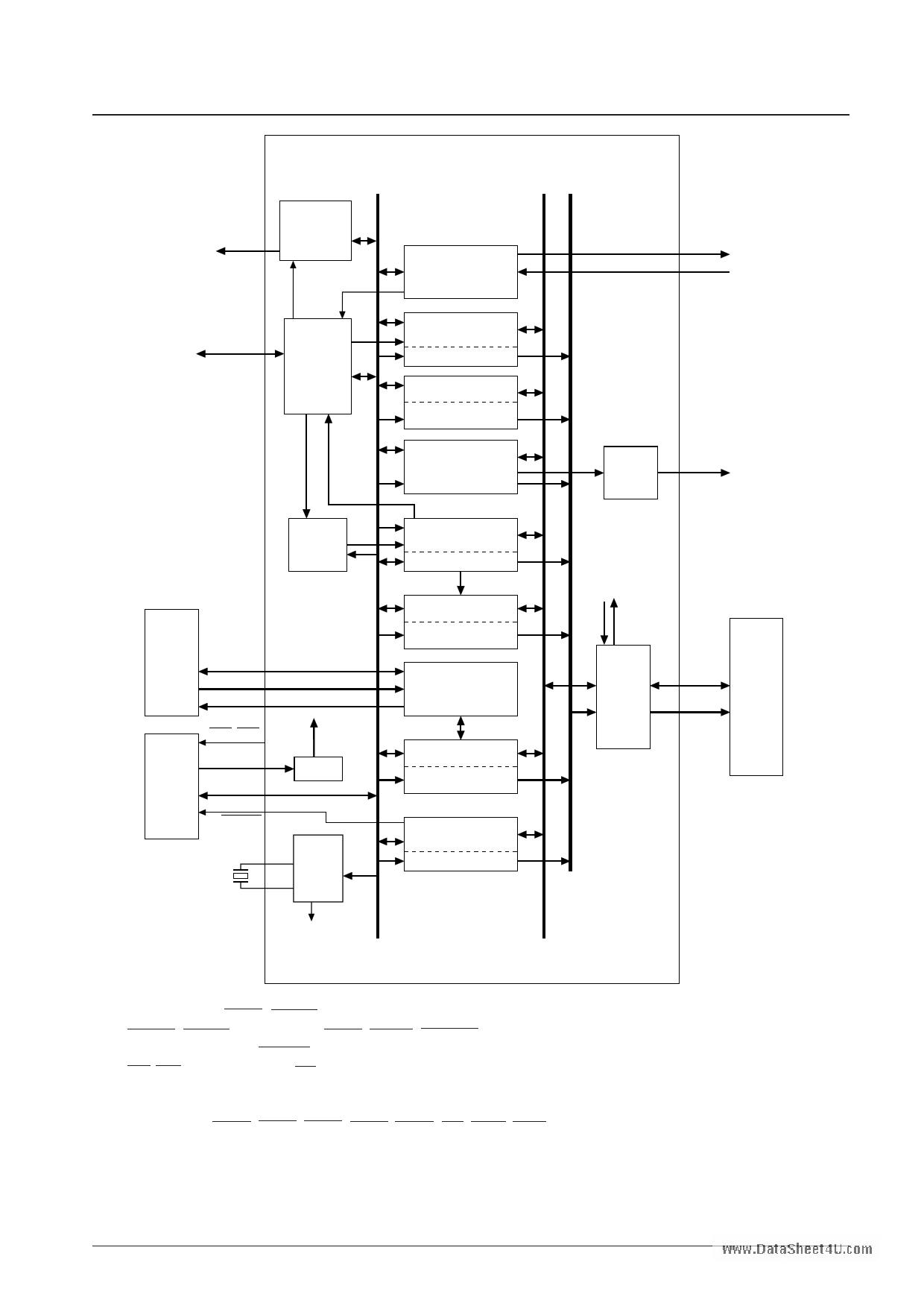

Block Diagram

Data bus[0:7]

LC898093

RAM

Data bus[0:15] Address bus[0:21]

Write Strategy

&

*12 Link-position

ATIPSYNC

ATIP/CLV servo

*11

*10

*1 Digital Servo

&

CIRC EnDec

Sub-code I/F

de-interleve/interleve

Address generator

Sub-code ECC

Address generator

CAV-Audio

DAC *13

CD-DSP I/F

& SYNC

Detector

HOST

*3

*4

*5

INT0, INT1

Micro

controller

*6

*7

ZSWAIT

XTALCK0

XTAL0

Each Block

Register

R0-R255

decoder

PLL

&

Clock

generator

Each Block

De-scramble &

Buffering

Address generator

ECC & EDC

Address generator

IDE I/F Block

based HISIDE

Data output input I/F

Address generator

Microcontroller

RAM access

Address generator

Each Block

Bus control

signal

Bus

Arbiter

&

DRAM

controller

*8

*9

External

Buffer

DRAM

*1 DSLB (pin96) to SUBSYNC (pin145), SHOCK (pin147) to PCK2 (pin155)

*3 DD0 to DD15, DASP, PDIAG

*4 CS1FX, CS3FX, DA0 to DA2, DIOR, DIOW, DMACK

*5 DMARQ, HINTRQ, IOCS16, IORDY

*6 RD, WR, SUA0 to SUA7, CS

*7 D0 to D7

*8 IO0 to IO15

*9 RA0 to RA9, RAS0, RAS1, RAS2, CAS0, CAS1, OE, UWE, LWE

*10 WOBBLE

*11 ATIPSYNC, BIDATA, BICLK

*12 WRITE, SSP2/1, RAPC, WAPC, H11T0, LDH, ATEST3, ATEST1, WDAT, NWDAT, EFMG

*13 LOUT, ROUT

**1 HISIDE (WD25C32) is made by WESTERN DIGITAL.

A13194

No. 6495-5/14

5 Page

www.DataSheet4U.com

LC898093

IORDY (output)

Indicates that the drive is ready to respond. Used during data transfers.

This signal will be low when the drive is not ready.

PDIAG (input/output)

Signal asserted by drive 1 to indicate to drive 0 that diagnostics have completed.

HRST (input)

Reset signal from the host. The IDE interface is reset by a low-level input to this pin.

<Microcontroller Interface Pins>

CS (input)

Chip select signal from the microcontroller. The microcontroller interface is active when this pin is low.

RD, WR (input)

Connect the microcontroller read and write lines to these inputs.

SWAIT (input)

Wait signal output to the microcontroller. When accessing buffer RAM, the microcontroller must wait if this pin is

low.

SUA0 to SUA7 (input)

Internal register address lines

D0 to D7 (input/output)

Microcontroller data bus. These pins have built-in pull-up resistors.

INT0, INT1 (output)

Interrupt request signals output to the microcontroller. INT1 can be set to output the ATAPI interrupt by setting

INT1EN (Conf-R11 bit 7)

These are open drain outputs with built-in 80 kΩ (at room temperature, 5 V) pull-up resistors.

<Buffer RAM Pins>

I/O0 to I/O15 (input/output)

Buffer RAM data bus. These pins have built-in pull-up resistors.

RA0 to RA9 (output)

Buffer RAM address lines.

RAS0, RAS1, RAS2 (output)

Buffer DRAM RAS outputs. Normally, RAS0 is used. However, if two 16-Mbit DRAMs are used, connect the RAS0

and RAS1 lines to the RAS pins on the DRAMs. If four 16-Mbit DRAMs are used, connect the RAS0, RAS1, RAS2,

and LWE lines to the RAS pins on the DRAMs.

CAS0, CAS1 (output)

Buffer DRAM CAS outputs. Normally, CAS0 is used. However, if two 16-Mbit DRAMs are used, connect the CAS0

output to the CAS pins on the DRAMs. If 2-CAS type DRAMs are used, connect CAS0 to UCAS and CAS1 to

LCAS.

OE (output)

Buffer RAM read output.

UWE, LWE (output)

Buffer RAM write outputs. Connect these to the corresponding pins. If 2-CAS type DRAMs are used, UWE must be

connected. (Leave LWE open.)

1. Analog Interface Pins

RREC (input)

Optical discrimination input.

FE (input)

Focus error signal input.

TE (input)

Tracking error signal input.

VREF (input)

Input for the servo system reference voltage.

No. 6495-11/14

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet LC898093.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LC898093 | Write CD-R/RW Encoder/Decoder IC | Sanyo Semicon Device |

| LC898094 | LC898094 | Sanyo |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |