|

|

PDF Z9960 Data sheet ( Hoja de datos )

| Número de pieza | Z9960 | |

| Descripción | 200 MHz Multi-Output Zero Delay Buffer | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de Z9960 (archivo pdf) en la parte inferior de esta página. Total 7 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Z9960

2.5V/3.3V, 200 MHz Multi-Output Zero Delay Buffer

Features

• 2.5V or 3.3V operation

• Output frequency up to 200 MHz

• Supports PowerPC, and Pentium® processors

• 21 clock outputs: drive up to 42 clock lines

• LVPECL or LVCMOS/LVTTL clock input

• Output-to-output skew < 150 ps

• Split 2.5V/3.3V outputs

• Spread spectrum compatible

• Glitch-free output clocks transitioning

• Output disable control

• Pin-compatible with MPC9600

• Industrial temperature range: –40°C to +85°C

• 48-pin LQFP package

Block Diagram

Table 1. Frequency Table[1]

SS

EE

LL

A QA B

0 VCO/2 0

1 VCO/4 1

QB

VCO/2

VCO/4

S

E

L

C

0

1

QC

VCO/2

VCO/4

F

B

_

S

E

L

0

1

FB_OUT

VCO/8

VCO/12

Pin Configuration

REF_SEL

TCLK

PECL_CLK

PECL_CLK#

FB_IN

SELA

SELB

AVDD

PLL

0

1

REF

FB

0

1

/2

/4

/8

/12

A

0

1

DQ

B

0

1

DQ

SELC

C

0

1

DQ

OE#

FB

0

1

DQ

0

1

2

3

4

5

6

0

1

2

3

4

5

6

0

1

2

3

4

5

6

FB_OUT

VSS

TCLK

PECL_CLK

PECL_CLK#

VDD

REF_SEL

FB_SEL

AVDD

SELA

SELB

SELC

VSSC

48 47 46 45 44 43 42 41 40 39 38 37

1 36

2 35

3 34

4 33

5

6

Z9960

32

31

7 30

8 29

9 28

10 27

11 26

12 25

13 14 15 16 17 18 19 20 21 22 23 24

VSSA

FB_OUT

QB0

QB1

VDDB

QB2

QB3

VSSB

QB4

QB5

QB6

VDDB

FB_SEL

Note:

1. Input frequency range: 16 MHz to 33 MHz (FB_SEL = 1), or 25 MHz to 50 MHz (FB_SEL = 0).

Cypress Semiconductor Corporation • 3901 North First Street • San Jose, CA 95134 • 408-943-2600

Document #: 38-07087 Rev. *C

Revised May 03, 2004

1 page

www.DataSheet4U.com

Z9960

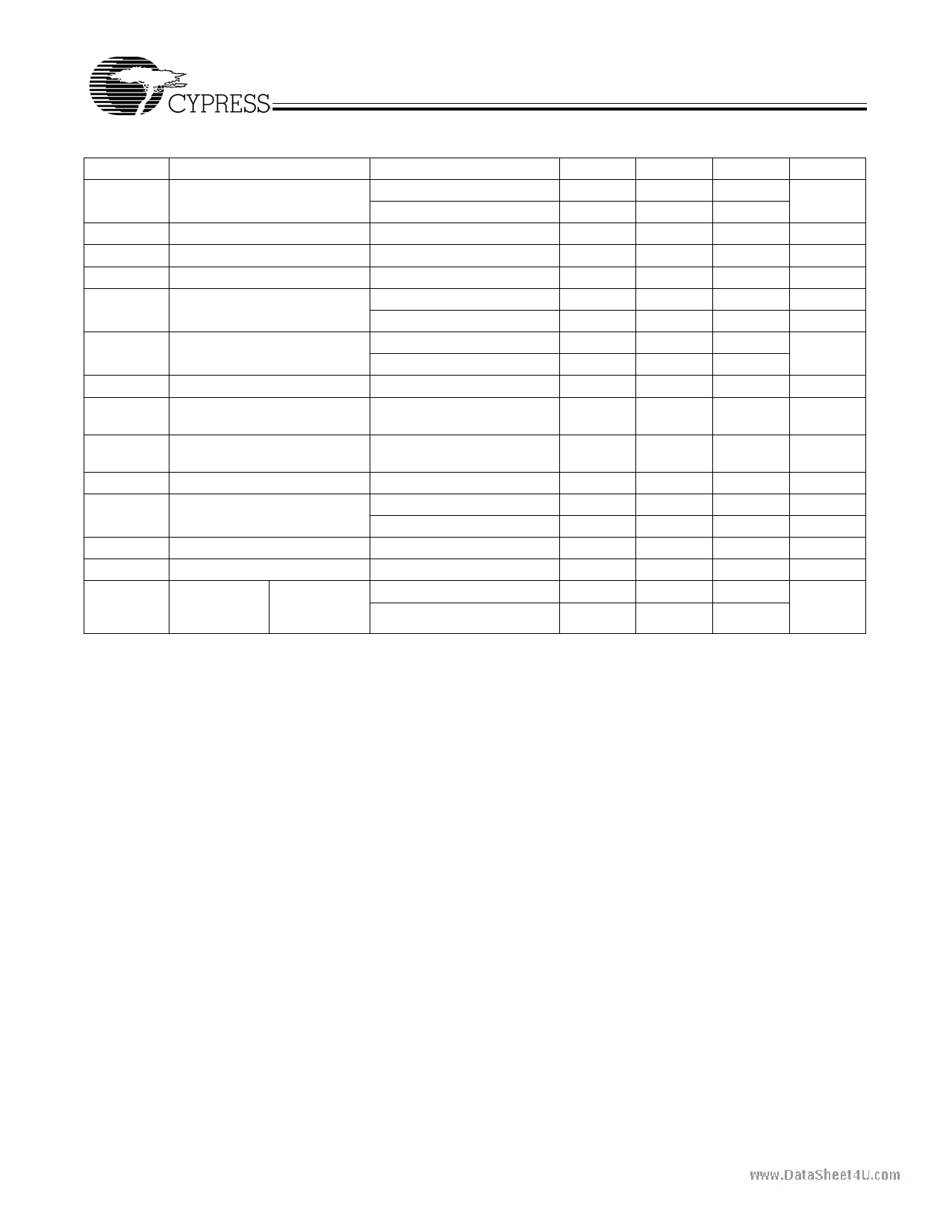

AC Electrical Characteristics VDD = 2.5V ±5% or 3.3V ±5%, TA = –40°C to +85°C[7]

Symbol

Parameter

Test Condition

Min.

Typ.

Fref Reference Input Frequency

FB_SEL = 1

16 –

FB_SEL = 0

25 –

FrefDC

Reference Input Duty Cycle

25 –

Fvco

PLL VCO Lock Range

200 –

Tlock

Maximum PLL lock Time

––

Tr / Tf

Fout

Output Clocks Rise / Fall

Time[8],[9]

Maximum Output Frequency

0.55V to 2.0V, VDD = 3.3V

0.5V to 1.8V, VDD = 2.5V

Q (÷2)

0.1

–

100

–

–

–

FoutDC

tpZL, tpZH

tpLZ, tpHZ

TCCJ

Output Duty Cycle[8],[9]

Output Enable Time[8] (all

outputs)

Output Disable Time[8] (all

outputs)

Cycle to Cycle Jitter[8],[9]

Q (÷4)

50 –

45 50

2–

2–

– ±100

Tskew

Any Output to Any Output

Skew[8],[9]

Same frequency

––

Different frequency – –

Tskew

Bank to Bank Skew

Tskew(pp) Part to Part Skew[10]

Banks at different voltages

–

–

–

–

Tpd Phase TCLK or

Error[8],[9]

PECL_CLK to

FB_IN

VDD = 3.3V

VDD = 2.5V

0 100

25 125

Note:

7. Parameters are guaranteed by design and characterization. Not 100% tested in production.

8. Outputs loaded with 30pF each.

9. 50Ω transmission line terminated into VDD/2.

10. Part to Part skew at a given temperature and voltage

Max.

33

50

75

400

10

1.0

–

200

100

55

10

8

–

150

300

400

450

200

225

Unit

MHz

%

MHz

ms

ns

MHz

%

ns

ns

ps

ps

ps

ps

ps

Document #: 38-07087 Rev. *C

Page 5 of 7

5 Page | ||

| Páginas | Total 7 Páginas | |

| PDF Descargar | [ Datasheet Z9960.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| Z9960 | 200 MHz Multi-Output Zero Delay Buffer | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |