|

|

PDF HYMP112S64MP8 Data sheet ( Hoja de datos )

| Número de pieza | HYMP112S64MP8 | |

| Descripción | DDR2 SDRAM SO-DIMM | |

| Fabricantes | Hynix Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HYMP112S64MP8 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Revision History

No. History

0.1

1) Defined target spec.

2) Corrected Pin assignment table

128Mx64 bits

DDR2 SDRAM SO-DIMM

HYMP112S64(L)MP8

Date

July 2004

Remark

This document is a general product description and is subject to change without notice. Hynix Semiconductor does not assume any

responsibility for use of circuits described. No patent licenses are implied.

Rev. 0.1/ July 2004

1

1 page

www.DataSheet4U.com

HYMP112S64(L)MP8

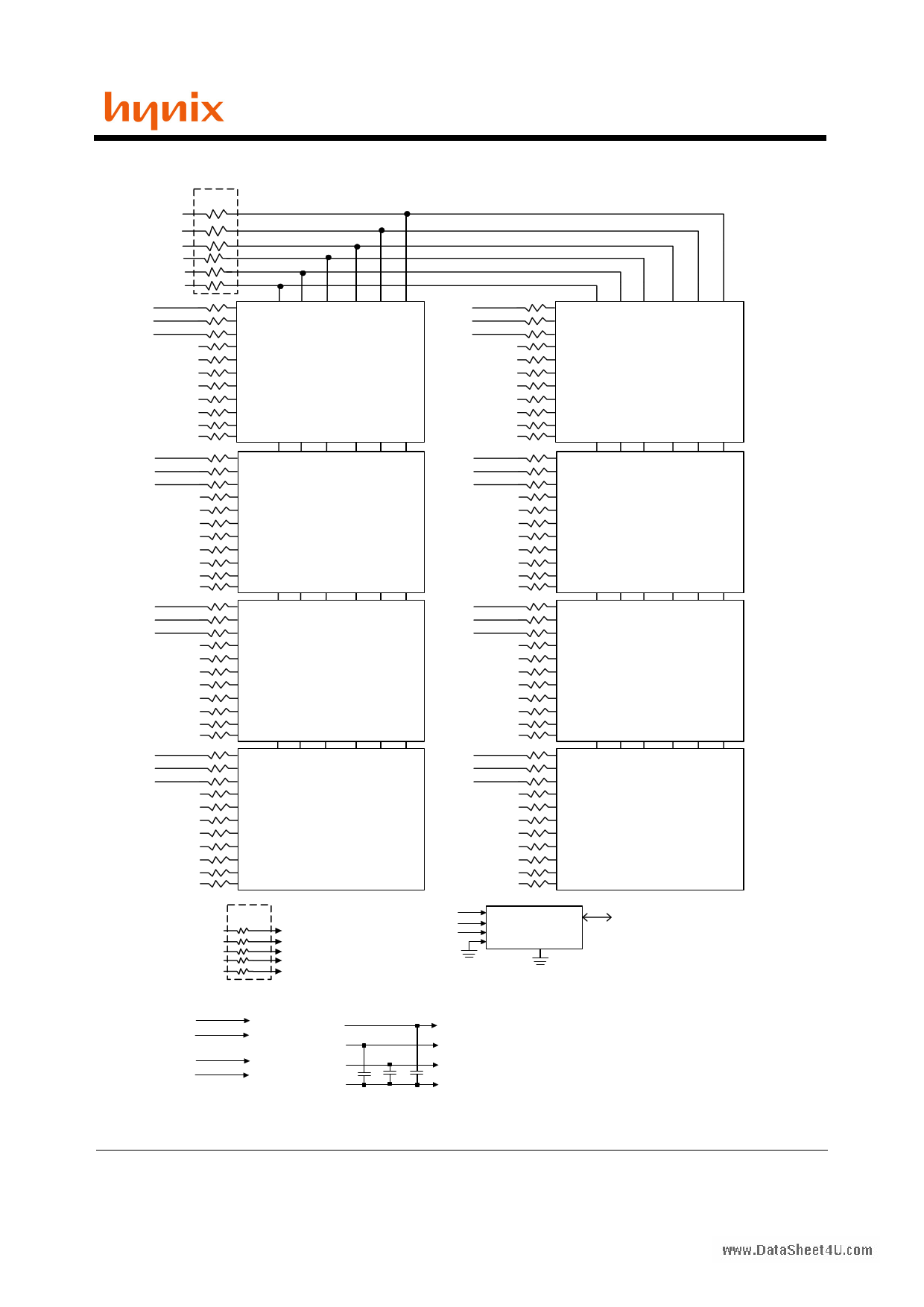

FUNCTIONAL BLOCK DIAGRAM

CKE1

ODT1

/S1

CKE0

ODT0

/S0

3Ω+/− 5%

DQS0

/DQS0

DM0

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQS

/DQS

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

/CS0 ODT0 CKE0 /CS1 ODT1 CKE1

D0,D8(DDP)

DQS1

/D Q S 1

DM1

DQS2

/D Q S 2

DM2

DQS3

/D Q S 3

DM3

DQ8

DQ8

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQS

/DQS

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

/CS0 ODT0 CKE0 /CS1 ODT1 CKE1

D1,D9(DDP)

DQS

/DQS

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

/CS0 ODT0 CKE0 /CS1 ODT1 CKE1

D2,D10(DDP)

DQS

/DQS

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

/CS0 ODT0 CKE0 /CS1 ODT1 CKE1

D3,D11(DDP)

DQS4

/DQS4

DM4

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQS5

/D Q S 5

DM5

DQS6

/D Q S 6

DM6

DQS7

/D Q S 7

DM7

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DQS

/DQS

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

/CS0 ODT0 CKE0 /CS1 ODT1 CKE1

D4,D12(DDP)

DQS /CS0 ODT0 CKE0 /CS1 ODT1 CKE1

/DQS

DM

I/O 0

I/O 1 D5,D13(DDP)

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DQS /CS0 ODT0 CKE0 /CS1 ODT1 CKE1

/DQS

DM

I/O 0

I/O 1

I/O 2

D6,D14(DDP)

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DQS /CS0 ODT0 CKE0 /CS1 ODT1 CKE1

/DQS

DM

I/O 0

I/O 1 D7,D15(DDP)

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

BA0-BA2

A0-AN

/RAS

/CAS

/WE

3Ω +/- 5%

SDRAMS D0-15

SDRAMS D0-15

SDRAMS D0-15

SDRAMS D0-15

SDRAMS D0-15

CK0

/CK0

CK1

/CK1

4 loads

4 loads

VDD SPD

VREF

VDD

VSS

SCL

SA0

SA1

SCL

A0

A1

A2

SDA

Serial PD

WP

SDA

Notes :

1. Unless otherwise noted, resistor values are 22 Ω ± 5%

2. DQ wring may differ form that described in this drawing; however ,

DQ,DM,DQS,/DQS relationships are maintained as shown.

Serial PD

SDRAMS DO-D15

SDRAMS DO-D15, VDD and VDDQ

SDRAMS DO-D15, SPD

Rev. 0.1/ July 2004

5

5 Page

www.DataSheet4U.com

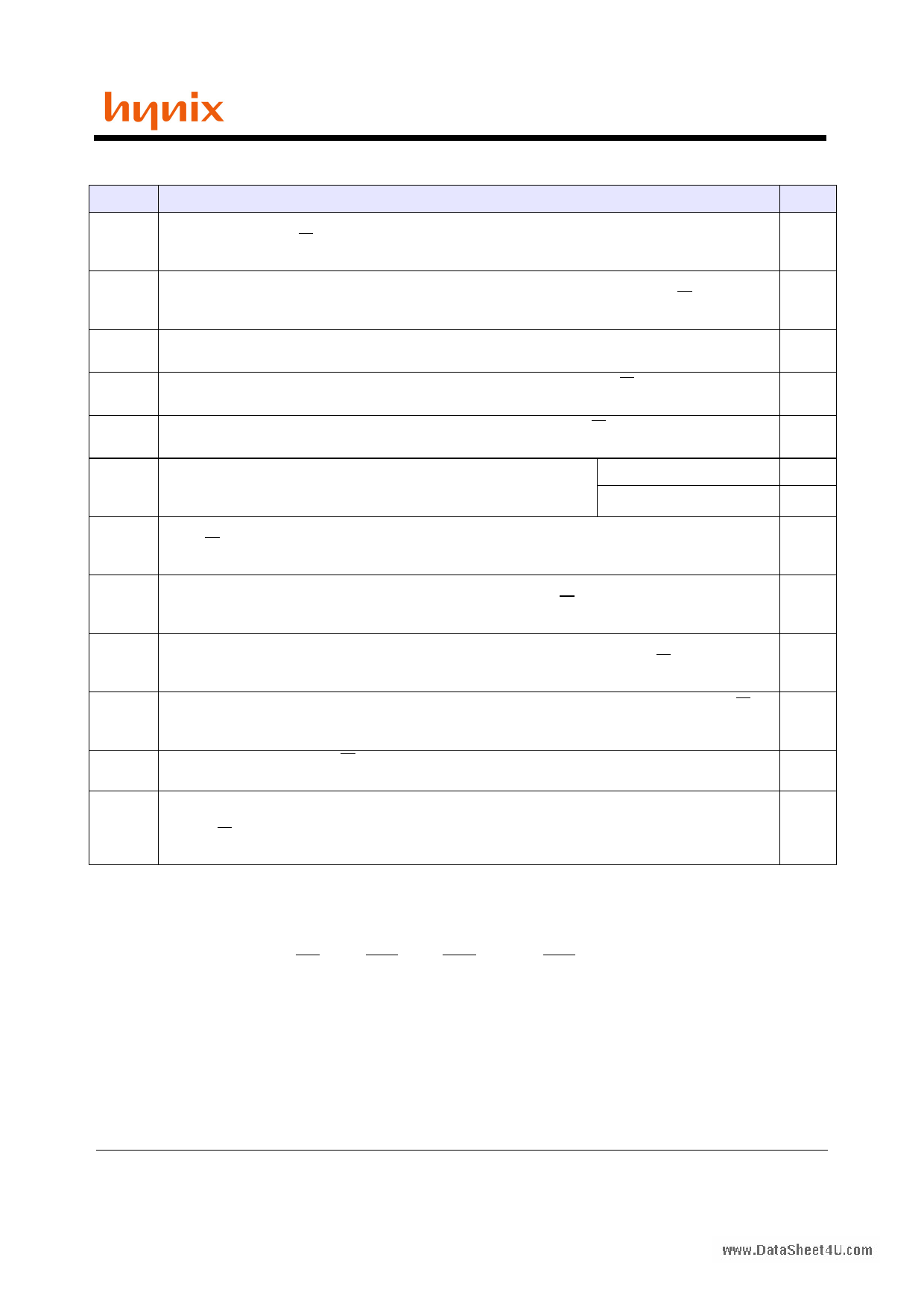

IDD Meauarement Conditions

HYMP112S64(L)MP8

Symbol

IDD0

IDD1

IDD2P

IDD2Q

IDD2N

IDD3P

IDD3N

IDD4W

IDD4R

IDD5B

IDD6

IDD7

Conditions

Operating one bank active-precharge current; tCK = tCK(IDD), tRC = tRC(IDD), tRAS = tRAS-

min(IDD);CKE is HIGH, CS is HIGH between valid commands;Address bus inputs are SWITCHING;Data bus

inputs are SWITCHING

Operating one bank active-read-precharge curren ; IOUT = 0mA;BL = 4, CL = CL(IDD), AL = 0;

tCK = tCK(IDD), tRC = tRC (IDD), tRAS = tRASmin(IDD), tRCD = tRCD(IDD) ; CKE is HIGH, CS is HIGH

between valid commands ; Address bus inputs are SWITCHING ; Data pattern is same as IDD4W

Precharge power-down current ; All banks idle ; tCK = tCK(IDD) ; CKE is LOW ; Other control and address

bus inputs are STABLE; Data bus inputs are FLOATING

Precharge quiet standby current;All banks idle; tCK = tCK(IDD);CKE is HIGH, CS is HIGH; Other control

and address bus inputs are STABLE; Data bus inputs are FLOATING

Precharge standby current; All banks idle; tCK = tCK(IDD); CKE is HIGH, CS is HIGH; Other control and

address bus inputs are SWITCHING; Data bus inputs are SWITCHING

Active power-down current; All banks open; tCK = tCK(IDD); CKE is

LOW; Other control and address bus inputs are STABLE; Data bus inputs are

FLOATING

Fast PDN Exit MRS(12) = 0

Slow PDN Exit MRS(12) = 1

Active standby current; All banks open; tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP =tRP(IDD); CKE is

HIGH, CS is HIGH between valid commands; Other control and address bus inputs are SWITCHING; Data bus

inputs are SWITCHING

Operating burst write current; All banks open, Continuous burst writes; BL = 4, CL = CL(IDD), AL = 0;

tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP = tRP(IDD); CKE is HIGH, CS is HIGH between valid commands;

Address bus inputs are SWITCHING; Data bus inputs are SWITCHING

Operating burst read current; All banks open, Continuous burst reads, IOUT = 0mA; BL = 4, CL =

CL(IDD), AL = 0; tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP = tRP(IDD); CKE is HIGH, CS is HIGH between

valid commands; Address bus inputs are SWITCHING;; Data pattern is same as IDD4W

Burst refresh current; tCK = tCK(IDD); Refresh command at every tRFC(IDD) interval; CKE is HIGH, CS is

HIGH between valid commands; Other control and address bus inputs are SWITCHING; Data bus inputs are

SWITCHING

Self refresh current; CK and CK at 0V; CKE £ 0.2V; Other control and address bus inputs are FLOATING;

Data bus inputs are FLOATING

Operating bank interleave read current; All bank interleaving reads, IOUT = 0mA; BL = 4, CL = CL(IDD),

AL = tRCD(IDD)-1*tCK(IDD); tCK = tCK(IDD), tRC = tRC(IDD), tRRD = tRRD(IDD), tRCD = 1*tCK(IDD); CKE

is HIGH, CS is HIGH between valid commands; Address bus inputs are STABLE during DESELECTs; Data pat-

tern is same as IDD4R; - Refer to the following page for detailed timing conditions

Units

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

Note:

1. IDD specifications are tested after the device is properly initialized

2. Input slew rate is specified by AC Parametric Test Condition

3. IDD parameters are specified with ODT disabled.

4. Data bus consists of DQ, DM, DQS, DQS, RDQS, RDQS, LDQS, LDQS, UDQS, and UDQS. IDD values must be met with all combinations

of EMRS bits 10 and 11.

5. Definitions for IDD

LOW is defined as Vin ≤ VILAC(max)

HIGH is defined as Vin ≥ VIHAC(min)

STABLE is defined as inputs stable at a HIGH or LOW level

FLOATING is defined as inputs at VREF = VDDQ/2

SWITCHING is defined as:

inputs changing between HIGH and LOW every other clock cycle (once per two clocks) for address and control signals, and

inputs changing between HIGH and LOW every other data transfer (once per clock) for DQ signals not including masks or strobes.

Rev. 0.1/ July 2004

11

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet HYMP112S64MP8.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HYMP112S64MP8 | DDR2 SDRAM SO-DIMM | Hynix Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |