|

|

PDF A25L40P Data sheet ( Hoja de datos )

| Número de pieza | A25L40P | |

| Descripción | Serial Flash Memory | |

| Fabricantes | AMIC Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de A25L40P (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

A25L40P Series

Preliminary

4 Mbit, Low Voltage, Serial Flash Memory

With 85MHz SPI Bus Interface

Document Title

4 Mbit, Low Voltage, Serial Flash Memory With 85MHz SPI Bus Interface

Revision History

Rev. No.

0.0

0.1

0.2

0.3

0.4

History

Initial issue

Add the Fast Read Dual Operation Instruction

Add QFN 8L (5 x 6mm) package type

Add QFN 8L (5 x 6mm) package outline dimensions

Modify the Part No. for Top/Bottom boot sector type

Add DIP 8(300mil) package type

Modify the maximum clock rate to 75MHz

Add transient voltage (<20ns) on any pin to ground potential spec.

Add the maximum clock rate of 3.0V~3.6V : 85MHz

Issue Date

August 29, 2006

April 4, 2006

April 20, 2006

September 5, 2006

May 25, 2007

Remark

Preliminary

PRELIMINARY (May, 2007, Version 0.4)

AMIC Technology Corp.

1 page

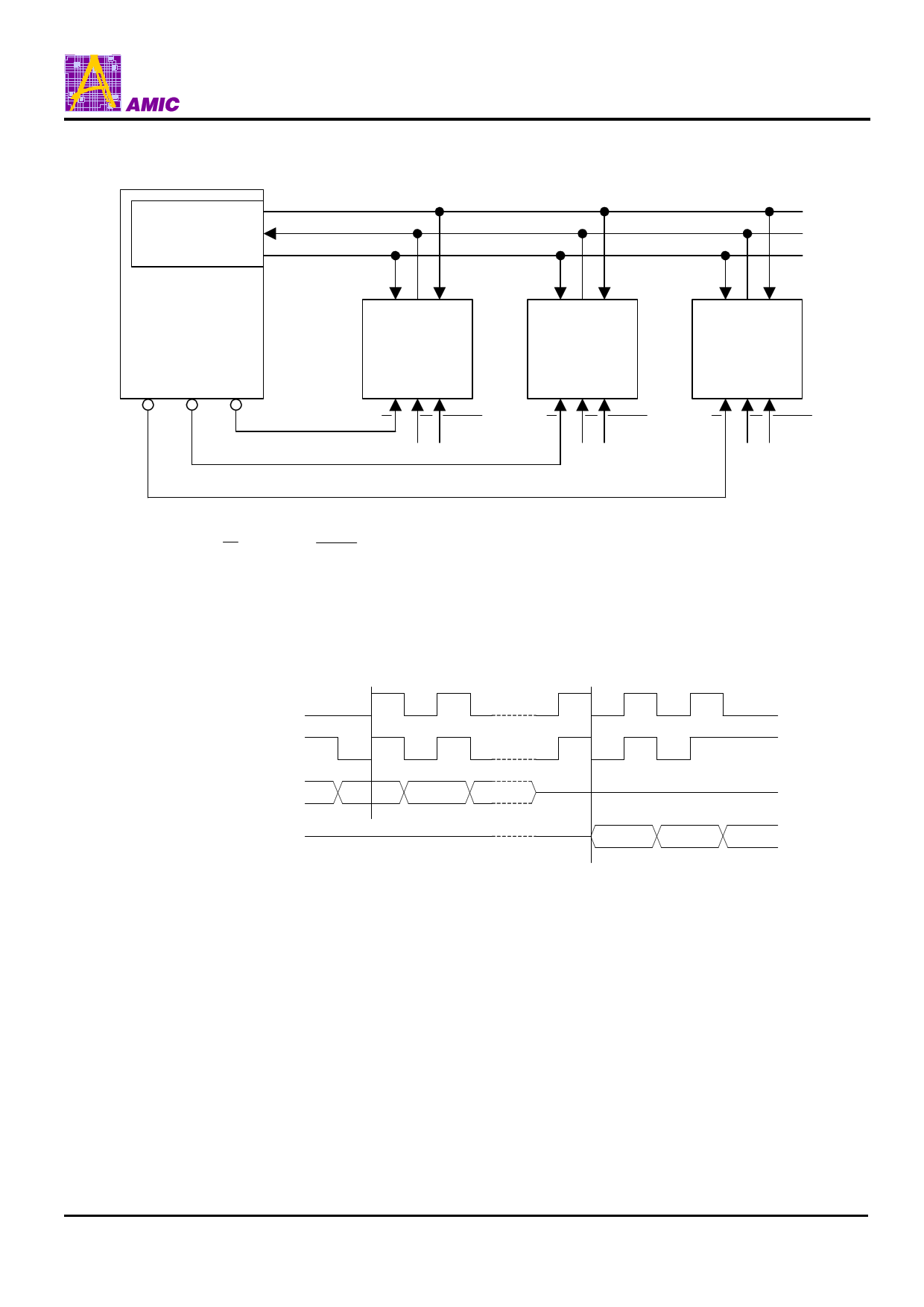

Figure 1. Bus Master and Memory Devices on the SPI Bus

SPI Interface with

(CPOL, CPHA)

= (0, 0) or (1, 1)

SDO

SDI

SCK

Bus Master

(ST6, ST7, ST9,

ST10, Other)

CS3 CS2 CS1

CQD

SPI Memory

Device

S W HOLD

CQD

SPI Memory

Device

S W HOLD

A25L40P Series

CQD

SPI Memory

Device

S W HOLD

Note: The Write Protect ( W ) and Hold ( HOLD ) signals should be driven, High or Low as appropriate.

Figure 2. SPI Modes Supported

CPOL CPHA

00

11

C

C

D

Q

MSB

MSB

PRELIMINARY (May, 2007, Version 0.4)

4

AMIC Technology Corp.

5 Page

Write Enable (WREN)

The Write Enable (WREN) instruction (Figure 4.) sets the

Write Enable Latch (WEL) bit.

The Write Enable Latch (WEL) bit must be set prior to every

Page Program (PP), Sector Erase (SE), Bulk Erase (BE) and

Write Status Register (WRSR) instruction.

A25L40P Series

The Write Enable (WREN) instruction is entered by driving

Chip Select ( S ) Low, sending the instruction code, and then

driving Chip Select ( S ) High.

Figure 4. Write Enable (WREN) Instruction Sequence

S

01 23 45 67

C

Instruction

D

High Impedance

Q

Write Disable (WRDI)

The Write Disable (WRDI) instruction (Figure 5.) resets the

Write Enable Latch (WEL) bit.

The Write Disable (WRDI) instruction is entered by driving Chip

Select ( S ) Low, sending the instruction code, and then driving

Chip The Write Enable Latch (WEL) bit is reset under the

following conditions:

﹣ Power-up

﹣ Write Disable (WRDI) instruction completion

﹣ Write Status Register (WRSR) instruction completion

﹣ Page Program (PP) instruction completion

﹣ Sector Erase (SE) instruction completion

﹣ Bulk Erase (BE) instruction completion

Figure 5. Write Disable (WRDI) Instruction Sequence

S

01 23 45 67

C

Instruction

D

High Impedance

Q

PRELIMINARY (May, 2007, Version 0.4)

10

AMIC Technology Corp.

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet A25L40P.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| A25L40P | Serial Flash Memory | AMIC Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |