|

|

PDF ICS889874 Data sheet ( Hoja de datos )

| Número de pieza | ICS889874 | |

| Descripción | DIFFERENTIAL-TO-LVPECL BUFFER/DIVIDER | |

| Fabricantes | ICS | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS889874 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Integrated

Circuit

Systems, Inc.

PRELIMINARY

ICS889874

1:2

DIFFERENTIAL-TO-LVPECL BUFFER/DIVIDER

GENERAL DESCRIPTION

ICS

The ICS889874 is a high speed 1:2 Differential-

to-LVPECL Buffer/Divider and is a member of

HiPerClockS™ the HiPerClockS ™ family of high performance

clock solutions from ICS. The ICS889874 has

a selectable ÷1, ÷2, ÷4, ÷8, ÷16 output divider,

which allows the device to be used as either a 1:2 fanout

buffer or frequency divider. The clock input has internal

termination resistors, allowing it to interface with several

differential signal types while minimizing the number of

required external components. The device is packaged in

a small, 3mm x 3mm VFQFN package, making it ideal for

use on space-constrained boards.

FEATURES

• 2 LVPECL outputs

• Frequency divide select options: ÷ 1, ÷ 2, ÷4, ÷8, ÷16

• IN, nIN input can accept the following differential input levels:

LVPECL, LVDS, CML

• Output frequency: > 2.5GHz

• Output skew: 5ps (typical)

• Part-to-part skew: TBD

• Additive jitter, RMS: <0.03ps (design target)

• Supply voltage range: (LVPECL), 2.375V to 3.465V

Supply voltage range: (ECL), -3.465V to -2.375V

• -40°C to 85°C ambient operating temperature

• Pin compatible with SY89874U

BLOCK DIAGRAM

S2

nRESET

IN

VT

nIN

S0

S1

Enable

FF

Enable

MUX

Decoder

00 ÷2

01 ÷4

10 ÷8

11 ÷16

0

1

PIN ASSIGNMENT

Q0

nQ0

16 15 14 13

Q0 1

12 IN

nQ0 2

11 VT

Q1 3

1 0 VREF_AC

nQ1 4

9 nIN

5678

Q1

nQ1 ICS889874

16-Lead VFQFN

3mm x 3mm x 0.95 package body

K Package

Top View

VREF_AC

The Preliminary Information presented herein represents a product in prototyping or pre-production. The noted characteristics are based on initial

product characterization. Integrated Circuit Systems, Incorporated (ICS) reserves the right to change any circuitry or specifications without notice.

889874AK

www.icst.com/products/hiperclocks.html

REV. A MAY 19, 2004

1

1 page

Integrated

Circuit

Systems, Inc.

PRELIMINARY

ICS889874

1:2

DIFFERENTIAL-TO-LVPECL BUFFER/DIVIDER

TABLE 4D. LVPECL DC CHARACTERISTICS, VCC = 3.3V±10% OR 2.5V±5%; TA = -40°C TO 85°C

Symbol Parameter

Conditions

Minimum Typical

VOH Output High Voltage; NOTE 1

VOL Output Low Voltage; NOTE 1

VCC - 1.005

VCC - 1.78

VOUT

Output Voltage Swing

800

VDIFF_OUT Differential Output Voltage Swing

Input and output parameters vary 1:1 with V . V can vary +0.925V to -0.5V.

CC EE

NOTE 1: Outputs terminated with 50Ω to VCC - 2V.

1.60

Maximum

Units

mV

mV

mV

V

TABLE

5.

AC

CHARACTERISTICS,

V

CC

=

3.3V±10%

OR

2.5V±5%;

TA

=

-40°C

TO

85°C

Symbol Parameter

Condition

Minimum Typical Maximum

Maximum Output Frequency

fMAX Maximum Input Frequency

Output Swing ≥ 450mV

÷ 2, ÷4, ÷8, ÷16

2

2

tPD

Propagation Delay, (Differential);

NOTE 1

Input Swing: < 400mV

Input Swing: ≥ 400mV

725

725

tsk(o) Output Skew; NOTE 2, 4

5

tsk(pp) Part-to-Part Skew; NOTE 3, 4

TBD

tjit

Additive Phase Jitter, RMS;

refer to Additive Phase Jitter section

<0.03

tRR Reset Recovery Time

tR/tF Output Rise/Fall Time

20% to 80%

TBD

180

tS Clock Enable Setup Time EN to IN, nIN

TBD

tH Clock Enable Hold Time EN to IN, nIN

TBD

All parameters characterized at ≤ 1GHz unless otherwise noted.

NOTE 1: Measured from the differential input crossing point to the differential output crossing point.

NOTE 2: Defined as skew between outputs at the same supply voltage and with equal load conditions.

Measured at the output differential cross points.

NOTE 3: Defined as skew between outputs on different devices operating at the same supply voltages

and with equal load conditions. Using the same type of inputs on each device, the outputs are measured

at the differential cross points.

NOTE 4: This parameter is defined in accordance with JEDEC Standard 65.

Units

GHz

GHz

ps

ps

ps

ps

ps

ps

ps

ps

ps

889874AK

www.icst.com/products/hiperclocks.html

5

REV. A MAY 19, 2004

5 Page

Integrated

Circuit

Systems, Inc.

PRELIMINARY

ICS889874

1:2

DIFFERENTIAL-TO-LVPECL BUFFER/DIVIDER

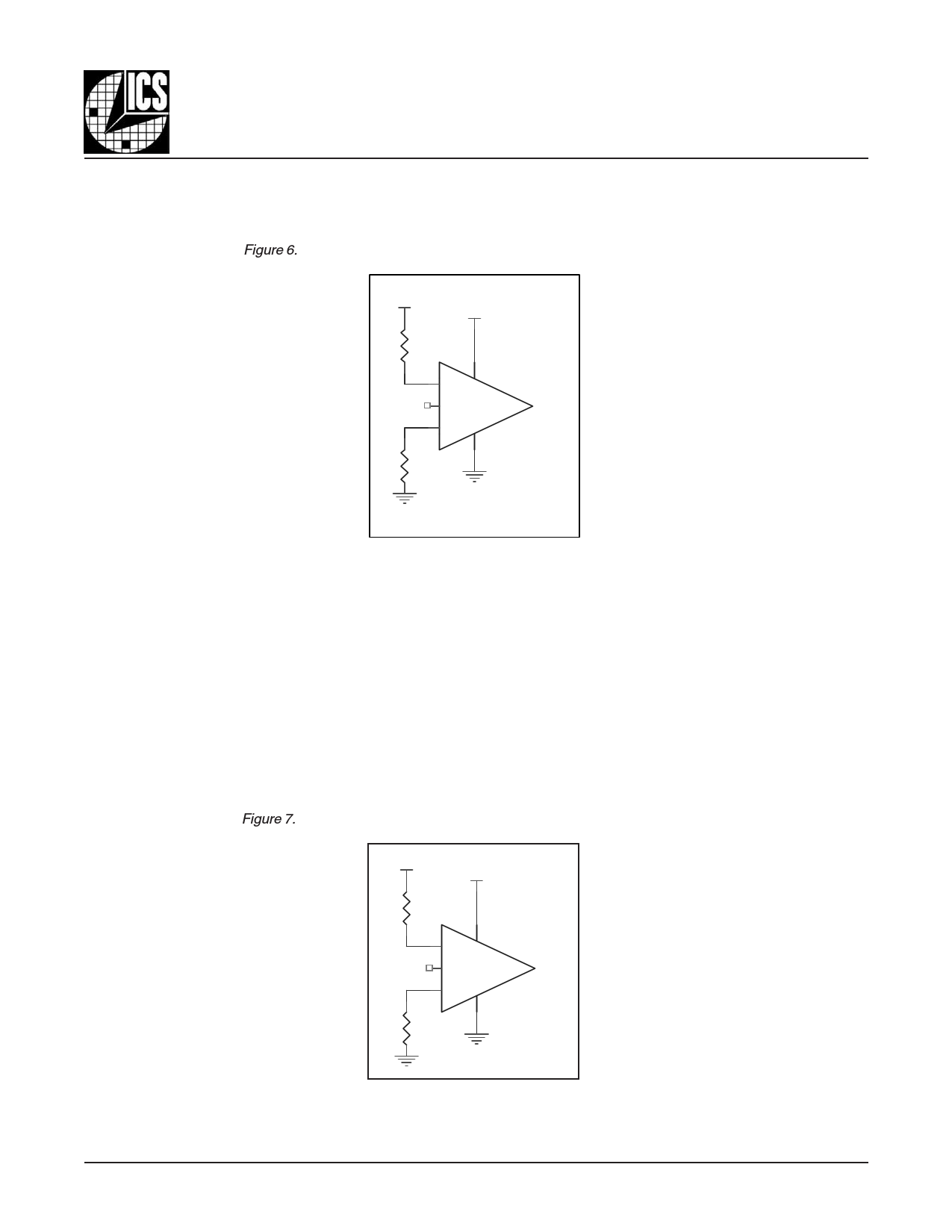

3.3V DIFFERENTIAL INPUT WITH BUILT-IN 50Ω TERMINATION UNUSED INPUT HANDLING

To prevent oscillation and to reduce noise, it is recommended to

have pullup and pulldown connect to true and compliment of the

unused input as shown in Figure 6.

3.3V

3.3V

R1

1K

IN

VT

nIN

R2

1K

Receiver

with

Built-In

50 Ohm

FIGURE 6. UNUSED INPUT HANDLING

2.5V DIFFERENTIAL INPUT WITH BUILT-IN 50Ω TERMINATION UNUSED INPUT HANDLING

To prevent oscillation and to reduce noise, it is recommended to

have pullup and pulldown connect to true and compliment of the

unused input as shown in Figure 7.

2.5V

2. 5V

R1

680

IN

VT

nI N

R2

680

Receiver

with

Built-In

50 Ohm

FIGURE 7. UNUSED INPUT HANDLING

889874AK

www.icst.com/products/hiperclocks.html

11

REV. A MAY 19, 2004

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet ICS889874.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS889872 | DIFFERENTIAL-TO-LVDS BUFFER/DIVIDER W/INTERNAL TERMINATION | IDT |

| ICS889874 | DIFFERENTIAL-TO-LVPECL BUFFER/DIVIDER | ICS |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |