|

|

PDF 89HPES32H8 Data sheet ( Hoja de datos )

| Número de pieza | 89HPES32H8 | |

| Descripción | 32-Lane 8-Port PCI Express System Interconnect Switch | |

| Fabricantes | IDT | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 89HPES32H8 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

32-Lane 8-Port PCI Express®

System Interconnect Switch

®

89HPES32H8

Data Sheet

Device Overview

The 89HPES32H8 is a member of the IDT PRECISE™ family of PCI

Express® switching solutions. The PES32H8 is a 32-lane, 8-port system

interconnect switch optimized for PCI Express packet switching in high-

performance applications, supporting multiple simultaneous peer-to-

peer traffic flows. Target applications include servers, storage, communi-

cations, and embedded systems.

Features

◆ High Performance PCI Express Switch

– Eight maximum switch ports

• Four main ports each of which consists of eight SerDes

• Each x8 main port can further bifurcate to 2 x4-ports

– Thirty-two 2.5 Gbps embedded SerDes

• Supports pre-emphasis and receive equalization on per-port

basis

– Delivers 128 Gbps (16 GBps) aggregate switching capacity

– Low-latency cut-through switch architecture

– Support for Max Payload Size up to 2048 bytes

– Supports two virtual channels and eight traffic classes

– PCI Express Base Specification Revision 1.1 compliant

◆ Flexible Architecture with Numerous Configuration Options

– Port arbitration schemes utilizing round robin algorithms

– Virtual channels arbitration based on priority

– Automatic per port link width negotiation to x8, x4, x2 or x1

– Automatic lane reversal on all ports

– Automatic polarity inversion on all ports

– Supports locked transactions, allowing use with legacy soft-

ware

– Ability to load device configuration from serial EEPROM

– Ability to control device via SMBus

◆ Highly Integrated Solution

– Requires no external components

– Incorporates on-chip internal memory for packet buffering and

queueing

– Integrates thirty-two 2.5 Gbps embedded full duplex SerDes,

8B/10B encoder/decoder (no separate transceivers needed)

◆ Reliability, Availability, and Serviceability (RAS) Features

– Redundant upstream port failover capability

– Internal end-to-end parity protection on all TLPs ensures data

integrity even in systems that do not implement end-to-end

CRC (ECRC)

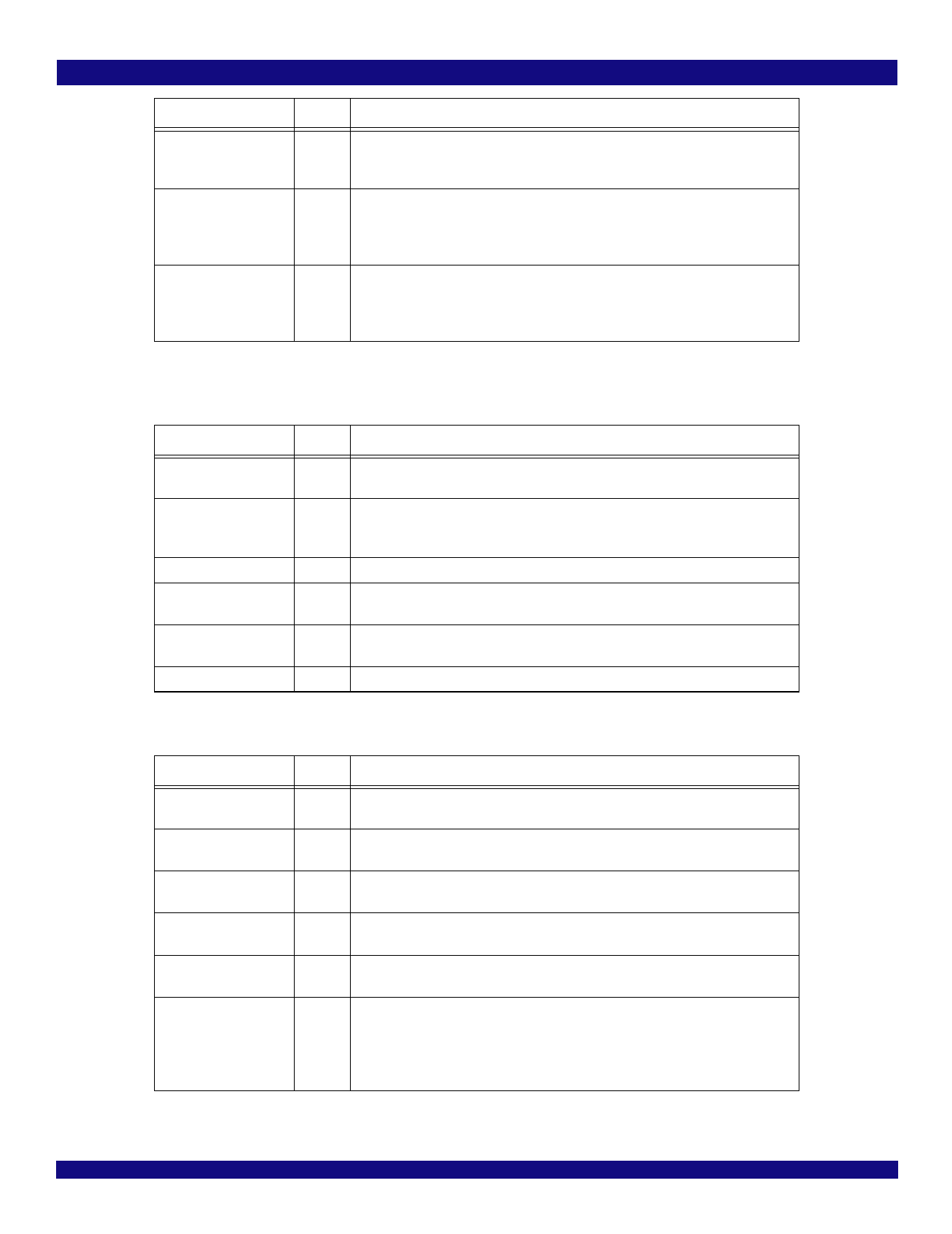

Block Diagram

x8/x4/x2/x1

SerDes

DL/Transaction Layer

x8/x4/x2/x1

SerDes

DL/Transaction Layer

Route Table

Frame Buffer

8-Port Switch Core

Port

Arbitration

Scheduler

DL/Transaction Layer

SerDes

DL/Transaction Layer

SerDes

x8/x4/x2/x1

x8/x4/x2/x1

Figure 1 Internal Block Diagram

© 2007 Integrated Device Technology, Inc.

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc.

1 of 40

July 19, 2007

1 page

IDT 89HPES32H8 Data Sheet

Signal

PE7TP[3:0]

PE7TN[3:0]

REFCLKM

PEREFCLKP[3:0]

PEREFCLKN[3:0]

Type

Name/Description

O PCI Express Port 7 Serial Data Transmit. Differential PCI Express transmit pairs for

port 7. When port 6 is merged with port 7, these signals become port 6 transmit pairs

for lanes 4 through 7.

I PCI Express Reference Clock Mode Select. This signal selects the frequency of the

reference clock input.

0x0 - 100 MHz

0x1 - 125 MHz

I PCI Express Reference Clock. Differential reference clock pair input. This clock is

used as the reference clock by on-chip PLLs to generate the clocks required for the

system logic and on-chip SerDes. The frequency of the differential reference clock is

determined by the REFCLKM signal.

Table 2 PCI Express Interface Pins (Part 2 of 2)

Signal

MSMBADDR[4:1]

MSMBCLK

MSMBDAT

SSMBADDR[5,3:1]

SSMBCLK

SSMBDAT

Type

Name/Description

I Master SMBus Address. These pins determine the SMBus address of the serial

EEPROM from which configuration information is loaded.

I/O Master SMBus Clock. This bidirectional signal is used to synchronize transfers on the

master SMBus. It is active and generating the clock only when the EEPROM or I/O

Expanders are being accessed.

I/O Master SMBus Data. This bidirectional signal is used for data on the master SMBus.

I Slave SMBus Address. These pins determine the SMBus address to which the slave

SMBus interface responds.

I/O Slave SMBus Clock. This bidirectional signal is used to synchronize transfers on the

slave SMBus.

I/O Slave SMBus Data. This bidirectional signal is used for data on the slave SMBus.

Table 3 SMBus Interface Pins

Signal

GPIO[0]

GPIO[1]

GPIO[2]

GPIO[3]

GPIO[4]

GPIO[5]

Type

Name/Description

I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

Alternate function pin name: GPEN

Alternate function pin type: Output

Alternate function: General Purpose Event (GPE) output

Table 4 General Purpose I/O Pins (Part 1 of 3)

5 of 40

July 19, 2007

5 Page

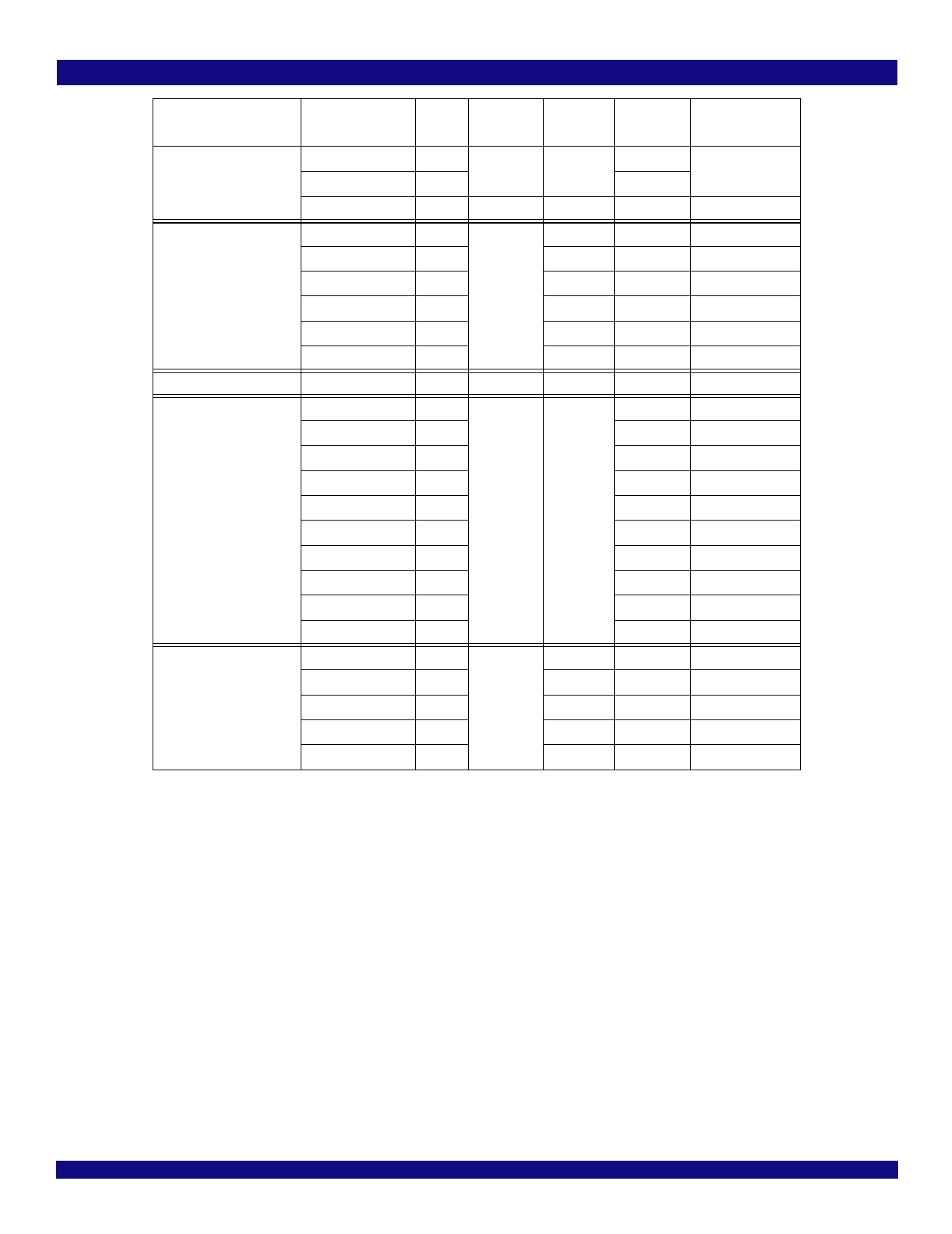

IDT 89HPES32H8 Data Sheet

Function

Pin Name Type Buffer

I/O Internal

Type Resistor

Notes

PCI Express Interface

(cont.)

SMBus

General Purpose I/O

System Pins

EJTAG / JTAG

PEREFCLKN[3:0]

PEREFCLKP[3:0]

REFCLKM

MSMBADDR[4:1]

MSMBCLK

MSMBDAT

SSMBADDR[5,3:1]

SSMBCLK

SSMBDAT

GPIO[31:0]

CCLKDS

CCLKUS

MSMBSMODE

P01MERGEN

P23MERGEN

P45MERGEN

P67MERGEN

PERSTN

RSTHALT

SWMODE[3:0]

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST_N

I

I

I

I

I/O

I/O

I

I/O

I/O

I/O

I

I

I

I

I

I

I

I

I

I

I

I

O

I

I

LVPECL/

CML

LVTTL

LVTTL

LVTTL

LVTTL

Diff. Clock

Input

Input

STI1

STI

STI

STI

STI

Input

Refer to Table 9

pull-down

pull-up

pull-up

pull-up

pull-up

pull-up

pull-down

pull-down

pull-down

pull-down

pull-down

LVTTL

pull-down

pull-down

STI pull-up

STI pull-up

STI pull-up

STI pull-up External pull-down

1. Schmitt Trigger Input (STI).

Table 8 Pin Characteristics (Part 2 of 2)

11 of 40

July 19, 2007

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet 89HPES32H8.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 89HPES32H8 | 32-Lane 8-Port PCI Express System Interconnect Switch | IDT |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |