|

|

PDF MAX3420E Data sheet ( Hoja de datos )

| Número de pieza | MAX3420E | |

| Descripción | USB Peripheral Controller | |

| Fabricantes | Maxim Integrated Products | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAX3420E (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

MAX3420E

EVALUATION KIT AVAILABLE

USB Peripheral Controller with SPI Interface

General Description

The MAX3420E contains the digital logic and analog

circuitry necessary to implement a full-speed USB periph-

eral compliant to USB specification rev 2.0. A built-in

full-speed transceiver features ±15kV ESD protection and

programmable USB connect and disconnect. An internal

serial-interface engine (SIE) handles low-level USB pro-

tocol details such as error checking and bus retries. The

MAX3420E operates using a register set accessed by an

SPI interface that operates up to 26MHz. Any SPI master

(microprocessor, ASIC, DSP, etc.) can add USB function-

ality using the simple 3- or 4-wire SPI interface.

Internal level translators allow the SPI interface to run at

a system voltage between 1.71V and 3.6V. USB timed

operations are done inside the MAX3420E with interrupts

provided at completion so an SPI master does not need

timers to meet USB timing requirements. The MAX3420E

includes four general-purpose inputs and outputs so any

microprocessor that uses I/O pins to implement the SPI

interface can reclaim the I/O pins and gain additional

ones.

The MAX3420E operates over the extended -40°C to

+85°C temperature range and is available in a 32-pin

LQFP package (7mm x 7mm) and a space-saving 24-pin

TQFN package (4mm x 4mm).

Applications

●● Cell Phones

●● PC Peripherals

●● Microprocessors and

DSPs

●● Custom USB Devices

●● Cameras

●● Desktop Routers

●● PLCs

●● Set-Top Boxes

●● PDAs

●● MP3 Players

●● Instrumentation

Ordering Information

PART

TEMP RANGE PIN-PACKAGE

MAX3420EETG+

-40°C to +85°C 24 TQFN-EP*

MAX3420EECJ+

-40°C to +85°C 32 LQFP

MAX3420EECJ/V+ -40°C to +85°C 32 LQFP

+Denotes a lead(Pb)-free/RoHS-compliant package.

*EP = Exposed pad.

/V denotes an automotive qualified part.

Benefits and Features

●● Simplifies Adding USB to Any System

• Microprocessor-Independent USB Solution

• Complies with USB Specification Revision 2.0

(Full-Speed Operation)

• Integrated Full-Speed USB Transceiver

• Firmware/Hardware Control of an Internal D+

Pullup Resistor

• Programmable 3- or 4-Wire 26MHz SPI Interface

• Intelligent USB Serial-Interface Engine (SIE)

Automatically Handles USB Flow Control and

Double Buffering

Handles Low-Level USB Signaling Details

Includes Timers for USB Time-Sensitive

Operations, So SPI Master Does Not Need

to Time Events

• Four General-Purpose Inputs and Four General-

Purpose Outputs

●● Internal Comparator Detects VBUS for Self-Powered

Applications

●● Interrupt Output Pin (Level or Programmable Edge)

Allows Polled or Interrupt-Driven SPI Interface

●● Double-Buffered Data Endpoints Increase

Throughput by Allowing the SPI Master to Transfer

Data Concurrently with USB Transfers Over the

Same Endpoint

• Built-In Endpoint FIFOs

EP0: CONTROL (64 Bytes)

EP1: OUT, Bulk or Interrupt, 2 x 64 Bytes

(Double-Buffered)

EP2: IN, Bulk or Interrupt, 2 x 64 Bytes

(Double-Buffered)

EP3: IN, Bulk or Interrupt (64 Bytes)

●● SETUP Data Has Its Own 8-Byte FIFO, Simplifying

Firmware

●● ESD Protection on D+, D-, and VBCOMP Improves

System Reliability

19-3781; Rev 4; 2/15

1 page

MAX3420E

USB Peripheral Controller with SPI Interface

Pin Description (continued)

PIN

TQFN-EP LQFP

NAME

INPUT/

OUTPUT

FUNCTION

USB Transceiver Power-Supply Input. Connect VCC to a positive 3.3V power

17 22, 23 VCC Input supply. Bypass VCC to ground with a 1.0µF ceramic capacitor as close to the

VCC pin as possible.

VBUS Comparator Input. VBCOMP is internally connected to a voltage

18

24

VBCOMP

Input

comparator to allow the SPI master to detect (through an interrupt or checking a

register bit) the presence or loss of power on VBUS. Bypass VBCOMP to ground

with a 1.0µF ceramic capacitor.

Crystal Oscillator Input. Connect XI to one side of a parallel resonant 12MHz

19 26 XI Input ±0.25% crystal and a capacitor to GND. XI can also be driven by an external

Clock referenced to VCC.

Crystal Oscillator Output. Connect XO to the other side of a parallel resonant

20 27 XO Output 12MHz ±0.25% crystal and a capacitor to GND. Leave XO unconnected if XI is

driven with an external source.

21 29 GPIN0

General-Purpose Inputs. GPIN3–GPIN0 are connected to VL with internal pullup

22

23

30

31

GPIN1

GPIN2

Input

resistors. GPIN3–GPIN0 logic levels are referenced to the voltage on VL. The

SPI master samples GPIN3–GPIN0 states by reading bit 7 through bit 4 of the

24 32 GPIN3

IOPINS (R20) register. Writing to these bits has no effect.

—

9, 16, 25,

28

N.C.

— No Internal Connection

— — EP Input Exposed Paddle (TQFN only). Connect EP to GND.

Register Description

The SPI master controls the MAX3420E by reading and

writing 21 registers (Table 1). For a complete description

of register contents, please refer to the “MAX3420E

Programming Guide.” A register access consists of the

SPI master first writing an SPI command byte, followed

by reading or writing the contents of the addressed

register. All SPI transfers are MSB first. The command

byte contains the register address, a direction bit (read

= 0, write = 1), and the ACKSTAT bit (Figure 4). The

SPI master addresses the MAX3420E registers by writ-

ing the binary value of the register number in the Reg4

through Reg0 bits of the command byte. For example,

to access the IOPINS (R20) register, the Reg4 through

Reg0 bits would be as follows: Reg4 = 1, Reg3 = 0,

Reg2 = 1, Reg1 = 0, Reg0 = 0. The DIR (direction) bit

determines the direction for the data transfer. DIR = 1

means the data byte(s) will be written to the register,

and DIR = 0 means the data byte(s) will be read from

the register. The ACKSTAT bit sets the ACKSTAT bit in

the EPSTALLS (R9) register. The SPI master sets this

bit to indicate that it has finished servicing a CONTROL

transfer. Since the bit is frequently used, having it in the

SPI command byte improves firmware efficiency. In SPI

full-duplex mode, the MAX3420E clocks out eight USB

status bits as the command byte is clocked in (Figure 5).

In half-duplex mode, these status bits are accessed

in the normal way, as register bits.

b7 b6

Reg4

Reg3

Figure 4. SPI Command Byte

b5

Reg2

b4

Reg1

b3

Reg0

b2

0

b1 b0

DIR ACKSTAT

b7 b6 b5 b4 b3 b2 b1

SUSPIRQ

URESIRQ SUDAVIRQ IN3BAVIRQ IN2BAVIRQ OUT1DAVIRQ OUT0DAVIRQ

Figure 5. USB Status Bits Clocked Out as First Byte of Every Transfer (Full-Duplex Mode Only)

b0

IN0BAVIRQ

www.maximintegrated.com

Maxim Integrated │ 5

5 Page

MAX3420E

USB Peripheral Controller with SPI Interface

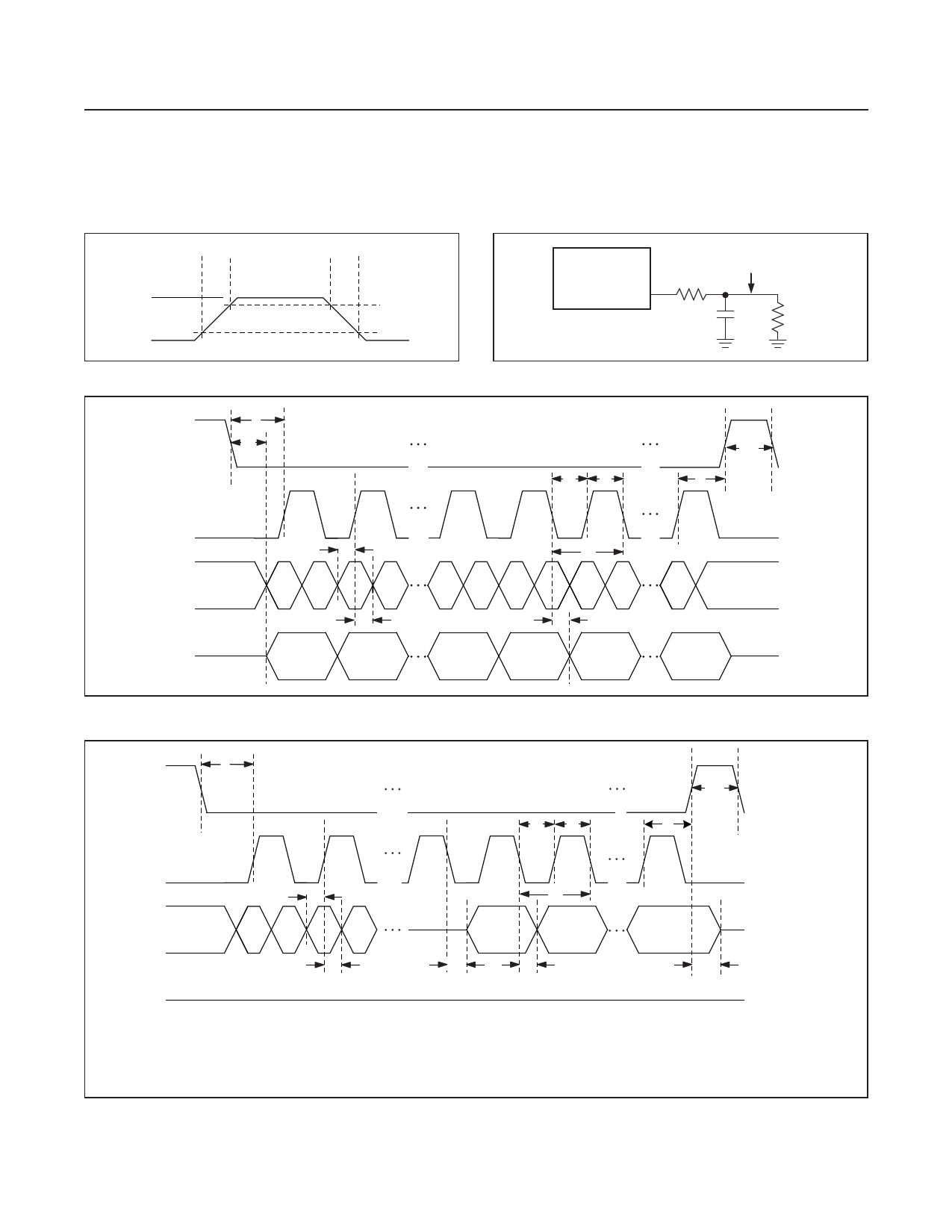

Test Circuits and Timing Diagrams

tRISE

tFALL

VOH

VOL

Figure 6. Rise and Fall Times

90%

10%

MAX3420E

D+ OR D-

33Ω

TEST

POINT

CL 15kΩ

Figure 7. Load for D+/D- AC Measurements

tL

SS tCSS

SCLK

MOSI

HIGH

MISO IMPEDANCE

12

tDS

tDH

tCL tCH

8 9 10

tCP

tDO

Figure 8. SPI Bus Timing Diagram (Full-Duplex Mode, SPI Mode (0,0))

tCSW

tT

16

HIGH

IMPEDANCE

tL

SS

tCSW

tCL tCH

tT

SCLK

MOSI

12

tDS

8 9 10

tCP

16

HI-Z

tDH tON tDI

tOFF

MISO HIGH IMPEDANCE

HIGH IMPEDANCE

NOTES:

1) DURING THE FIRST 8 CLOCKS CYCLES, THE MOSI PIN IS HIGH IMPEDANCE AND THE SPI MASTER DRIVES DATA ONTO THE MOSI PIN. SETUP AND HOLD TIMES ARE THE SAME AS

FOR FULL-DUPLEX MODE.

2) FOR SPI WRITE CYCLES, THE MOSI PIN CONTINUES TO BE HIGH IMPEDANCE AND THE EXTERNAL MASTER CONTINUES TO DRIVE MOSI.

3) FOR SPI READ CYCLES, AFTER THE 8TH CLOCK-RISING EDGE, THE MAX3420E STARTS DRIVING THE MOSI PIN AFTER TIME tON. THE EXTERNAL MASTER MUST TURN

OFF ITS DRIVER TO THE MOSI PIN BEFORE tON TO AVOID CONTENTION. PROPAGATION DELAYS ARE THE SAME AS FOR THE MOSI PIN IN FULL-DUPLEX MODE.

Figure 9. SPI Bus Timing Diagram (Half-Duplex Mode, SPI Mode (0,0))

www.maximintegrated.com

Maxim Integrated │ 11

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet MAX3420E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAX3420E | USB Peripheral Controller | Maxim Integrated Products |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |