|

|

PDF XRK69773 Data sheet ( Hoja de datos )

| Número de pieza | XRK69773 | |

| Descripción | 1:12 LVCMOS PLL CLOCK GENERATOR | |

| Fabricantes | Exar Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XRK69773 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

PRELIMINARY

XRK69773

1:12 LVCMOS PLL CLOCK GENERATOR

APRIL 2006

REV. P1.0.0

GENERAL DESCRIPTION

The XRK69773 is a PLL based LVCMOS Clock Generator

targeted for high performance and low skew clock distribu-

tion applications. The XRK69773 can select between one

of three reference inputs and provides 14 LVCMOS outputs

-12 outputs (3 banks of 4) for clock distribution, 1 for feed-

back and 1 for synchronization.

The XRK69773 is a highly flexible device. It has 3 select-

able inputs, (one differential and two single-ended inputs) to

support system clock redundancy. Up to three different

clock frequencys can be generated and outputted on the

three output banks. Switching the internal reference clock

is controlled by the control input, CLK_SEL.

The XRK69773 uses PLL technology to frequency lock its

outputs to the input reference clock. The divider in the feed-

back path will determine the frequency of the VCO. Each of

the separate output banks can individually divide down the

VCO output frequency. This allows the XRK69773 to gen-

erate a multitude of different bank frequency ratios and out-

put-to-input frequency ratios.

The outputs of the XRK69773 can individually be immobi-

lized, in the low state, by use of the clock stop feature. All

outputs except QC0 and QFB can be immobilized through a

2 pin serial interface. Global output disabling and reset can

be achieved the control input MR/OE.

The XRK69773 also has a QSYNC output which can be

used for system synchronization purposes. It monitors

Bank A and Bank C outputs and goes low one period of the

faster clock prior to coincident rising edges of Bank A and

Bank C clocks. QSYNC then goes high again when the

coincident rising edges of Bank A and Bank C occur. This

feature is used primarily in applications where Bank A and

Bank C are running at different frequencies, and is

particularly useful when they are running at non-integer

multiples of one another.

The XRK69773 has an output frequency range of 8.33MHz

to 240MHz and an input frequency range of 5MHz to

120MHz.

FEATURES

• Fully Integrated PLL

• Selectable Differential PECL or LVCMOS inputs for

reference clock source

• 14 LVCMOS outputs

■ 3 banks with 4 outputs each. Frequencies can

be individually controlled by bank

■ 1 dedicated feedback with frequency control

■ 1 Sync

• VCO Range 200MHz to 480MHz

• Output freq. range: 8.33MHz to 240MHz

• Max Output Skew of 250ps

• Cycle-to-cycle jitter: 150ps (typ)

APPLICATIONS

• System Clock generator

• Zero Delay Buffer

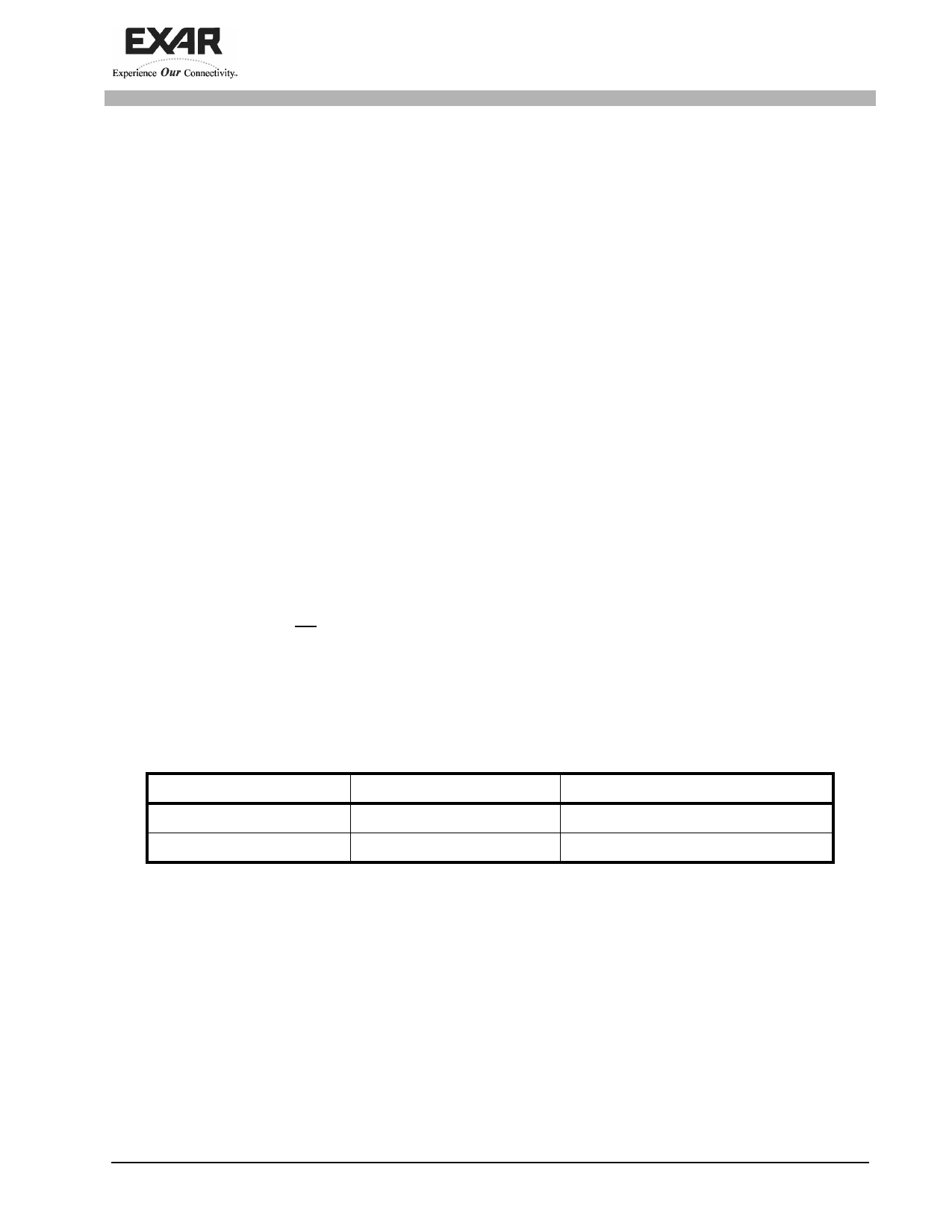

PRODUCT NUMBER

XRK69773CR

XRK69773IR

PRODUCT ORDERING INFORMATION

PACKAGE TYPE

52-LEAD LQFP

OPERATING TEMPERATURE RANGE

0°C to +70°C

52-LEAD LQFP

-40°C to +85°C

Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

1 page

REV. P1.0.0

PRELIMINARY

XRK69773

1:12 LVCMOS PLL CLOCK GENERATOR

TABLE 4: AC CHARACTERISTICS (VDD = 3.3V +/- 5%)

SYMBOL

CHARACTERISTICS

CONDITION

MIN TYP MAX UNIT

fREF

Input reference frequencya

÷4 feedback

÷6 feedback

÷8 feedback

÷10 feedback

÷12 feedback

÷16 feedback

÷20 feedback

÷24 feedback

÷32 feedback

÷40 feedback

PLL bypass mode

50.0

33.3

25.0

20.0

16.6

12.5

10.0

8.33

6.25

5.00

120

80.0

60.0

48.0

40.0

30.0

24.0

20.0

15.0

12.0

250

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

fVCO

VCO frequency range

200 480 MHz

fMAX

Output frequencya

÷2 output

÷4 output

÷6 output

÷8 output

÷10 output

÷12 output

÷16 output

÷20 output

÷24 output

100.0

50.0

33.3

25.0

20.0

16.6

12.5

10.0

8.33

240.0

120.0

80.0

60.0

48.0

40.0

30.0

24.0

20.0

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

fSTOP_CLK Serial interface frequency

20.0

MHz

VPP Peak to Peak Input Voltage

PECL and PECL

LVPECL

400

1000

mV

VCMR

Common Mode Range PECL

and PECL

LVPECL

1.2

VDD - 0.9

V

tPW CLKx pulse width

2.0 ns

ItR, ItF

Input CLKx Rise/Fall time

0.8V to 2.0V

1 ns

t(∅)

Propagation Delay (static 6.25MHz < fREF < 65.0MHz

-3

phase offset) CLKx to FB_INb 65.0MHz < fREF < 125MHz

-4

fREF = 50MHz & FB = ÷8

-166

+3

+4

+166

°

°

ps

tSK(O)

Output to output skew

Bank A (QAx to QAy)

Bank B (QBx to QBy)

Bank C (QCx to QCy)

all outputs (QXy to QWz)c

100 ps

100 ps

100 ps

250 ps

DC Output duty cycled

(T÷2)-200 T÷2 (T÷2)+200 ps

OtR, OtF

Output Rise/Fall time

0.55 to 2.4V

0.1

1.0 ns

5

5 Page

REV. P1.0.0

PACKAGE DIMENSIONS

PRELIMINARY

XRK69773

E 1:12 LVCMOS PLL CLOCK GENERATOR

52 LEAD LOW-PROFILE QUAD FLAT PACK

(10 mm x 10 mm X 1.4 mm LQFP, 1.0 mm Form)

Rev. 1.00

Note: The control dimension is in millimeters.

SYMBOL

A

A1

A2

B

C

D

D1

e

L

α

INCHES

MIN MAX

0.055

0.063

0.002

0.006

0.053

0.057

0.010

0.014

0.004

0.009

0.465

0.480

0.390

0.398

0.0256 BSC

0.029

0.041

0° 7°

MILLIMETERS

MIN MAX

1.40 1.60

0.05 0.15

1.35 1.45

0.25 0.35

0.11 0.23

11.80

12.20

9.90 10.10

0.65 BSC

0.73 1.03

0° 7°

α

11

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet XRK69773.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XRK69772 | 1:12 LVCMOS PLL CLOCK GENERATOR | Exar Corporation |

| XRK69773 | 1:12 LVCMOS PLL CLOCK GENERATOR | Exar Corporation |

| XRK69774 | 1:14 LVCMOS PLL CLOCK GENERATOR | Exar Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |