|

|

PDF XRT83SL314 Data sheet ( Hoja de datos )

| Número de pieza | XRT83SL314 | |

| Descripción | 14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT | |

| Fabricantes | Exar Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XRT83SL314 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

PRELIMINARY

XRT83SL314

NOVEMBER 2003

14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT

REV. P1.0.5

GENERAL DESCRIPTION

The XRT83SL314 is a fully integrated 14-channel

short-haul line interface unit (LIU) that operates from

a single 3.3V power supply. Using internal

termination, the LIU provides one bill of materials to

operate in T1, E1, or J1 mode independently on a per

channel basis with minimum external components.

The LIU features are programmed through a standard

microprocessor interface. EXAR’s LIU has patented

high impedance circuits that allow the transmitter

outputs and receiver inputs to be high impedance

when experiencing a power failure or when the LIU is

powered off. Key design features within the LIU

optimize 1:1 or 1+1 redundancy and non-intrusive

monitoring applications to ensure reliability without

using relays.

The on-chip clock synthesizer generates T1/E1/J1

clock rates from a selectable external clock frequency

and has five output clock references that can be used

for external timing (8kHz, 1.544Mhz, 2.048Mhz, nxT1/

J1, nxE1).

Additional features include RLOS, a 16-bit LCV

counter for each channel, AIS, QRSS generation/

detection, Network Loop Code generation/detection,

TAOS, DMO, and diagnostic loopback modes.

APPLICATIONS

• T1 Digital Cross Connects (DSX-1)

• ISDN Primary Rate Interface

• CSU/DSU E1/T1/J1 Interface

• T1/E1/J1 LAN/WAN Routers

• Public Switching Systems and PBX Interfaces

• T1/E1/J1 Multiplexer and Channel Banks

• Integrated Multi-Service Access Platforms (IMAPs)

• Integrated Access Devices (IADs)

• Inverse Multiplexing for ATM (IMA)

• Wireless Base Stations

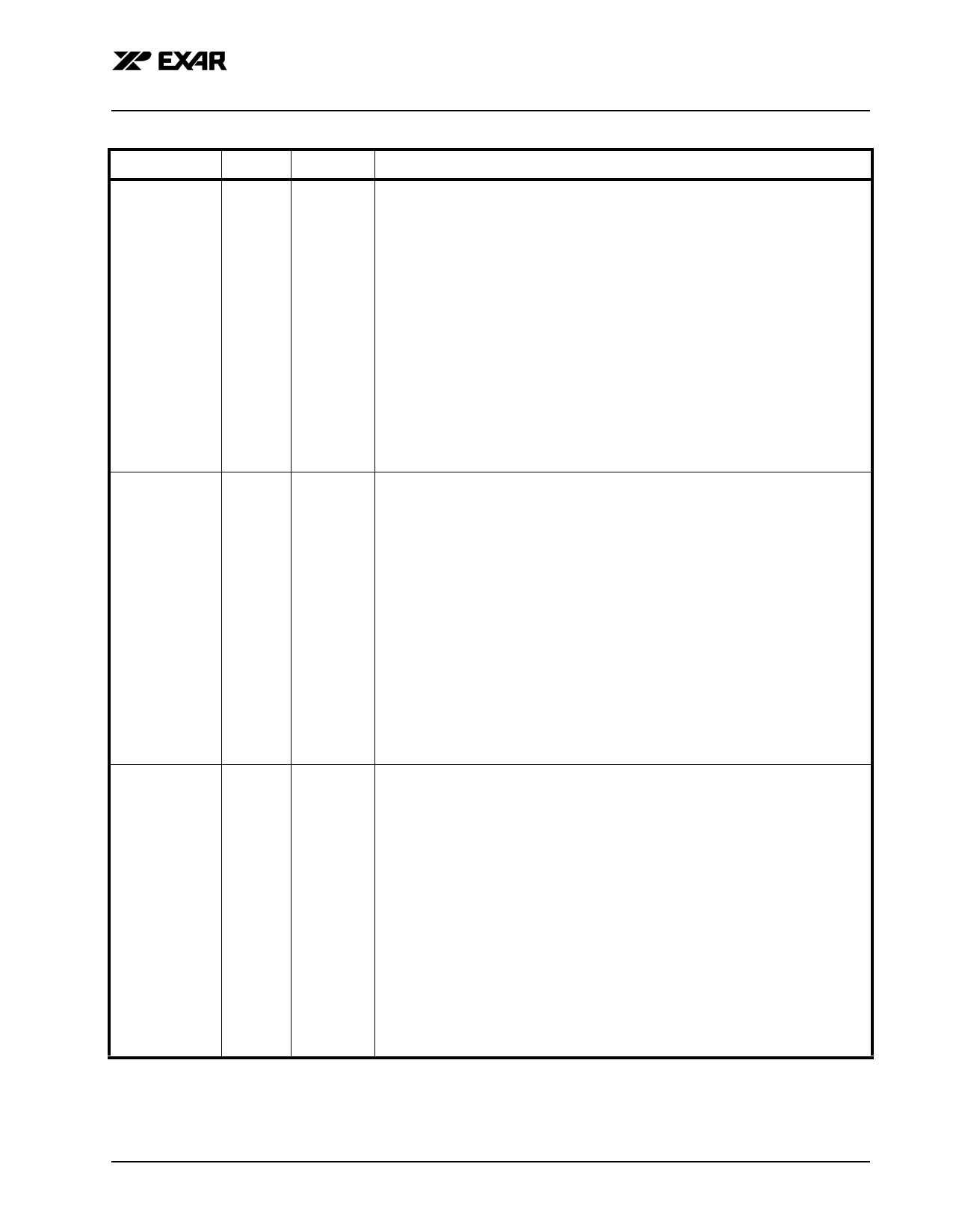

FIGURE 1. BLOCK DIAGRAM OF THE XRT83SL314

TCLK

TPOS

TNEG

RCLK

RPOS

RNEG

ICT

TEST

TxON

1 of 14 Channels

NLCD

Generation

Driver

Monitor

HDB3/B8ZS

Encoder

Tx Jitter

Attenuator

Timing

Control

Tx Pulse

Shaper &

Pattern Gen

Remote

Loopback

Digital

Loopback

QRSS

Generation

& Detection

Line

Driver

Analog

Loopback

HDB3/B8ZS

Decoder

Rx Jitter

Attenuator

Clock & Data

Recovery

NLCD

Detection

AIS & LOS

Detector

Peak

Detector

& Slicer

Rx

Equalizer

Rx Equalizer

Control

Test

Microprocessor

Interface

Programmable Master

Clock Synthesizer

TTIP

TRING

RTIP

RRING

DMO

RLOS

8kHzOUT

MCLKE1out

MCLKT1out

MCLKE1Nout

MCLKT1Nout

RxON

RxTSEL

Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

1 page

PRELIMINARY

XRT83SL314

14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT

REV. P1.0.5

FIGURE 17. DUAL RAIL MODE WITH A FIXED REPEATING "0011" PATTERN ............................................................................................ 25

2.10 RXMUTE (RECEIVER LOS WITH DATA MUTING) ..................................................................................... 25

FIGURE 18. SIMPLIFIED BLOCK DIAGRAM OF THE RXMUTE FUNCTION................................................................................................... 25

3.0 TRANSMIT PATH LINE INTERFACE ................................................................................................. 26

FIGURE 19. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT PATH ......................................................................................................... 26

3.1 TCLK/TPOS/TNEG DIGITAL INPUTS ............................................................................................................ 26

FIGURE 20. TRANSMIT DATA SAMPLED ON FALLING EDGE OF TCLK...................................................................................................... 26

FIGURE 21. TRANSMIT DATA SAMPLED ON RISING EDGE OF TCLK........................................................................................................ 26

3.2 HDB3/B8ZS ENCODER .................................................................................................................................. 27

TABLE 7: TIMING SPECIFICATIONS FOR TCLK/TPOS/TNEG.................................................................................................................. 27

TABLE 8: EXAMPLES OF HDB3 ENCODING ............................................................................................................................................ 27

TABLE 9: EXAMPLES OF B8ZS ENCODING............................................................................................................................................. 27

3.3 TRANSMIT JITTER ATTENUATOR ............................................................................................................... 28

3.4 TAOS (TRANSMIT ALL ONES) ..................................................................................................................... 28

FIGURE 22. TAOS (TRANSMIT ALL ONES) ............................................................................................................................................ 28

3.5 TRANSMIT DIAGNOSTIC FEATURES .......................................................................................................... 28

TABLE 10: MAXIMUM GAP WIDTH FOR MULTIPLEXER/MAPPER APPLICATIONS......................................................................................... 28

3.5.1 ATAOS (AUTOMATIC TRANSMIT ALL ONES)......................................................................................................... 29

FIGURE 23. SIMPLIFIED BLOCK DIAGRAM OF THE ATAOS FUNCTION ..................................................................................................... 29

3.5.2 NETWORK LOOP UP CODE...................................................................................................................................... 29

FIGURE 24. NETWORK LOOP UP CODE GENERATION ............................................................................................................................ 29

3.5.3 NETWORK LOOP DOWN CODE ............................................................................................................................... 29

FIGURE 25. NETWORK LOOP DOWN CODE GENERATION ....................................................................................................................... 29

3.5.4 QRSS GENERATION.................................................................................................................................................. 30

3.6 TRANSMIT PULSE SHAPER AND FILTER ................................................................................................... 30

TABLE 11: RANDOM BIT SEQUENCE POLYNOMIALS................................................................................................................................ 30

3.6.1 T1 SHORT HAUL LINE BUILD OUT (LBO) ............................................................................................................... 31

3.6.2 ARBITRARY PULSE GENERATOR FOR T1 AND E1............................................................................................... 31

FIGURE 26. ARBITRARY PULSE SEGMENT ASSIGNMENT ......................................................................................................................... 31

3.7 DMO (DIGITAL MONITOR OUTPUT) ............................................................................................................. 31

TABLE 12: SHORT HAUL LINE BUILD OUT.............................................................................................................................................. 31

3.8 LINE TERMINATION (TTIP/TRING) ............................................................................................................... 32

FIGURE 27. TYPICAL CONNECTION DIAGRAM USING INTERNAL TERMINATION ......................................................................................... 32

4.0 T1/E1 APPLICATIONS ........................................................................................................................ 33

4.1 LOOPBACK DIAGNOSTICS .......................................................................................................................... 33

4.1.1 LOCAL ANALOG LOOPBACK .................................................................................................................................. 33

FIGURE 28. SIMPLIFIED BLOCK DIAGRAM OF LOCAL ANALOG LOOPBACK................................................................................................ 33

4.1.2 REMOTE LOOPBACK ................................................................................................................................................ 33

FIGURE 29. SIMPLIFIED BLOCK DIAGRAM OF REMOTE LOOPBACK .......................................................................................................... 33

4.1.3 DIGITAL LOOPBACK ................................................................................................................................................. 34

FIGURE 30. SIMPLIFIED BLOCK DIAGRAM OF DIGITAL LOOPBACK ........................................................................................................... 34

4.1.4 DUAL LOOPBACK ..................................................................................................................................................... 34

FIGURE 31. SIMPLIFIED BLOCK DIAGRAM OF DUAL LOOPBACK ............................................................................................................... 34

4.2 84-CHANNEL T1/E1 MULTIPLEXER/MAPPER APPLICATIONS ................................................................. 35

FIGURE 32. SIMPLIFIED BLOCK DIAGRAM OF AN 84-CHANNEL APPLICATION ........................................................................................... 35

TABLE 13: CHIP SELECT ASSIGNMENTS ................................................................................................................................................ 35

4.3 LINE CARD REDUNDANCY .......................................................................................................................... 36

4.3.1 1:1 AND 1+1 REDUNDANCY WITHOUT RELAYS .................................................................................................... 36

4.3.2 TRANSMIT INTERFACE WITH 1:1 AND 1+1 REDUNDANCY .................................................................................. 36

FIGURE 33. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR 1:1 AND 1+1 REDUNDANCY ................................................ 36

4.3.3 RECEIVE INTERFACE WITH 1:1 AND 1+1 REDUNDANCY..................................................................................... 36

FIGURE 34. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR 1:1 AND 1+1 REDUNDANCY.................................................. 37

4.3.4 N+1 REDUNDANCY USING EXTERNAL RELAYS ................................................................................................... 37

4.3.5 TRANSMIT INTERFACE WITH N+1 REDUNDANCY ................................................................................................ 38

FIGURE 35. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N+1 REDUNDANCY ............................................................ 38

4.3.6 RECEIVE INTERFACE WITH N+1 REDUNDANCY ................................................................................................... 39

FIGURE 36. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR N+1 REDUNDANCY .............................................................. 39

4.4 POWER FAILURE PROTECTION .................................................................................................................. 40

4.5 OVERVOLTAGE AND OVERCURRENT PROTECTION ............................................................................... 40

4.6 NON-INTRUSIVE MONITORING .................................................................................................................... 40

FIGURE 37. SIMPLIFIED BLOCK DIAGRAM OF A NON-INTRUSIVE MONITORING APPLICATION ..................................................................... 40

4.7 XRT83SL314 JITTER CHARACTERISTICS .................................................................................................. 40

4.7.1 INTRINSIC JITTER...................................................................................................................................................... 40

II

5 Page

PRELIMINARY

RECEIVER SECTION

NAME

PIN

RNEG13

RNEG12

RNEG11

RNEG10

RNEG9

RNEG8

RNEG7

RNEG6

RNEG5

RNEG4

RNEG3

RNEG2

RNEG1

RNEG0

AA14

Y21

P21

N21

H21

G21

C14

C10

F3

G3

N3

P3

Y3

AA10

RTIP13

RTIP12

RTIP11

RTIP10

RTIP9

RTIP8

RTIP7

RTIP6

RTIP5

RTIP4

RTIP3

RTIP2

RTIP1

RTIP0

AC14

Y23

T23

P23

G23

E23

A14

A9

E1

G1

P1

T1

Y1

AC9

RRING13

RRING12

RRING11

RRING10

RRING9

RRING8

RRING7

RRING6

RRING5

RRING4

RRING3

RRING2

RRING1

RRING0

AC13

W23

U23

N23

H23

D23

A13

A10

D1

H1

N1

U1

W1

AC10

XRT83SL314

14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT

REV. P1.0.5

TYPE

O

DESCRIPTION

RNEG/LCV_OF Output

In dual rail mode, this pin is the receive negative data output. In single rail

mode, this pin is a Line Code Violation / Counter Overflow indicator. If LCV is

selected by programming the appropriate global register and if a line code vio-

lation, a bi-polar violation, or excessive zeros occur, the LCV pin will pull "High"

for a minimum of one RCLK cycle. LCV will remain "High" until there are no

more violations. However, if OF is selected the LCV pin will pull "High" if the

internal LCV counter is saturated. The LCV pin will remain "High" until the LCV

counter is reset.

I Receive Differential Tip Input

RTIP is the positive differential input from the line interface. Along with the

RRING signal, these pins should be coupled to a 1:1 transformer for proper

operation.

I Receive Differential Ring Input

RRING is the negative differential input from the line interface. Along with the

RTIP signal, these pins should be coupled to a 1:1 transformer for proper oper-

ation.

6

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet XRT83SL314.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XRT83SL314 | 14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT | Exar Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |