|

|

PDF IR3500 Data sheet ( Hoja de datos )

| Número de pieza | IR3500 | |

| Descripción | Complete VR11.0 or AMD PVID power solution | |

| Fabricantes | International Rectifier | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IR3500 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

IR3500

DATA SHEET

XPHASE3TM VR11.0 & AMD PVID CONTROL IC

DESCRIPTION

The IR3500 Control IC combined with an xPHASE3TM Phase IC provides a full featured and flexible way to

implement a complete VR11.0 or AMD PVID power solution. The Control IC provides overall system

control and interfaces with any number of Phase ICs which each drive and monitor a single phase of a

multiphase converter. The XPhase3TM architecture implements a power supply that is smaller, less

expensive, and easier to design while providing higher efficiency than conventional approaches.

FEATURES

• 1 to X phase operation with matching Phase IC

• VID Select pin configures AMD 5 or 6 bit PVID, Intel VR11 with/out startup to 1.1V Boot voltage

• 0.5% overall system set point accuracy

• Programmable 250kHz to 9MHz Daisy-chain digital phase timing clock oscillator frequency provides a

per phase switching frequency of 250kHz to 1.5MHz without external components

• Programmable Dynamic VID Slew Rate

• Programmable VID Offset or No Offset

• Programmable Load Line Output Impedance

• High speed error amplifier with wide bandwidth of 30MHz and fast slew rate of 12V/us

• Programmable converter current limit during soft start, hiccup with delay during normal operation

• Central over voltage detection with programmable threshold and communication to phase ICs

• Over voltage signal output to system with overvoltage detection during powerup and normal operation

• Detection and protection of open remote sense line and open control loop

• IC bias linear regulator control with programmable output voltage and UVLO

• Programmable VRHOT function monitors temperature of power stage through a NTC thermistor

• Remote sense amplifier with true converter voltage sensing and less than 50uA bias current

• Simplified VR Ready output provides indication of proper operation and avoids false triggering

• Small thermally enhanced 32L 5mm x 5mm MLPQ package

12V

VR READY

VIDSEL

Q1

R VC C LD R V

RVCCLFB1 RVCCLFB2

Optional

FUSE

C VC C L

4.7uF

ROVP1

Q3

Q2

SCR

R OVP2

To Converter

VCCL

VID7

VID6

VID5

VID4

VID3

VID2

VID1

VID0

ENABLE

VRHOT

1

VI D 7

2 VID6

3 VID5

4 VID4

5 VID3

6

VI D 2

7 VID1

8 VID0

IR3500

CONTROL

IC

LGND

ROSC / OVP

SS/ D EL

VD AC

OCSET

VSETPT

IIN

VD R P

24

23

22

21

20

19

18

17

R OSC

CSS/ DEL

R VD AC

ROCSET

RVSETPT

C VD AC

VDAC

RTHERMISTOR2 RHOTSET2

R TH ER MI STOR 1

Close to

Power Stage

RHOTSET1

VC C L

RFB1 CFB

RFB

CDRP

RDRP

RCP

CCP

C C P1

RFB2

Figure 1 – Application Circuit

6 Wire

Bus to

Phase

ICs

VCC SENSE +

To Load

VSS SENSE -

Page 1 of 47

June 12, 2007

1 page

www.DataSheet4U.com

IR3500

PARAMETER

TEST CONDITION

Minimum Voltage

Maximum Voltage

Measure V(VCCL) – V(EAOUT)

Open Voltage Loop Detection

Threshold

Measure V(VCCL) - V(EAOUT),

Relative to Error Amplifier maximum

voltage.

Open Voltage Loop Detection Measure PHSOUT pulse numbers from

Delay

V(EAOUT) = V(VCCL) to VRRDY = low.

Enable Input

VR 11 Threshold Voltage

ENABLE rising

VR 11 Threshold Voltage

ENABLE falling

VR 11 Hysteresis

AMD Threshold Voltage

ENABLE rising

AMD Threshold Voltage

ENABLE falling

AMD Hysteresis

Bias Current

0V ≤ V(ENABLE) ≤ 3.3V

Blanking Time

Noise Pulse < 100ns will not register an

ENABLE state change. Note 1

Over-Current Comparator

Input Offset Voltage

1V ≤ V(OCSET) ≤ 3.3V

OCSET Bias Current

ROSC= 24.5 KΩ

Over-Current Delay Counter ROSC = 7.75 KΩ (PHSOUT=1.5MHz)

Over-Current Delay Counter ROSC = 15.0 KΩ (PHSOUT=800kHZ)

Over-Current Delay Counter ROSC = 50.0 KΩ (PHSOUT=250kHz)

Over-Current Limit Amplifier

Input Offset Voltage

Transconductance

Note 1

Sink Current

Unity Gain Bandwidth

Over Voltage Protection (OVP) Comparators

Threshold at Power-up

Threshold during Normal

Operation

Compare to V(VDAC)

OVP Release Voltage during

Normal Operation

Compare to V(VDAC)

Threshold during Dynamic VID

down

Dynamic VID Detect

Comparator Threshold

Propagation Delay to IIN

Measure time from V(VO) > V(VDAC)

(250mV overdrive) to V(IIN) transition to

> 0.9 * V(VCCL).

IIN Pull-up Resistance

Propagation Delay to OVP

Measure time from V(VO) > V(VDAC)

(250mV overdrive) to V(ROSC/OVP)

transition to >1V.

OVP High Voltage

Measure V(VCCL)-V(ROSC/OVP)

OVP Power-up High Voltage

V(VCCLDRV)=1.8V. Measure V(VCCL)-

V(ROSC/OVP)

MIN

500

125

825

775

25

1.1

1.05

30

-5

75

-30

23.25

-10

0.50

35

0.75

1.60

105

-13

1.70

25

0

0

TYP

120

780

300

8

850

800

50

1.2

1.14

50

0

250

-13

24.50

4096

2048

1024

0

1.00

55

2.00

1.73

125

3

1.73

50

90

5

90

MAX

250

950

600

UNIT

mV

mV

mV

Pulses

875

825

75

1.3

1.23

80

5

400

mV

mV

mV

V

V

mV

µA

ns

0

25.75

mV

µA

Cycle

Cycle

Cycle

10

1.75

75

3.00

mV

mA/V

uA

kHz

1.83

145

20

1.75

75

180

V

mV

mV

V

mV

ns

15 Ω

300 ns

1.2 V

0.2 V

Page 5 of 47

June 12, 2007

5 Page

www.DataSheet4U.com

IR3500

most systems. The inductor current will increase much more rapidly than decrease in response to load transients.

An additional advantage of the architecture is that differences in ground or input voltage at the phases have no

effect on operation since the PWM ramps are referenced to VDAC. Figure 6 depicts PWM operating waveforms

under various conditions.

The error amplifier is a high speed amplifier with 110 dB of open loop gain. It is not unity gain stable.

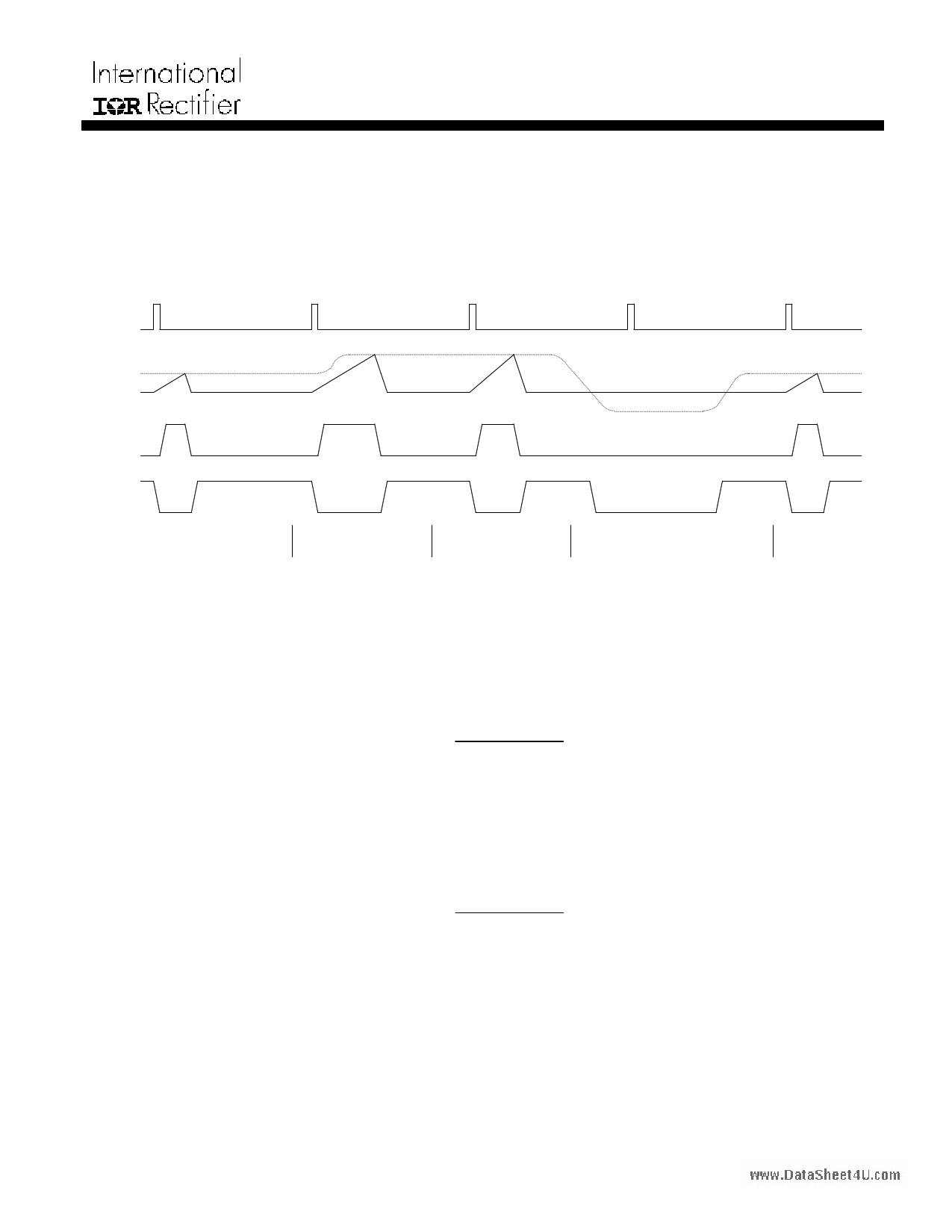

PHASE IC

CLOCK

PULSE

EAIN

PWMRMP

VDAC

GATEH

GATEL

STEADY-STATE

OPERATION

DUTY CYCLE INCREASE

DUE TO LOAD

INCREASE

DUTY CYCLE DECREASE

DUE TO VIN INCREASE

(FEED-FORWARD)

DUTY CYCLE DECREASE DUE TO LOAD

DECREASE (BODY BRAKING) OR FAULT

(VCC UV, OCP, VID FAULT)

STEADY-STATE

OPERATION

Figure 6 - PWM Operating Waveforms

Body BrakingTM

In a conventional synchronous buck converter, the minimum time required to reduce the current in the inductor in

response to a load step decrease is;

TSLEW

=

L * (IMAX − IMIN )

VO

The slew rate of the inductor current can be significantly increased by turning off the synchronous rectifier in

response to a load step decrease. The switch node voltage is then forced to decrease until conduction of the

synchronous rectifier’s body diode occurs. This increases the voltage across the inductor from Vout to Vout +

VBODYDIODE. The minimum time required to reduce the current in the inductor in response to a load transient

decrease is now;

TSLEW

=

L * (IMAX − IMIN )

VO + VBODYDIODE

Since the voltage drop in the body diode is often comparable to the output voltage, the inductor current slew rate

can be increased significantly. This patented method is referred to as “body braking” and is accomplished through

the “body braking comparator” located in the phase IC. If the error amplifier’s output voltage drops below the output

voltage of the share adjust amplifier in the phase IC, this comparator turns off the low side gate driver.

Lossless Average Inductor Current Sensing

Inductor current can be sensed by connecting a series resistor and a capacitor network in parallel with the inductor

and measuring the voltage across the capacitor, as shown in Figure 7. The equation of the sensing network is,

Page 11 of 47

June 12, 2007

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet IR3500.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IR350 | Receiver Pre-amp Module | ETC |

| IR3500 | Complete VR11.0 or AMD PVID power solution | International Rectifier |

| IR3502 | CONTROL IC | International Rectifier |

| IR3505 | Phase IC combined | International Rectifier |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |