|

|

PDF 56F8123 Data sheet ( Hoja de datos )

| Número de pieza | 56F8123 | |

| Descripción | (56F8123 / 56F8323) 16-bit Digital Signal Controllers | |

| Fabricantes | Freescale Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 56F8123 (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

56F8323/56F8123

Data Sheet

Preliminary Technical Data

56F8300

16-bit Digital Signal Controllers

www.DataSheet4U.com

MC56F8323

Rev. 17

04/2007

freescale.com

1 page

56F8323/56F8123 General Description

Note: Features in italics are NOT available in the 56F8123 device.

• Up to 60 MIPS at 60MHz core frequency

• DSP and MCU functionality in a unified,

C-efficient architecture

• 32KB Program Flash

• 4KB Program RAM

• 8KB Data Flash

• 8KB Data RAM

• 8KB Boot Flash

• One 6-channel PWM module

• Two 4-channel 12-bit ADCs

• Temperature Sensor

• One Quadrature Decoder

• One FlexCAN module

• Up to two Serial Communication Interfaces (SCIs)

• Up to two Serial Peripheral Interfaces (SPIs)

• Two general-purpose Quad Timers

• Computer Operating Properly (COP)/Watchdog

• On-Chip Relaxation Oscillator

• JTAG/Enhanced On-Chip Emulation (OnCE™) for

unobtrusive, real-time debugging

• Up to 27 GPIO lines

• 64-pin LQFP Package

RESET

OCR_DIS VCAP VDD VSS VDDA VSSA

5 4 44 2

3

3

6 PWM Outputs

PWMA or

Current Sense Inputs SPI1 or

Fault Inputs

GPIOA

JTAG/

EOnCE

Port

Digital Reg Analog Reg

16-Bit

56800E Core

Low Voltage

Supervisor

Program Controller

Address

and Hardware Generation Unit

Looping Unit

Data ALU

16 x 16 + 36 −> 36-Bit MAC

Three 16-bit Input Registers

Bit

Manipulation

Unit

Four 36-bit Accumulators

4 AD0

4 AD1

Memory

XDB2

5 VREF

Program Memory

16K x 16 Flash

XAB1

XAB2

TEMP_SENSE 2K x 16 RAM

PAB

4K x 16 Boot

Flash

PDB

CDBR

Quadrature

Data Memory

CDBW

4 Decoder 0 or 4K x 16 Flash

Quad

4K x 16 RAM

Timer A or

GPIO B

PAB

PDB

CDBR

CDBW

R/W Control

System Bus

Control

IPBus Bridge (IPBB)

Quad

3 Timer C or

SCI0 or

GPIOC Decoding

Peripheral

Device Selects

RW IPAB IPWDB

Control

IPRDB

2 FlexCAN or Peripherals

GPIOC

Clock

resets

PLL

SPI0 or

SCI1 or

GPIOB

4

COP/

Interrupt

Watchdog Controller

IRQA

System

P

O

Integration R

Module

Clock

Generator*

O

S

C

XTAL or GPIOC

EXTAL or GPIOC

*Includes On-Chip

Relaxation Oscillator

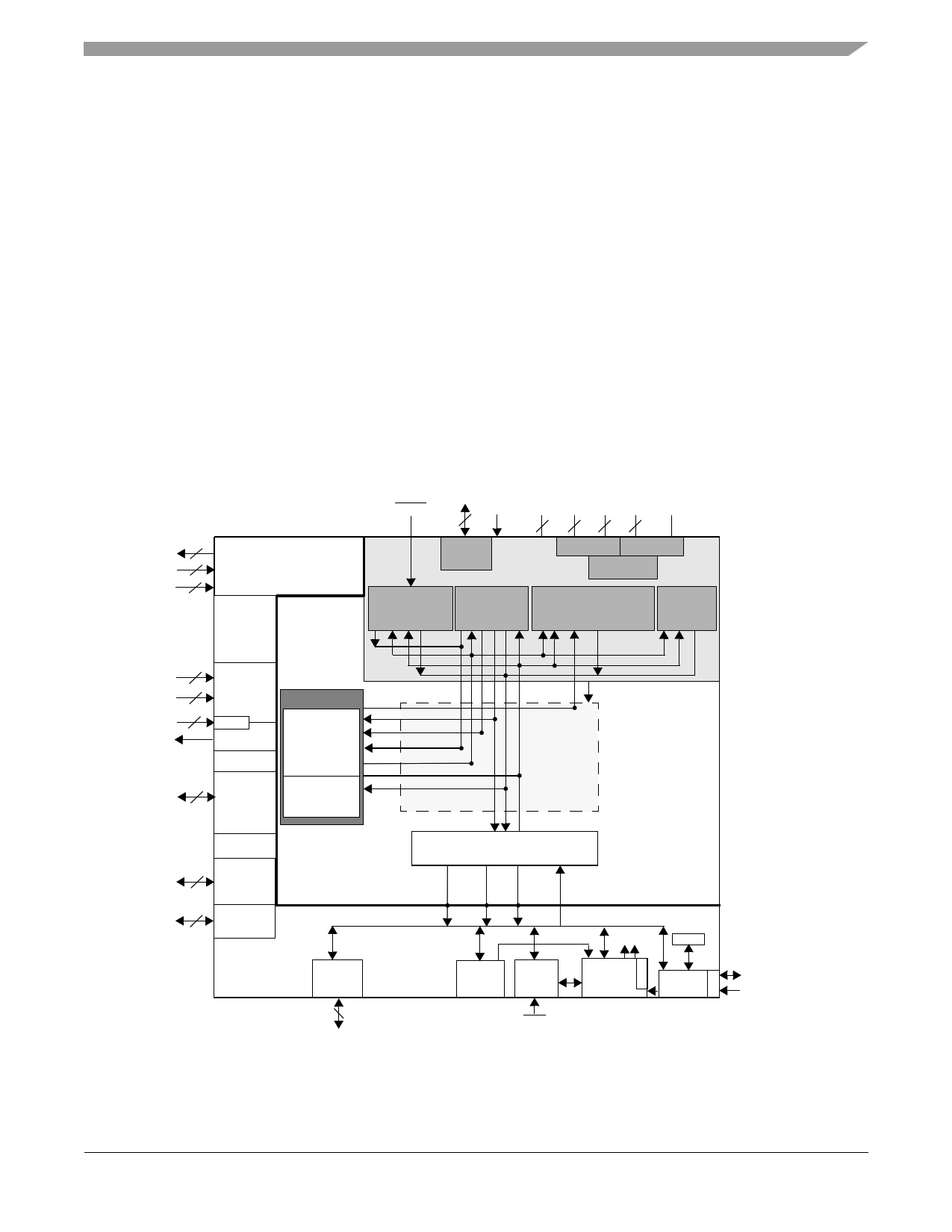

56F8323/56F8123 Block Diagram

Freescale Semiconductor

Preliminary

56F8323 Technical Data, Rev. 17

5

5 Page

Architecture Block Diagram

1.4 Architecture Block Diagram

Note: Features in italics are NOT available in the 56F8123 device and are shaded in the following figures.

The 56F8323/56F8123 architecture is shown in Figure 1-1 and Figure 1-2. Figure 1-1 illustrates how the

56800E system buses communicate with internal memories and the IPBus Bridge. Table 1-2 lists the

internal buses in the 56800E architecture and provides a brief description of their function. Figure 1-2

shows the peripherals and control blocks connected to the IPBus Bridge. The figures do not show the

on-board regulator and power and ground signals. They also do not show the multiplexing between

peripherals or the dedicated GPIOs. Please see Part 2 Signal/Connection Descriptions, to see which

signals are multiplexed with those of other peripherals.

Also shown in Figure 1-2 are connections between the PWM, Timer C and ADC blocks. These

connections allow the PWM and/or Timer C to control the timing of the start of ADC conversions. The

Timer C, Channel 2, output can generate periodic start (SYNC) signals to the ADC to start its conversions.

In another operating mode, the PWM load interrupt (SYNC output) signal is routed internally to the Timer

C, Channel 2, input as indicated. The timer can then be used to introduce a controllable delay before

generating its output signal. The timer output then triggers the ADC. To fully understand this interaction,

please see the 56F8300 Peripheral User Manual for clarification on the operation of all three of these

peripherals.

Freescale Semiconductor

Preliminary

56F8323 Technical Data, Rev. 17

11

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet 56F8123.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 56F8122 | 16-bit Hybrid Controllers | Motorola Inc |

| 56F8123 | (56F8123 / 56F8323) 16-bit Digital Signal Controllers | Freescale Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |