|

|

PDF HI5767 Data sheet ( Hoja de datos )

| Número de pieza | HI5767 | |

| Descripción | A/D Converter | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HI5767 (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

®

Data Sheet

March 30, 2005

HI5767

FN4319.6

10-Bit, 20/40/60MSPS A/D Converter with

Internal Voltage Reference

The HI5767 is a monolithic, 10-bit, analog-to-digital

converter fabricated in a CMOS process. It is designed for

high speed applications where wide bandwidth and low

power consumption are essential. Its high sample clock

rate is made possible by a fully differential pipelined

architecture with both an internal sample and hold and

internal band-gap voltage reference.

The 250MHz Full Power Input Bandwidth and superior high

frequency performance of the HI5767 converter make it an

excellent choice for implementing Digital IF architectures in

communications applications.

The HI5767 has excellent dynamic performance while

consuming only 310mW power at 40MSPS. Data output

latches are provided which present valid data to the output

bus with a latency of 7 clock cycles.

The HI5767 is offered in 20MSPS, 40MSPS and 60MSPS

sampling rates.

Pinout

www.DataSheet4U.com

HI5767 (SOIC, SSOP)

TOP VIEW

DVCC1 1

DGND 2

DVCC1 3

DGND 4

AVCC 5

AGND 6

VREFIN 7

VREFOUT 8

VIN+ 9

VIN- 10

VDC 11

AGND 12

AVCC 13

OE 14

28 D0

27 D1

26 D2

25 D3

24 D4

23 DVCC2

22 CLK

21 DGND

20 D5

19 D6

18 D7

17 D8

16 D9

15 DFS

Features

• Sampling Rate . . . . . . . . . . . . . . . . . . . . . . 20/40/60MSPS

• 8.8 Bits at fIN = 10MHz, fS = 40MSPS

• Low Power at 40MSPS . . . . . . . . . . . . . . . . . . . . .310mW

• Wide Full Power Input Bandwidth . . . . . . . . . . . . 250MHz

• On-Chip Sample and Hold

• Internal 2.5V Band-Gap Voltage Reference

• Fully Differential or Single-Ended Analog Input

• Single Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . .+5V

• TTL/CMOS Compatible Digital Inputs

• CMOS Compatible Digital Outputs. . . . . . . . . . . 3.0V/5.0V

• Offset Binary or Two’s Complement Output Format

• Pb-Free Available (RoHS Compliant)

Applications

• Digital Communication Systems

• QAM Demodulators

• Professional Video Digitizing

• Medical Imaging

• High Speed Data Acquisition

1 CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2003, 2005. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

1 page

HI5767

Absolute Maximum Ratings TA = 25oC

Supply Voltage, AVCC or DVCC to AGND or DGND . . . . . . . . . . .6V

DGND to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.3V

Digital I/O Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . DGND to DVCC

Analog I/O Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . AGND to AVCC

Operating Conditions

Temperature Range

HI5767/xCx. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0oC to 70oC

HI5767/xIx . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -40oC to 85oC

Thermal Information

Thermal Resistance (Typical, Note 1)

θJA (oC/W)

SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

75

SSOP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . .

100

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . .150oC

Maximum Storage Temperature Range . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . .300oC

(SOIC - Lead Tips Only)

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications

AVCC = DVCC1 = 5.0V, DVCC2 = 3.0V; VREFIN = VREFOUT; fS = 40MSPS at 50% Duty Cycle;

CL = 10pF; TA = 25oC; Differential Analog Input; Typical Values are Test Results at 25oC,

Unless Otherwise Specified

PARAMETER

TEST CONDITIONS

MIN TYP MAX

ACCURACY

Resolution

10 -

-

Integral Linearity Error, INL

Differential Linearity Error, DNL

(Guaranteed No Missing Codes)

fIN = 1MHz Sinewave

fIN = 1MHz Sinewave

-

±0.75

±1.75

-

±0.35

±1.0

Offset Error, VOS

Full Scale Error, FSE

DYNAMIC CHARACTERISTICS

fIN = DC

fIN = DC

-40 - 40

-4-

Minimum Conversion Rate

No Missing Codes

- 0.5 1

Maximum Conversion Rate

HI5767/2

No Missing Codes

20 -

-

HI5767/4

No Missing Codes

40 -

-

HI5767/6

No Missing Codes

60 -

-

Effective Number of Bits, ENOB

HI5767/2

HI5767/4

HI5767/6

Signal to Noise and Distortion Ratio, SINAD

= ----------------R----M-----S------S----i-g----n---a---l---------------

RMS Noise + Distortion

HI5767/2

HI5767/4

HI5767/6

Signal to Noise Ratio, SNR

= R-----M-----S------S----i-g---n----a---l

RMS Noise

HI5767/2

HI5767/4

HI5767/6

Total Harmonic Distortion, THD

HI5767/2

fS = 20MSPS, fIN = 10MHz

fS = 40MSPS, fIN = 10MHz

fS = 60MSPS, fIN = 10MHz

fS = 20MSPS, fIN = 10MHz

fS = 40MSPS, fIN = 10MHz

fS = 60MSPS, fIN = 10MHz

fS = 20MSPS, fIN = 10MHz

fS = 40MSPS, fIN = 10MHz

fS = 60MSPS, fIN = 10MHz

fS = 20MSPS, fIN = 10MHz

8.7

8.55

8.1

9

8.8

8.4

-

-

-

- 55.9 -

- 54.7 -

- 53.8 -

- 55.9 -

- 55 -

- 54 -

- -71 -

UNITS

Bits

LSB

LSB

LSB

LSB

MSPS

MSPS

MSPS

MSPS

Bits

Bits

Bits

dB

dB

dB

dB

dB

dB

dBc

5

5 Page

HI5767

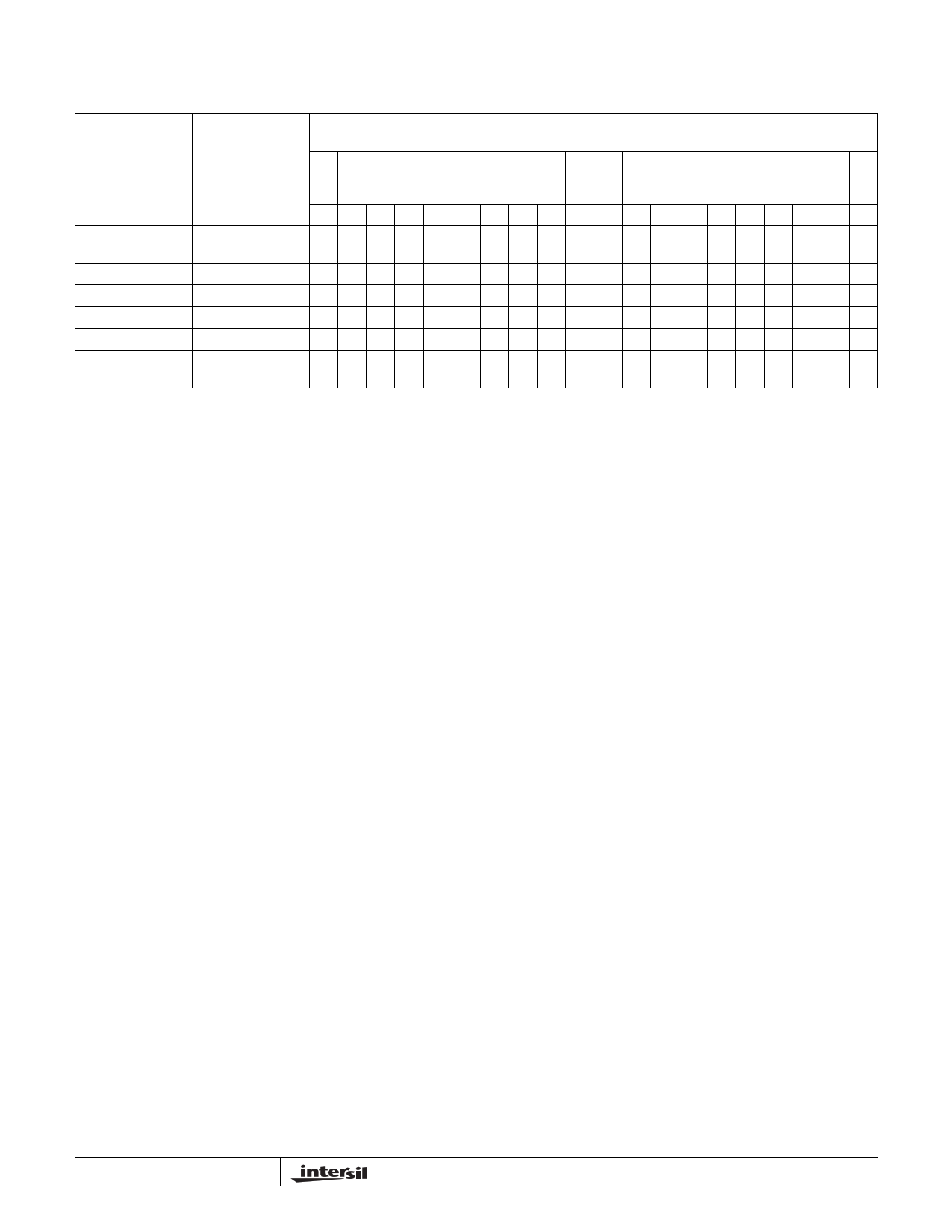

TABLE 1. A/D CODE TABLE

OFFSET BINARY OUTPUT CODE

(DFS LOW)

TWO’S COMPLEMENT OUTPUT CODE

(DFS HIGH)

CODE CENTER

DESCRIPTION

M LM L

DIFFERENTIAL S

INPUT VOLTAGE B

SS

BB

S

B

(VIN+ - VIN-) D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

+Full Scale (+FS) -

1/4 LSB

+FS - 11/4 LSB

+3/4 LSB

-1/4 LSB

-FS + 13/4 LSB

0.499756V

0.498779V

732.422µV

-244.141µV

-0.498291V

11111111110111111111

11111111100111111110

10000000000000000000

01111111111111111111

00000000011000000001

-Full Scale (-FS) +

3/4 LSB

-0.499268V

00000000001000000000

NOTE:

4. The voltages listed above represent the ideal center of each output code shown with VREFIN = +2.5V.

Detailed Description

Theory of Operation

The HI5767 is a 10-bit fully differential sampling pipeline A/D

converter with digital error correction logic. Figure 16 depicts

the circuit for the front end differential-in-differential-out sample-

and-hold (S/H). The switches are controlled by an internal

sampling clock which is a non-overlapping two phase signal, Φ1

and Φ2, derived from the master sampling clock. During the

sampling phase, Φ1, the input signal is applied to the sampling

capacitors, CS. At the same time the holding capacitors, CH,

are discharged to analog ground. At the falling edge of Φ1 the

input signal is sampled on the bottom plates of the sampling

capacitors. In the next clock phase, Φ2, the two bottom plates

of the sampling capacitors are connected together and the

holding capacitors are switched to the op-amp output nodes.

The charge then redistributes between CS and CH completing

one sample-and-hold cycle. The front end sample-and-hold

output is a fully-differential, sampled-data representation of the

analog input. The circuit not only performs the sample-and-hold

function but will also convert a single-ended input to a fully-

differential output for the converter core. During the sampling

phase, the VIN pins see only the on-resistance of a switch and

CS. The relatively small values of these components result in a

typical full power input bandwidth of 250MHz for the converter.

As illustrated in the functional block diagram and the timing

diagram in Figure 1, eight identical pipeline subconverter

stages, each containing a two-bit flash converter and a two-

bit multiplying digital-to-analog converter, follow the S/H

circuit with the ninth stage being a two bit flash converter.

Each converter stage in the pipeline will be sampling in one

phase and amplifying in the other clock phase. Each

individual subconverter clock signal is offset by 180 degrees

from the previous stage clock signal resulting in alternate

stages in the pipeline performing the same operation.

The output of each of the eight identical two-bit subconverter

stages is a two-bit digital word containing a supplementary bit

to be used by the digital error correction logic. The output of

each subconverter stage is input to a digital delay line which is

controlled by the internal sampling clock. The function of the

digital delay line is to time align the digital outputs of the eight

identical two-bit subconverter stages with the corresponding

output of the ninth stage flash converter before applying the

eighteen bit result to the digital error correction logic. The

digital error correction logic uses the supplementary bits to

correct any error that may exist before generating the final ten

bit digital data output of the converter.

Because of the pipeline nature of this converter, the digital data

representing an analog input sample is output to the digital data

bus on the 7th cycle of the clock after the analog sample is

taken. This time delay is specified as the data latency. After the

data latency time, the digital data representing each

succeeding analog sample is output during the following clock

cycle. The digital output data is synchronized to the external

sampling clock by a double buffered latching technique. The

digital output data is available in two’s complement or offset

binary format depending on the state of the Data Format Select

(DFS) control input (see Table 1, A/D Code Table).

Internal Reference Voltage Output, VREFOUT

The HI5767 is equipped with an internal reference voltage

generator, therefore, no external reference voltage is

required. VREFOUT must be connected to VREFIN when using

the internal reference voltage.

An internal band-gap reference voltage followed by an

amplifier/buffer generates the precision +2.5V reference

voltage used by the converter. A 4:1 array of substrate

PNPs generates the “delta-VBE” and a two-stage op-amp

closes the loop to create an internal +1.25V band-gap

reference voltage. This voltage is then amplified by a

wideband uncompensated operational amplifier connected

11

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet HI5767.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HI5760 | A/D Converter | Intersil Corporation |

| HI5762 | A/D Converter | Intersil Corporation |

| HI5766 | A/D Converter | Intersil Corporation |

| HI5767 | A/D Converter | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |