|

|

PDF HD74LS165A Data sheet ( Hoja de datos )

| Número de pieza | HD74LS165A | |

| Descripción | Parallel-Load 8-bit Shift Register | |

| Fabricantes | Renesas Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HD74LS165A (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

HD74LS165A

Parallel-Load 8-bit Shift Register

REJ03D0449–0300

Rev.3.00

Jul.15.2005

The LS165A are 8-bit serial shift registers that shift the data in the direction of QA toward QH when clocked. Parallel-in

access to each stage is made available by eight individual direct data inputs that are enabled by a low level at the shift /

load input. These registers also feature gated clock inputs and complementary outputs from the eighth bit. All inputs

are diode-clamped to minimize transmission-line effects, thereby simplifying system design.

Clocking is accomplished through a 2-input positive-NOR gate, permitting one input to be used as a clock-inhibit

function. Holding either of the clock inputs high inhibits clocking and holding either clock input low with the shift /

load input high enables the other clock input. The clock-inhibit input should be changed to the high level only while the

clock input is high. Parallel loading is inhibited as long as the shift / load input is high. Data at the parallel inputs are

loaded directly into the register on a high-to-low transition of the shift / load input independently of the levels of the

clock, clock inhibit, or serial inputs.

Features

• Ordering Information

Part Name

Package Type

Package Code

(Previous Code)

Package

Abbreviation

HD74LS165AP

DILP-16 pin

PRDP0016AE-B

(DP-16FV)

P

HD74LS165AFPEL SOP-16 pin (JEITA)

PRSP0016DH-B

(FP-16DAV)

FP

Note: Please consult the sales office for the above package availability.

Taping Abbreviation

(Quantity)

—

EL (2,000 pcs/reel)

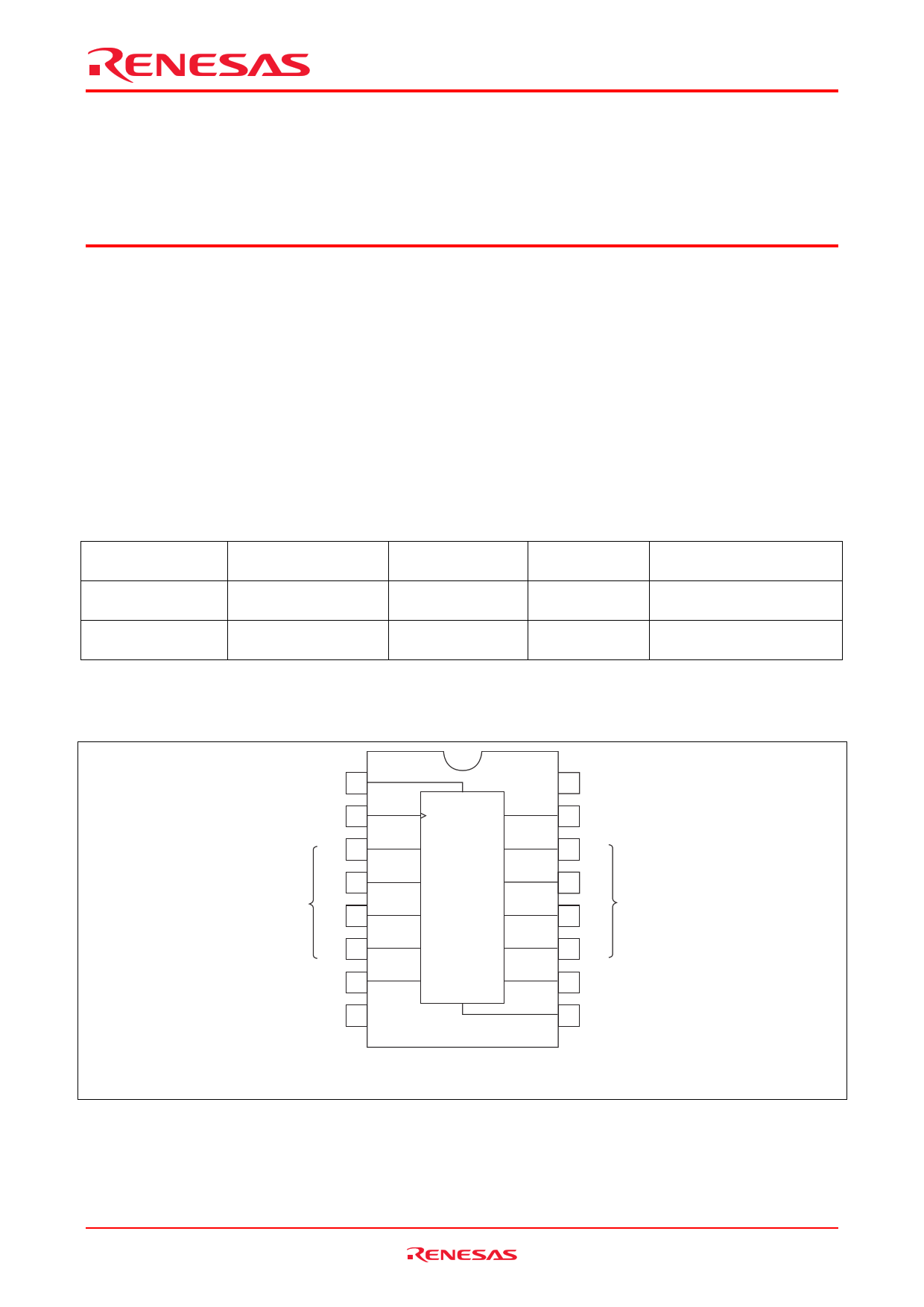

Pin Arrangement

Shift/

Load

Clock

1

2

E3

F4

Parallel

Inputs G 5

H6

Output QH 7

GND 8

Shift/Load

CK Clock

Inhibit

ED

FC

GB

HA

QH

Serial

QH Input

16 VCC

15

Clock

Inhibit

14 D

13 C

12 B

Parallel

Inputs

11 A

10

Serial

Input

9 Output QH

(Top view)

Rev.3.00, Jul.15.2005, page 1 of 7

1 page

HD74LS165A

Waveforms 2

Clock Inhibit

Input

Clock

Input

1.3V

tsu

3V

(Disable while

clock is high)

0V

3V

1.3V 1.3V 1.3V

tsu

tw (clock)

0V

F and H

Inputs

1.3V 1.3V

(See Notes A and B)

Shift/

Load

1.3V

tw (load)

1.3V

tsu

tw (load)

1.3V 1.3V 1.3V 1.3V

3V

0V

3V

0V

tPHL

Output QH

tPLH

1.3V

tPHL

1.3V

tPLH

1.3V

tPHL

1.3V

tPLH

1.3V

tPLH

Output QH

tPHL

1.3V 1.3V

tPLH

1.3V

tPHL

1.3V

tPLH

1.3V

tPHL

1.3V

Notes:

A. The remaining six data inputs and the serial input are low.

B. Prior to test, high-level data is loaded into H input.

C. The input pulse Generators have the following characteristics: PRR ≤ 1 MHz,

duty cycle ≤ 50%, Zout ≈ 50 Ω, tTLH ≤ 15 ns, tTHL ≤ 6 ns.

VOH

VOL

VOH

VOL

Rev.3.00, Jul.15.2005, page 5 of 7

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet HD74LS165A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HD74LS165A | Parallel-Load 8-bit Shift Register | Hitachi Semiconductor |

| HD74LS165A | Parallel-Load 8-bit Shift Register | Renesas Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |