|

|

PDF ZL38065 Data sheet ( Hoja de datos )

| Número de pieza | ZL38065 | |

| Descripción | 32 Channel Voice Echo Canceller | |

| Fabricantes | Zarlink Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ZL38065 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

ZL38065

32 Channel Voice Echo Canceller

Features

• Independent multiple channels of echo

cancellation; from 32 channels of 64 ms to 16

channels of 128 ms with the ability to mix

channels at 128 ms or 64 ms in any combination

• Fully compliant to ITU-T G.165, G.168 (2000) and

(2002) specifications

• Passed all AT&T voice quality tests for carrier

grade echo canceller systems.

• Unparalleled in-system tunability

• Sub 50 ms initial convergence times under many

typical network conditions

• Fast reconvergence on echo path changes

• Patented Advanced Non-Linear Processor with

high quality subjective performance

• Superior noise matching algorithm

• PCM coding, µ/A-Law ITU-T G.711 or sign

magnitude

• Per channel Fax/Modem G.164 2100 Hz or G.165

2100 Hz phase reversal Tone Disable

• Per channel echo canceller parameters control

• Transparent data transfer and mute

• Protection against narrow band signal divergence

and instability in high echo environments

Data Sheet

January 2006

Ordering Information

ZL38065QCG

ZL38065GDG

ZL38065QCG1

ZL38065GDG2

100 Pin LQFP Trays, Bake & Drypack

208 Ball LBGA Trays, Bake & Drypack

100 Pin LQFP* Trays, Bake & Drypack

208 Ball LBGA** Trays, Bake & Drypack

*Pb Free Matte Tin

**Pb Free Tin/Silver/Copper

-40°C to +85°C

• +9 dB to -12 dB level adjusters (3 dB steps) at all

signal ports

• Offset nulling of all PCM channels

• Independent Power Down mode for each group of

2 channels for power management

• Compatible to ST-BUS and GCI interface at

2 Mbps serial PCM

• 3.3 V pads and 1.8 V Logic core operation with

5 V tolerant inputs

• IEEE-1149.1 (JTAG) Test Access Port

Applications

• Voice over IP network gateways

• Voice over ATM, Frame Relay

• T1/E1/J1 multichannel echo cancellation

Rin

Sin

MCLK

Fsel

C4i

F0i

VDD1 (3.3V)

VSS

VDD2 (1.8 V)

ODE

Serial

to

Parallel

PLL

Timing

Unit

Echo Canceller Pool

Group 0 Group 1 Group 2

ECA/ECB ECA/ECB ECA/ECB

Group 4 Group 5 Group 6

ECA/ECB ECA/ECB ECA/ECB

Group 8 Group 9 Group 10

ECA/ECB ECA/ECB ECA/ECB

Group 12 Group 13 Group 14

ECA/ECB ECA/ECB ECA/ECB

Group 3

ECA/ECB

Group 7

ECA/ECB

Group 11

ECA/ECB

Group 15

ECA/ECB

Parallel

to

Serial

Note:

Refer to Figure 4

for Echo Canceller

block diagram

Microprocessor Interface

Test Port

Rout

Sout

IC0

RESET

DS CS R/W A12-A0 DTA D7-D0 IRQ TMS TDI TDO TCK TRST

Figure 1 - ZL38065 Device Overview

1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2004-2006, Zarlink Semiconductor Inc. All Rights Reserved.

1 page

ZL38065

Data Sheet

List of Tables

Table 1 - Quiet PCM Code Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 2 - Memory Page Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 3 - Group and Channel Allocation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 4 - Memory Mapping of Per Channel Control and Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5

Zarlink Semiconductor Inc.

5 Page

ZL38065

Data Sheet

1.1 Adaptive Filter

The adaptive filter adapts to the echo path and generates an estimate of the echo signal. This echo estimate is then

subtracted from Sin. For each group of echo cancellers, the adaptive filter is a 1024 tap FIR adaptive filter which is

divided into two sections. Each section contains 512 taps providing 64 ms of echo estimation. In Normal

configuration, the first section is dedicated to channel A and the second section to channel B. In Extended Delay

configuration, both sections are cascaded to provide 128 ms of echo estimation in channel A. In Back-to Back

configuration, the first section is used in the receive direction and the second section is used in the transmit

direction for the same channel.

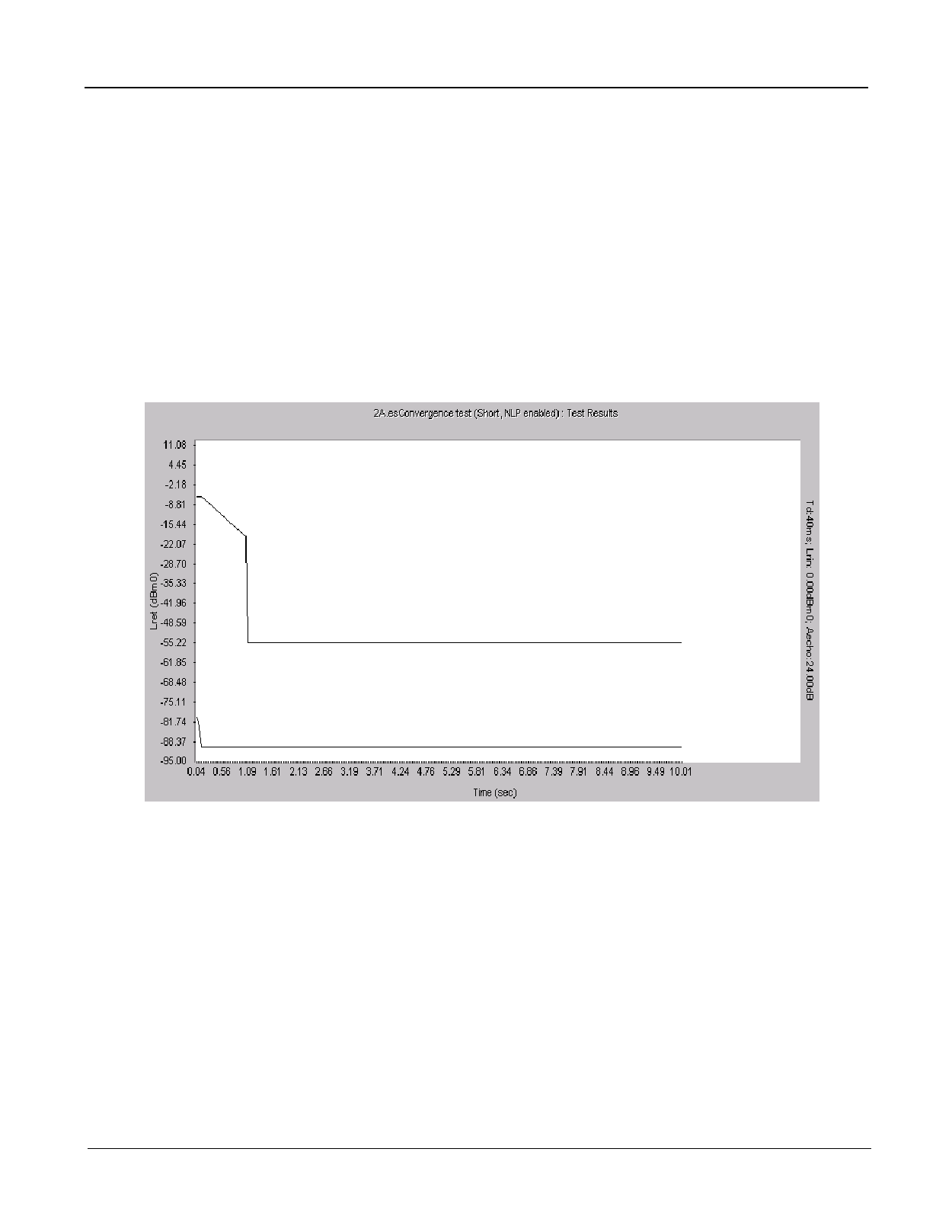

The ZL38065 offers industry leading convergence speeds, both in initial convergence and reconvergence. A

sample test result from G.168-2002 Test 2A can be seen in Figure 5. This test result demonstrates one of the many

conditions where the Zarlink device offer sub 50 ms initial convergence times (G.168 Test 2A, Hybrid 5, 40 ms

delay, ERL=24dB, Lrin=0dBm0). Full G.168 test results across all hybrids and test conditions are available upon

request.

Figure 5 - Sample G.168 Test 2A Convergence Result

1.2 Double-Talk Detector

Double-Talk is defined as those periods of time when signal energy is present in both directions simultaneously.

When this happens, it is necessary to disable the filter adaptation to prevent divergence of the Adaptive Filter

coefficients. Note that when double-talk is detected, the adaptation process is halted but the echo canceller

continues to cancel echo using the previous converged echo profile. A double-talk condition exists whenever the

relative signal levels of Rin (Lrin) and Sin (Lsin) meet the following condition:

Lsin > Lrin + 20log10(DTDT)

where DTDT is the Double-Talk Detection Threshold. Lsin and Lrin are signal levels expressed in dBm0.

A different method is used when it is uncertain whether Sin consists of a low level double-talk signal or an echo

return. During these periods, the adaptation process is slowed down but it is not halted. The slow convergence

speed is set using the Slow sub-register in Control Register 4. During slow convergence, the adaptation speed is

11

Zarlink Semiconductor Inc.

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ZL38065.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ZL38065 | 32 Channel Voice Echo Canceller | Zarlink Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |