|

|

PDF HCSxxx Data sheet ( Hoja de datos )

| Número de pieza | HCSxxx | |

| Descripción | Memory Programming Specification | |

| Fabricantes | Microchip Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HCSxxx (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

HCSXXX

HCSXXX Memory Programming Specification

This document includes the

programming specifications for the

following devices:

• HCS200

• HCS201

• HCS300

• HCS301

• HCS320

• HCS360

• HCS361

• HCS362

• HCS410

• HCS412

• HCS500

• HCS512

• HCS515

1.0 PROGRAMMING THE HCSXXX

All of the KEELOQ® devices are programmed using a

serial method. This Serial mode allows KEELOQ

devices to be programmed while in users' systems,

which increases the flexibility of designing

cryptographic encoders, decoders and transponders

into electronic systems. While some of the devices are

capable of being programmed through wireless

communications, the subject of this document is

focused on wired programmers that make contact with

the KEELOQ products while the components are in-

circuit or in a programmer socket. Additionally, this

programming specification only applies to all KEELOQ

devices listed above in all packages.

Note:

For the purpose of this document,

“KEELOQ devices” and “KEELOQ products”

refers to all of the components listed

above.

1.1 Programming Algorithm

Requirements

Depending on the device being programmed, the

method for entering Programming mode can be

achieved through the use of a combination of logic level

signals applied to the programming pins. One or two

pins are capable of accepting clock signals, while

another pin is dedicated to bidirectional data. These

pins are detailed in Table 1-1.

Additionally, the programming voltage range for VDD is

+5V ± 10% for all the KEELOQ devices. There is not a

requirement to apply high voltages to any of the pins

beyond the level of VDD in order to enter the

Programming mode. For more details about pin

configurations during programming, refer to Table 1-1.

1.2 Program/Verify Mode

The Program/Verify mode for the KEELOQ devices

allows programming for all memory locations within the

device being programmed. With the exception of the

decoders, these pins are also used to verify the memory

arrays.

2004 Microchip Technology Inc.

Preliminary

DS41256A-page 1

1 page

HCSXXX

2.0 MEMORY MAPPING

The program memory maps for KEELOQ products begin

at 0x000 and extend as shown in the tables that follow.

As a device is being programmed, the address counter

automatically increments to the next word location after

receiving a data word. The memory maps for all

KEELOQ encoders and transponders were designed so

that each word is 16 bits wide. Decoder memory maps

are 8 bits wide.

2.1 Encoder Memory Maps

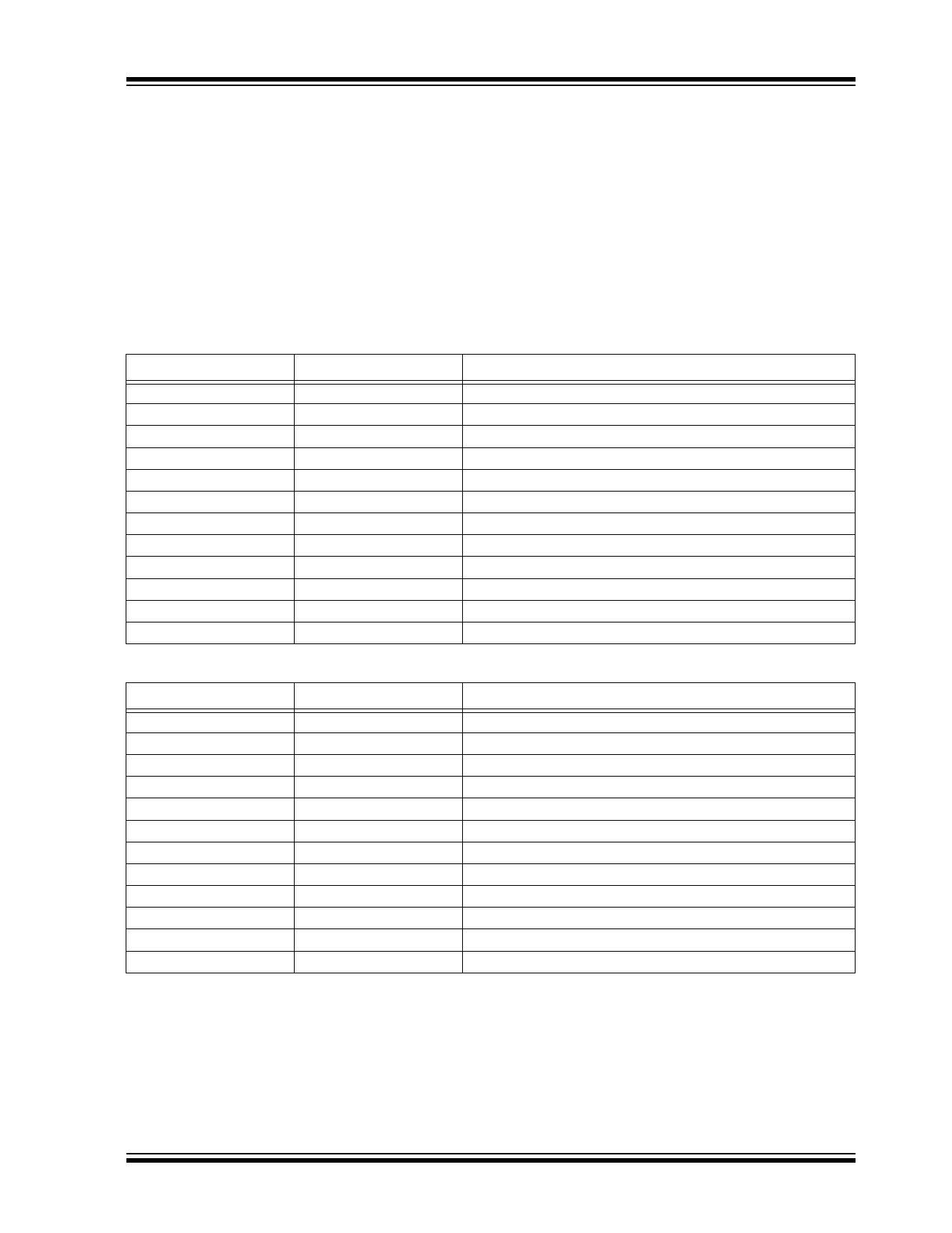

TABLE 2-1: HCS200 12 X 16-BIT EEPROM MEMORY MAP

Word Address

Mnemonic

Description

0x00

0x01

0x02

0x03

0x04

KEY_0

KEY_1

KEY_2

KEY_3

SYNC

Word 0 (LSb's) of 64-bit crypt key

Word 1 of 64-bit crypt key

Word 2 of 64-bit crypt key

Word 3 (MSb's) of 64-bit crypt key

16-bit synchronization value

0x05

0x06

Reserved

SER_0

Set to 0x0000

Word 0 (LSb's) of 32-bit serial number

0x07

0x08

0x09

0x0A

0x0B

SER_1

SEED_0

SEED_1

Reserved

CONFIG

Word 1 (MSb's) of 32-bit serial number

Word 0 (LSb's) of 32-bit seed value

Word 1 (MSb's) of 32-bit seed value

Set to 0x0000

Configuration Word

TABLE 2-2: HCS201 12 X 16-BIT EEPROM MEMORY MAP

Word Address

Mnemonic

Description

0x00

0x01

0x02

0x03

0x04

0x05

KEY_0

KEY_1

KEY_2

KEY_3

SYNC

Reserved

Word 0 (LSb's) of 64-bit crypt key

Word 1 of 64-bit crypt key

Word 2 of 64-bit crypt key

Word 3 (MSb's) of 64-bit crypt key

16-bit synchronization value

Set to 0x0000

0x06

0x07

0x08

0x09

0x0A

0x0B

SER_0

SER_1

SEED_0

SEED_1

DISC

CONFIG

Word 0 (LSb's) of 32-bit serial number

Word 1 (MSb's) of 32-bit serial number

Word 0 (LSb's) of 32-bit seed value

Word 1 (MSb's) of 32-bit seed value

Discrimination Word

Configuration Word

2004 Microchip Technology Inc.

Preliminary

DS41256A-page 5

5 Page

HCSXXX

2.4 Bulk Write Device

All transponders and encoders are bulk erased and

programmed with zeros following the Start condition.

The bulk erase/write time frame is specified as TPBW,

which is minimally 4.0 ms. After the bulk function is

complete, the programming state machine continues

into the Program mode where it begins to wait for data

and clock signals.

2.5 Serial Program/Verify Operation

For all of the encoders and transponders, the memory

maps have been designed to be in 16-bit format, which

means that each address location contains 16 bits of

information including “don't care” bits that are read as

zeros. Details relating to the designated pins for clock

and data signals are outlined in Table 1-1. The

decoders, on the other hand, were designed with

memory maps in 8-bit format, so they are discussed

separately in the next couple of paragraphs.

For specific information relating to the size of the

memory maps for a given family of devices, be sure to

review the tables in Section 2.1 “Encoder Memory

Maps”.

The following paragraphs were written with the

assumption that the target device has been placed into

the Programming mode and is now waiting for data or

a command byte to continue programming the memory

array.

2.5.1 ENCODERS/TRANSPONDERS

To input data to the target KEELOQ encoder or

transponder, 16 clock cycles are applied to the clock pin

of the target device while data is driven into the data pin.

Data is clocked into the target device on the falling edge

of the clock signal. Also, the minimum high time and low

time for the clock signals are 50 µs. During verification,

data must be sampled on the rising edge of the clock.

2.5.2 DECODERS

To input data to the target KEELOQ decoder, 8 clock

cycles are applied to the clock pin of the target device

while data is driven into the data pin. Data is clocked

into the target device on the falling edge of the clock

signals. Also, the minimum high time and minimum low

time for the clock signals are 50 µs. For the decoder

family, there are no verification functions.

2.6 Begin Programming

Write cycles are performed a bit-at-a-time throughout

the entire programming sequence for KEELOQ

products. The total write cycle, which includes internal

processing and programming time, is specified to take

a minimum of 50 ms. As a result, programmers can

include a delay for the minimum write cycle time or they

can poll the target device as discussed in Section 2.7

“Polling Write Cycle”.

2.7 Polling Write Cycle

2.7.1 HCS201 AND HCS412

Once the 16th clock cycle for the data word has been

generated and the next minimum low time for the clock

passes, the clock pin can be driven high to poll the

completion of the write cycle. Before the write cycle is

complete, the data pin for the target KEELOQ device will

be low. After the write cycle is complete, the data pin on

the HCS201 and the HCS412 will begin to provide

pulses to the programmer in order to signal the

completion of the write cycle. As a result, the

programmer data pin should be set to high-impedance

(input) so that it can read the pulses. After reading the

pulses on the data pin, the programmer should drive

the clock pin low and make the data pin an output so

that data can continue to be driven into the target

device. These pulses can be used for calibration

sequences for the HCS201 and the HCS412. For

information relating to oscillator calibration refer to

Section 5.0 “Program/Verify Mode Electrical

Characteristics”, which discusses oscillator tuning. If

the programmer polls the target device for the end of a

write cycle, these two devices will continue to emit

calibration pulses until their clock lines are driven low.

In order to measure the calibration pulses, the clock pin

must be driven high prior to the end of the write cycle,

otherwise the calibration pulses will not appear.

2.7.2 ALL OTHER KEELOQ DEVICES

Once the 16th clock cycle for the data word has been

generated for any of the encoders or transponders or

the last clock cycle for a decoder data packet is

generated, the clock pin can be driven high to poll for

the completion of the write cycle. Before the write cycle

is complete, the data pin for the target KEELOQ device

will be low. As a result, the programmer data pin should

be set to high-impedance (input) so that it can sense

the rising edge of data. After the write cycle is

complete, the data pin will be driven high until the clock

line is driven low again.

2004 Microchip Technology Inc.

Preliminary

DS41256A-page 11

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet HCSxxx.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HCSxxx | Memory Programming Specification | Microchip Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |