|

|

PDF PC7447A Data sheet ( Hoja de datos )

| Número de pieza | PC7447A | |

| Descripción | PowerPC RISC microprocessor | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de PC7447A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Features

• 3000 Dhrystone 2.1 MIPS at 1.3 GHz

• Selectable Bus Clock (30 CPU Bus Dividers up to 28x)

• Selectable MPx/60x Interface Voltage (1.8V, 2.5V)

• PD Typically 18W at 1.33 GHz at VDD = 1.3V; 8.0W at 1 GHz at VDD = 1.1V

Full Operating Conditions

• Nap, Doze and Sleep Power Saving Modes

• Superscalar (Four Instructions Fetched Per Clock Cycle)

• 4 GB Direct Addressing Range

• Virtual Memory: 4 Hexabytes (252)

• 64-bit Data and 36-bit Address Bus Interface

• Integrated L1: 32 KB Instruction and 32 KB Data Cache

• Integrated L2: 512 KB

• 11 Independent Execution Units and 3 Register Files

• Write-back and Write-through Operations

• fINT Max = 1.33 GHz (1.42 GHz to be Confirmed)

• fBUS Max = 133 MHz/166 MHz

Description

The PC7447A host processor is a high-performance, low-power, 32-bit implementa-

tions of the PowerPC Reduced Instruction Set Computer (RISC) architecture

combined with a full 128-bit implementation of Freescale®’s AltiVec™ technology.

This microprocessor is ideal for leading-edge embedded computing and signal pro-

cessing applications. The PC7447A features 512 KB of on-chip L2 cache. The

PC7447A microprocessor has no backside L3 cache, allowing for a smaller package

designed as a pin-for-pin replacement for the PC7447 microprocessor. This device

benefits from a silicon-on-insulator (SOI) CMOS process technology, engineered to

help deliver tremendous power savings without sacrificing speed. A low-power version

of the PC7447A microprocessor is also available.

Figure 1-1 shows a block diagram of the PC7447A. The core is a high-performance

superscalar design supporting a double-precision floating-point unit and a SIMD multi-

media unit. The memory storage subsystem supports the MPX bus protocol and a

subset of the 60x bus protocol to the main memory and other system resources.

Note that the PC7447A is a footprint-compatible, drop-in replacement in a PC7447

application if the core power supply is 1.3V.

Screening

• Full Military Temperature Range (Tj = -55°C, +125°C)

• Industrial Temperature Range (Tj = -40°C, +110°C)

PowerPC®

7447A

RISC

Microprocessor

PC7447A

Preliminary

GH suffix

HITCE 360

Rev. 5387B–HIREL–07/05

1 page

5387B–HIREL–07/05

PC7447A [Preliminary]

Dedicated adder calculates effective addresses (EAs)

Supports store gathering

Performs alignment, normalization, and precision conversion for floating-point data

Executes cache control and TLB instructions

Performs alignment, zero padding, and sign extension for integer data

Supports hits under misses (multiple outstanding misses)

Supports both big- and little-endian modes, including misaligned little-endian

accesses

• Three issue queues, FIQ, VIQ, and GIQ, can accept as many as one, two, and three

instructions, respectively, in a cycle. Instruction dispatch requires the following:

– Instructions can only be dispatched from the three lowest IQ entries: IQ0, IQ1, and

IQ2

– A maximum of three instructions can be dispatched to the issue queues per clock

cycle

– Space must be available in the CQ for an instruction to dispatch (this includes

instructions that are assigned a space in the CQ but not in an issue queue)

• Rename buffers

– 16 GPR rename buffers

– 16 FPR rename buffers

– 16 VR rename buffers

• Dispatch unit

– Decode/dispatch stage fully decodes each instruction

• Completion unit

– The completion unit retires an instruction from the 16-entry completion queue (CQ)

when all instructions ahead of it have been completed, the instruction has finished

execution, and no exceptions are pending

– Guarantees sequential programming model (precise exception model)

– Monitors all dispatched instructions and retires them in order

– Tracks unresolved branches and flushes instructions after a mispredicted branch

– Retires as many as three instructions per clock cycle

• Separate on-chip L1 instruction and data caches (Harvard Architecture)

– 32-Kbyte, eight-way set-associative instruction and data caches

– Pseudo least-recently-used (PLRU) replacement algorithm

– 32-byte (eight-word) L1 cache block

– Physically indexed/physical tags

– Cache write-back or write-through operation programmable on a per-page or per-

block basis

5

5 Page

PC7447A [Preliminary]

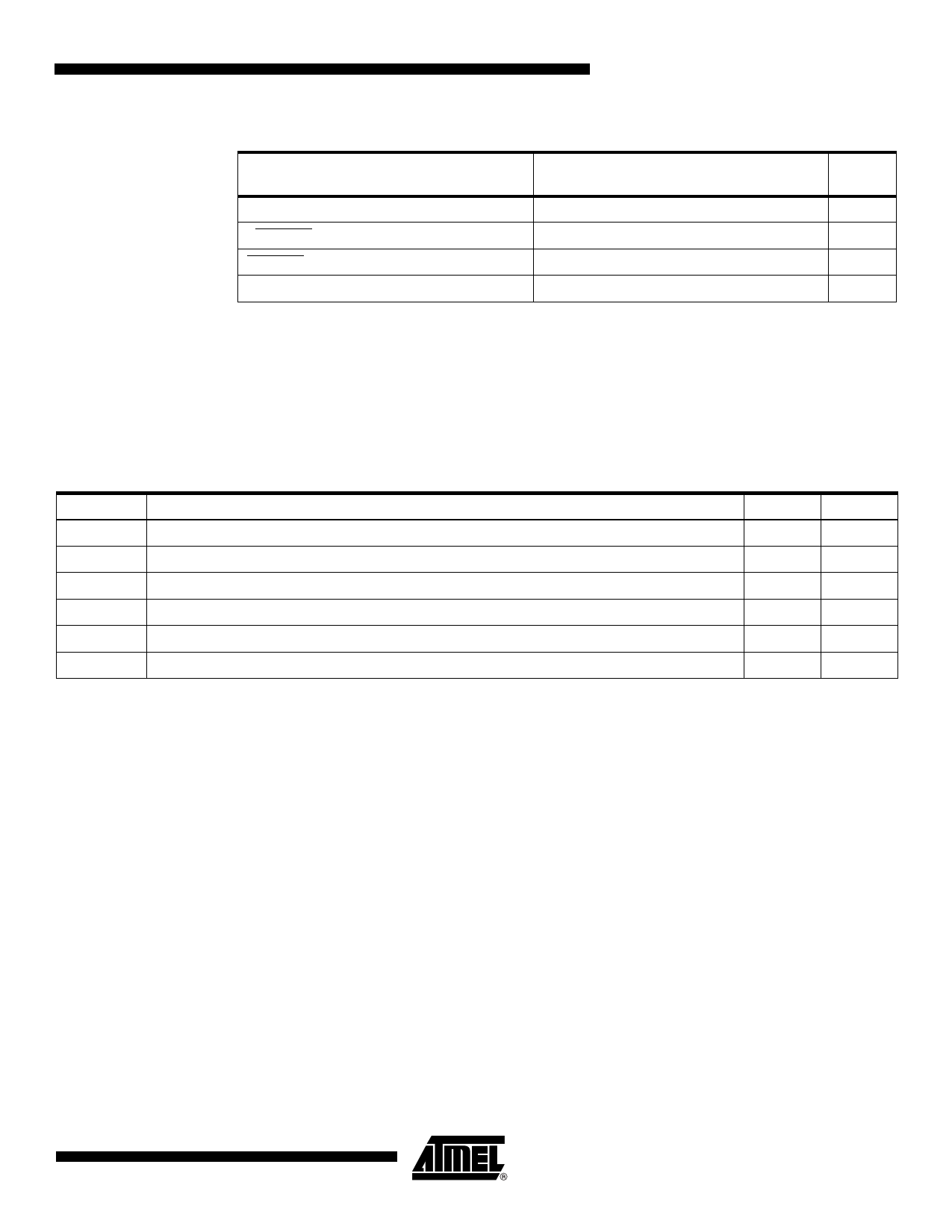

Table 6-3. Input Threshold Voltage Setting(1)

BVSEL Signal

Processor Bus Input Threshold is

Relative to:

Notes

0 1.8V (2)

¬HRESET

Not available

HRESET

2.5V

1

Notes:

2.5V

1. Caution: The input threshold selection must agree with the OVDD voltages supplied. See notes

in Table 6-1 on page 9.

2. If used, pull-down resistors should be less than 250Ω.

6.4 Thermal Characteristics

6.4.1

Package Characteristics

Table 6-4. Package Thermal Characteristics(1)

Symbol Characteristic

Value

Unit

RθJA(2)(3)

RθJMA(2)(4)

RθJMA(2)(4)

RθJMA(2)(4)

RθJB(5)

RθJC(6)

Junction-to-ambient thermal resistance, natural convection, single-layer (1s) board

Junction-to-ambient thermal resistance, natural convection, four-layer (2s2p) board

Junction-to-ambient thermal resistance, 200 ft./min. airflow, single-layer (1s) board

Junction-to-ambient thermal resistance, 200 ft./min. airflow, four-layer (2s2p) board

Junction-to-board thermal resistance

Junction-to-case thermal resistance

26

19

20

16

10

< 0.1

°C/W

°C/W

°C/W

°C/W

°C/W

°C/W

Notes:

1. See ”Thermal Management Information” on page 12 for details about thermal management.

2. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) tempera-

ture, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

3. Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

4. Per JEDEC JESD51-6 with the board horizontal.

5. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on

the top surface of the board near the package.

6. This is the thermal resistance between the die and the case top surface as measured with the cold plate method (MIL

SPEC-883 Method 1012.1) with the calculated case temperature. The actual value of RθJC for the part is less than 0.1°C/W.

6.4.2

Internal Package Conduction Resistance

For the exposed-die packaging technology described in Table 6-4 on page 11, the intrinsic con-

duction thermal resistance paths are as follows:

• The die junction-to-case thermal resistance (the case is actually the top of the exposed

silicon die)

• The die junction-to-ball thermal resistance

Figure 19 depicts the primary heat transfer path for a package with an attached heat sink

mounted to a printed-circuit board.

5387B–HIREL–07/05

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet PC7447A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PC7447 | (PC7447 / PC7457) PowerPC 7457 RISC Microprocessor | ATMEL Corporation |

| PC7447A | PowerPC RISC microprocessor | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |