|

|

PDF CDB42L52 Data sheet ( Hoja de datos )

| Número de pieza | CDB42L52 | |

| Descripción | Evaluation Board | |

| Fabricantes | Cirrus Logic | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CDB42L52 (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

CDB42L52

Evaluation Board for CS42L52

Features

Stereo Analog Inputs

– 4 Stereo Audio Jack Inputs, 2 of which can

be Differential Microphone Inputs

– Channel Mixer

MUX’d Analog Output and Speaker Outputs

– Headphone/Line Out Jack

– Stereo Headphone Jack

– Stereo Speaker Outputs w/Banana Jacks

8- to 96-kHz S/PDIF Interface

– CS8416 Digital Audio Receiver

– CS8406 Digital Audio Transmitter

I/O Stake Headers

– External Control Port Accessibility

– External DSP Serial Audio I/O Accessibility

Independent, Regulated Power Supplies

1.65 V to 3.3 V Logic Interface

FlexGUI S/W Control - Windows® Compatible

– Pre-Defined & User-Configurable Scripts

Description

Using the CDB42L52 evaluation board is an ideal way

to evaluate the CS42L52 CODEC. Use of the board re-

quires an analog/digital signal source, an analyzer and

power supplies. A Windows PC-compatible computer is

also needed in order to configure the CS42L52 and the

board functionality.

System timing can be provided by the CS8416, by the

CS42L52 with supplied master clock, or via an I/O stake

header with a DSP connected.

1/8th inch audio jacks are provided for the CS42L52 an-

alog inputs and HP/Line outputs. Speaker driver

outputs are via Banana jacks. Digital data I/O connec-

tions are via RCA phono or optical connectors to the

CS8416 and CS8406 (S/PDIF Rx and Tx).

The Windows-based software GUI provided makes

configuring the CDB42L52 easy. The software commu-

nicates through the PC’s USB to configure board and

FPGA registers so that all features of the CS42L52 can

be evaluated. The evaluation board may also be con-

figured to accept external timing and data signals for

operation in a user application during system develop-

ment.

ORDERING INFORMATION

CDB42L52

Evaluation Board

Software Mode

Control Port

Reset

I²C Header

MCLK

Reset

S/PDIF Output

(CS8406)

S/PDIF Input

(CS8416)

FPGA

CS42L52

MCLK

Oscillator

(socket)

Reset

Clk/Data SRC

Clocks/Data

Header

Frequency

Synthesizer PLL

Reset

http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 2006

(All Rights Reserved)

Analog Input

(Line + MIC)

Speaker Outputs

Analog Output

(Line + Headphone)

DECEMBER '06

DS680DB1

1 page

CDB42L52

1.9 Analog Inputs

Four stereo jack connectors supply the AC coupled line-level analog inputs to the CS42L52. Differential or

single ended microphone inputs may be connected to J45 or J50 in place of line inputs. Stake headers J46

J38, J51 and J49 allow the user to select (with jumpers installed) the CS42L52 as the microphone bias

source for each microphone input.

Figure 8 on page 17 illustrates how the analog inputs are connected and routed. Table 2 on page 14 details

the jumper selections. The CS42L52 data sheet specifies the allowed full scale input voltage level.

1.10 Analog Outputs

The CDB42L52 has a Stereo Headphone/Line output jack and a separate Stereo Headphone (HP) output

jack for the ground centered DAC output. Stake headers are provided to allow the user to select a 16 Ω or

a 32 Ω resistive load connected to the DAC output or a filtered or unfiltered output for the HP/Line jack out-

put. The resistive load can be selected to evaluate the CS42L52 drive capabilities. When connecting head-

phones to either output jack, the resistive load should be disconnected by removing the jumpers on each

stake header.

The CDB42L52 also has A/B speaker output banana jacks (2 per A or B channel) and 1/8“ jack outputs. (1

per A or B channel). Stake headers on each channel (A or B) connect the CS42L52 Class D speaker driver

amp outputs to either banana jack or 1/8” jack output in a number of configurations. Audio jack stake header

selections include RC filtered or unfiltered outputs. Banana jack output selections include RLC filtered, un-

filtered and either full or half bridge output modes. The red banana jacks designate the positive speaker ter-

minal connection and the black jacks designate the negative terminal connection.

1.11 Control Port Connectors

The graphical user interface for the CDB42L52 (Cirrus Logic Flex GUI) allows the user to configure the

CS42L52 registers and other component registers via the onboard I²C control bus. The GUI interfaces with

the CDB via the USB connection to a PC. Section 2. “Software Mode Control” on page 6 provides a descrip-

tion of the Graphical User Interface (GUI).

1.11.1 USB Connector

Connecting a USB port cable from a PC to the USB connector on the board and launching the Cirrus

FlexGUI software enables the CDB42L52. Note: The USB port connection also provides DC power to the

board (except for VP). The minimum current required is approximately 300 mA. It may, therefore, be nec-

essary to connect the CDB42L52 directly to the USB port on the PC as opposed to a hub or keyboard port

where current may be limited.

DS680DB1

5

5 Page

CDB42L52

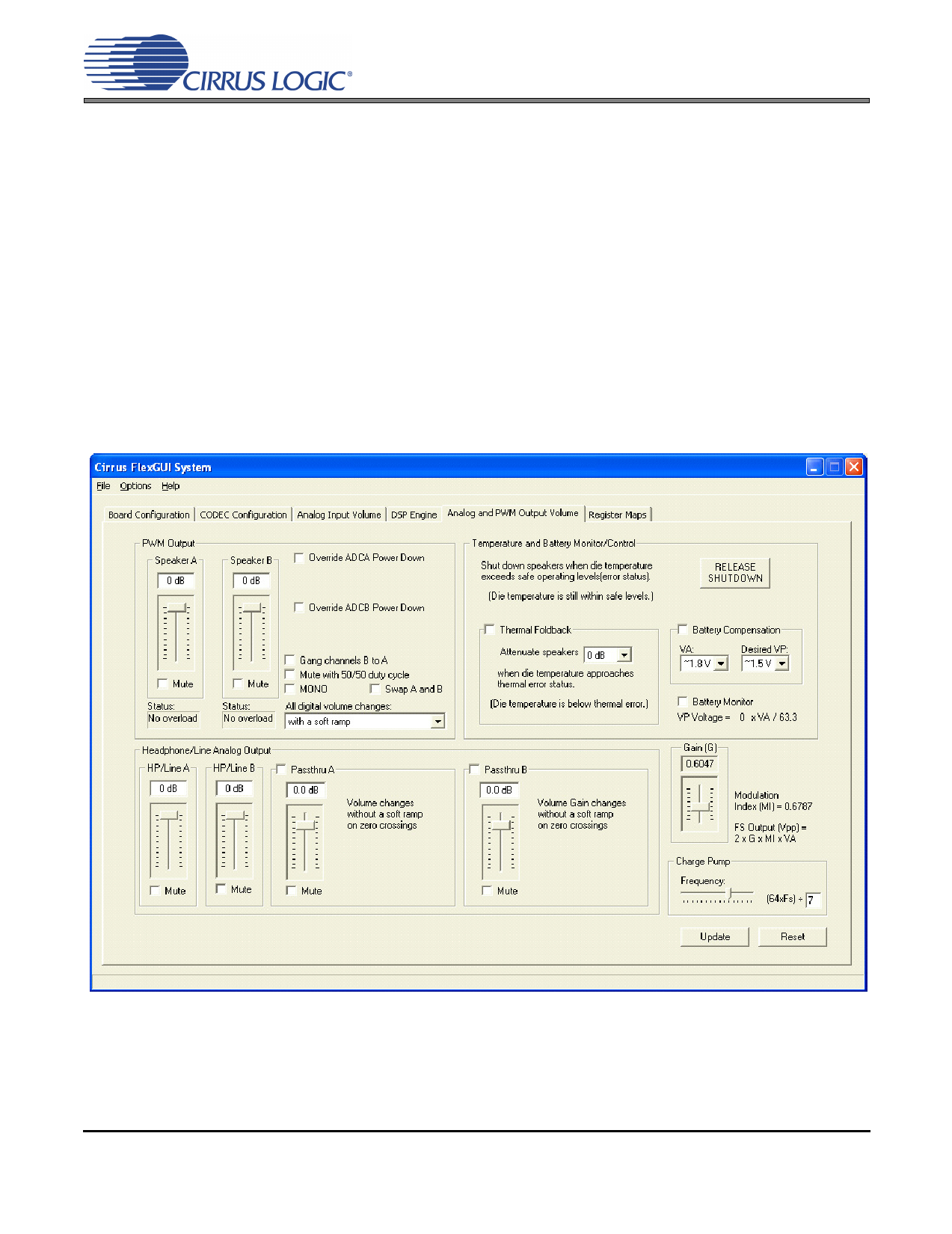

2.5 Analog and PWM Output Volume Tab

The “Analog and PWM Output Volume” tab provides high-level control of the CS42L52 DAC output analog

MUX, Input pass-through volume, HP/Line output volume levels and charge pump frequency. This tab also

provides controls for the PWM output including speaker volume, PWM gain and modulation index. Temper-

ature and Battery monitoring controls for the PWM/Speaker outputs are also on this tab. Status text detailing

the CODEC’s specific configuration is shown in read-only edit boxes, in parenthesis or appears directly be-

low the associated control. This text will change depending on the setting of the associated control. A de-

scription of each control group is outlined below (register descriptions are in the CS42L52 data sheet).

Headphone/Line Analog Output - Digital and analog volume controls and adjustments for the DAC channel

(outside of the SPE) and for the input pass-through. Gain, Modulation Index, current limit and charge pump

frequency adjustment are also provided and affect the FS output levels.

PWM Output - Volume, mute, power down and other functional controls for the PWM speaker outputs.

Temperature and Battery Monitor/Control - Battery Compensation, Thermal Foldback, Temperature Shut-

down and Battery Monitor for the PWM/Speaker outputs.

DS680DB1

Figure 5. Analog and PWM Output Volume Tab

11

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet CDB42L52.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CDB42L50 | Low Voltage/ Stereo CODEC with headphone Amp | Cirrus Logic |

| CDB42L52 | Evaluation Board | Cirrus Logic |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |