|

|

PDF AD9927 Data sheet ( Hoja de datos )

| Número de pieza | AD9927 | |

| Descripción | 14-Bit CCD Signal Processor | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD9927 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

14-Bit CCD Signal Processor with V-Driver

and Precision TimingTM Generator

AD9927

FEATURES

Integrated 18-channel V-driver

1.8 V AFETG core

Internal LDO regulator and charge pump circuitry

Compatibility with 3 V or 1.8 V systems

24 programmable vertical clock signals

Correlated double sampler (CDS) with −3 dB, 0 dB,

+3 dB, and +6 dB gain

6 dB to 42 dB, 10-bit variable gain amplifier (VGA)

14-bit, 40 MHz analog-to-digital converter (ADC)

Black level clamp with variable level control

Complete on-chip timing generator

Precision Timing core with ~400 ps resolution

On-chip 3 V horizontal and RG drivers

General-purpose outputs (GPOs) for shutter and

system support

On-chip driver for external crystal

On-chip sync generator with external sync input

128-lead CSP_BGA package, 9 mm × 9 mm, 0.65 mm pitch

APPLICATIONS

Digital still cameras

GENERAL DESCRIPTION

The AD9927 is a highly integrated CCD signal processor for

digital still camera applications. It includes a complete analog

front end with A/D conversion, combined with a full-function

programmable timing generator and 18-channel vertical driver

(V-driver). The timing generator is capable of supporting up to

24 vertical clock signals to control advanced CCDs. The on-

chip V-driver supports up to 18 channels for use with 5-field

CCDs. A Precision Timing core allows adjustment of high speed

clocks with approximately 400 ps resolution at 40 MHz

operation. The AD9927 also contains eight general-purpose

outputs, which can be used for shutter and system functions.

The analog front end includes black level clamping, CDS, VGA,

and a 14-bit ADC. The timing generator provides all the

necessary CCD clocks: RG, H-clocks, V-clocks, sensor gate

pulses, substrate clock, and substrate bias control.

The AD9927 is specified over an operating temperature range

of –25°C to +85°C.

FUNCTIONAL BLOCK DIAGRAM

REFT REFB

–3dB, 0dB, +3dB, +6dB

CCDIN

CDS

VGA

VREF

14-BIT

ADC

14

3V INPUT

1.8V OUTPUT

LDO

REG

6dB TO 42dB

CLAMP

1.8V INPUT

3V OUTPUT

RG

HL

H1 TO H8

V1A-V6 (3-LEVEL)

V7-V15 (2-LEVEL)

SUBCK

CHARGE

PUMP

HORIZONTAL

8 DRIVERS

18 XV1 TO XV24

VERTICAL

DRIVER

24

VERTICAL

TIMING

CONTROL

XSUBCK 8

INTERNAL CLOCKS

PRECISION

TIMING

GENERATOR

SYNC

GENERATOR

AD9927

INTERNAL

REGISTERS

DOUT

SL

SCK

SDATA

XSUBCNT

GP01 TO GP08

HD VD SYNC CLI CLO

Figure 1.

RSTB

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2006 Analog Devices, Inc. All rights reserved.

1 page

AD9927

ANALOG SPECIFICATIONS

AVDD = 1.8 V, fCLI = 40 MHz, typical timing specifications, TMIN to TMAX, unless otherwise noted.

Table 3.

Parameter

CDS1

Allowable CCD Reset Transient

CDS Gain Accuracy

−3.0 dB CDS Gain

0 dB CDS Gain

+3 dB CDS Gain

+6 dB CDS Gain

Maximum Input Range Before Saturation

−3 dB CDS Gain

0 dB CDS Gain

+3 dB CDS Gain

+6 dB CDS Gain

Allowable OB Pixel Amplitude1

0 dB CDS Gain (Default)

+6 dB CDS Gain

VARIABLE GAIN AMPLIFIER (VGA)

Gain Control Resolution

Gain Monotonicity

Gain Range

Low Gain (VGA Code 15, Default)

Maximum Gain (VGA Code 1023)

BLACK LEVEL CLAMP

Clamp Level Resolution

Clamp Level

Minimum Clamp Level (Code 0)

Maximum Clamp Level (Code 1023)

ADC

Resolution

Differential Nonlinearity (DNL)

No Missing Codes

Integral Nonlinearity (INL)

Full-Scale Input Voltage

VOLTAGE REFERENCE

Reference Top Voltage (REFT)

Reference Bottom Voltage (REFB)

SYSTEM PERFORMANCE

Gain Accuracy

Low Gain (VGA Code 15)

Maximum Gain (VGA Code 1023)

Peak Nonlinearity, 1.0 V Input Signal

Total Output Noise

Power Supply Rejection (PSR)

Min Typ Max Unit

Notes

0.5 1.2 V

−3.3 −2.8 −2.3 dB

−0.5 0

+0.5 dB

2.4 2.9 3.4 dB

5.0 5.5 6.0 dB

1.4 V p-p

1.0 V p-p

0.7 V p-p

0.5 V p-p

VGA gain = 6.3 dB (Code 15, default value)

VGA gain = 6.3 dB (Code 15, default value)

−100

−50

+200 mV

+100 mV

1024

Guaranteed

Steps

6.3 dB

42.4 dB

1024

0

255

Steps

LSB

LSB

Measured at ADC output

14

−1.0 ±0.5

Guaranteed

4 16

2.0

Bits

LSB

LSB

V

1.4 V

0.4 V

Includes entire signal chain

0 dB CDS gain

5.8 6.3 6.8 dB

Gain = (0.0358 × Code) + 5.76 dB

41.9 42.4 42.9 dB

0.1 0.3 %

6 dB VGA gain, 0 dB CDS gain applied

0.5 LSB rms AC-grounded input, 6 dB VGA gain applied

50 dB Measured with step change on supply

1 Input signal characteristics defined as follows:

500mV TYP

RESET TRANSIENT

200mV MAX

OPTICAL BLACK PIXEL

INPUT

1V MAX

SIGNAL RANGE

(0dB CDS GAIN)

Rev. 0 | Page 5 of 100

5 Page

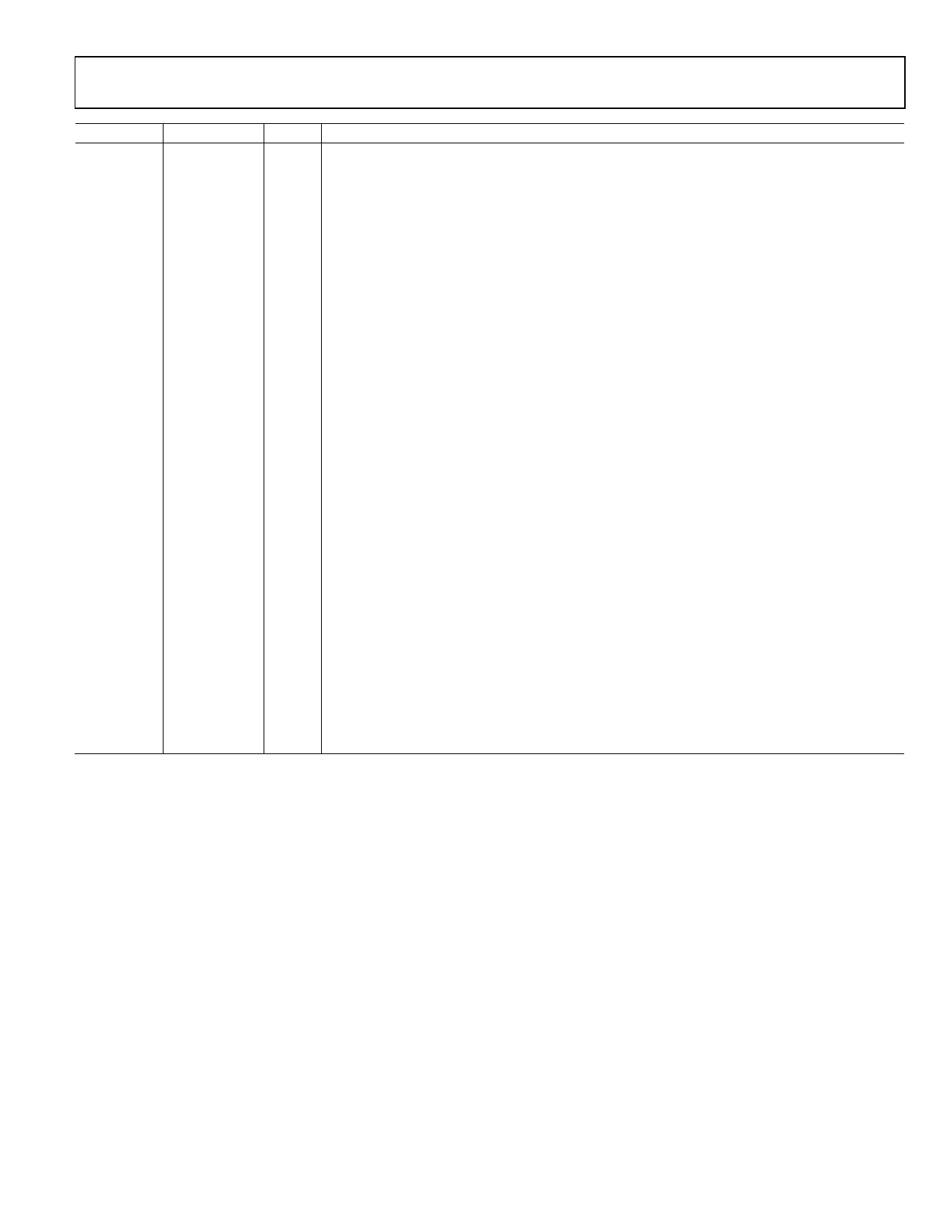

AD9927

Pin No.

A3

K4

J3

J4

H3

H4

G4

G3

F3

F4

E4

E3

D4

D3

D5

D6

D7

C7

C8

D8

J8

J7

K8

D10

J6

G9

J9

A11, A12,

B10, B12,

C6, C9, C12,

D9, D12, E9,

E12, F12,

G12

Mnemonic

DCLK

SUBCK

V1A

V1B

V2A

V2B

V3A

V3B

V4

V5

V6

V7

V8

V9

V10

V11

V12

V13

V14

V15

TEST0

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

NC

Type1

DO

VO3

VO3

VO3

VO3

VO3

VO3

VO3

VO3

VO3

VO3

VO2

VO2

VO2

VO2

VO2

VO2

VO2

VO2

VO2

AO

AO

DI

DI

AI

AI

DI

Description

Data Clock Output.

CCD Substrate Clock

CCD Vertical Transfer Clock. 3-Level Output (XV1 + XV16)

CCD Vertical Transfer Clock. 3-Level Output (XV1 + XV17)

CCD Vertical Transfer Clock. 3-Level Output (XV2 + XV18)

CCD Vertical Transfer Clock. 3-Level Output (XV2 + XV19)

CCD Vertical Transfer Clock. 3-Level Output (XV3 + XV20)

CCD Vertical Transfer Clock. 3-Level Output (XV3 + XV21)

CCD Vertical Transfer Clock. 3-Level Output (XV4 + XV22)

CCD Vertical Transfer Clock. 3-Level Output (XV5 + XV23)

CCD Vertical Transfer Clock. 3-Level Output (XV6 + XV24)

CCD Vertical Transfer Clock. 2-Level Output (XV7)

CCD Vertical Transfer Clock. 2-Level Output (XV8)

CCD Vertical Transfer Clock. 2-Level Output (XV9)

CCD Vertical Transfer Clock. 2-Level Output (XV10)

CCD Vertical Transfer Clock. 2-Level Output (XV11)

CCD Vertical Transfer Clock. 2-Level Output (XV12)

CCD Vertical Transfer Clock. 2-Level Output (XV13)

CCD Vertical Transfer Clock. 2-Level Output (XV14)

CCD Vertical Transfer Clock. 2-Level Output (XV15)

Do Not Connect

Do Not Connect

Connect to 1.8 V/3 V Supply

Connect to Ground

Connect to Ground

Connect to Ground

Connect to Ground

Not Internally Connected

1 AI = analog input, AO = analog output, DI = digital input, DO = digital output, DIO = digital input/output, P = power, VO2 = vertical driver output 2-level, VO3 = vertical

driver output 3-level.

Rev. 0 | Page 11 of 100

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AD9927.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD9920A | 12-Bit CCD Signal Processor | Analog Devices |

| AD9923A | CCD Signal Processor | Analog Devices |

| AD9925 | CCD Signal Processor | Analog Devices |

| AD9927 | 14-Bit CCD Signal Processor | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |