|

|

PDF PCK9446 Data sheet ( Hoja de datos )

| Número de pieza | PCK9446 | |

| Descripción | LVCMOS clock fan-out buffer | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PCK9446 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

PCK9446

2.5 V and 3.3 V LVCMOS clock fan-out buffer

Rev. 01 — 10 April 2006

Product data sheet

1. General description

The PCK9446 is a 2.5 V and 3.3 V compatible 1 : 10 clock distribution buffer designed for

low-voltage mid-range to high-performance telecom, networking and computing

applications. Both 3.3 V, 2.5 V and dual supply voltages are supported for mixed-voltage

applications. The PCK9446 offers 10 low skew outputs and 2 selectable inputs for clock

redundancy. The outputs are configurable and support 1 : 1 and 1 : 2 output to input

frequency ratios. The PCK9446 is specified for the extended temperature range of

−40 °C to +85 °C.

The PCK9446 is a full static design supporting clock frequencies up to 250 MHz. The

signals are generated and retimed on-chip to ensure minimal skew between the three

output banks. Two independent LVCMOS compatible clock inputs are available. This

feature supports redundant clock sources or the addition of a test clock into the system

design. Each of the three output banks can be individually supplied by 2.5 V or 3.3 V

supporting mixed voltage applications. The FSELx pins choose between division of the

input reference frequency by one or two. The frequency divider can be set individually for

each of the three output banks. The PCK9446 can be reset and the outputs are disabled

by deasserting the MR/OE pin (logic HIGH state). Asserting OE will enable the outputs.

All inputs accept LVCMOS signals while the outputs provide LVCMOS compatible levels

with the capability to drive terminated 50 Ω transmission lines. Please refer to the

PCK9456 specification for a 1 : 10 mixed voltage buffer with LVPECL compatible inputs.

For series terminated transmission lines, each of the PCK9446 outputs can drive one or

two traces giving the devices an effective fan-out of 1 : 20. The device is packaged in a

32-lead LQFP package which has a 7 mm × 7 mm body size with a conservative 0.8 mm

pin spacing.

2. Features

I Configurable 10 outputs LVCMOS clock distribution buffer

I Compatible to single, dual and mixed 3.3 V/2.5 V voltage supply

I Wide range output clock frequency up to 250 MHz

I Designed for mid-range to high-performance telecom, networking and computer

applications

I Supports applications requiring clock redundancy

I Maximum output skew of 200 ps (100 ps within one bank)

I Selectable output configurations per output bank

I 3-stateable outputs

I 32-lead LQFP packaging

I Ambient operating temperature range of −40 °C to +85 °C

1 page

Philips Semiconductors

PCK9446

2.5 V and 3.3 V LVCMOS clock fan-out buffer

7. Limiting values

Table 5. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol Parameter

Conditions

Min

VCC supply voltage

VI input voltage

VO output voltage

−0.3

−0.3

−0.3

II input current

IO output current

Tstg storage temperature

-

-

−40

Max

+4.6

VCC + 0.3

VCC + 0.3

±20

±50

+125

Unit

V

V

V

mA

mA

°C

8. Recommended operating conditions

Table 6. Operating conditions

Symbol Parameter

VCC

VCC(bankA)

VCC(bankB)

VCC(bankC)

Tamb

supply voltage

supply voltage (bank A)

supply voltage (bank B)

supply voltage (bank C)

ambient temperature

Conditions

VCCA pins

VCCB pins

VCCC pins

Min

2.375

2.375

2.375

2.375

−40

Typ

-

-

-

-

-

Max

3.465

3.465

3.465

3.465

+85

Unit

V

V

V

V

°C

PCK9446_1

Product data sheet

Rev. 01 — 10 April 2006

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

5 of 17

5 Page

Philips Semiconductors

PCK9446

2.5 V and 3.3 V LVCMOS clock fan-out buffer

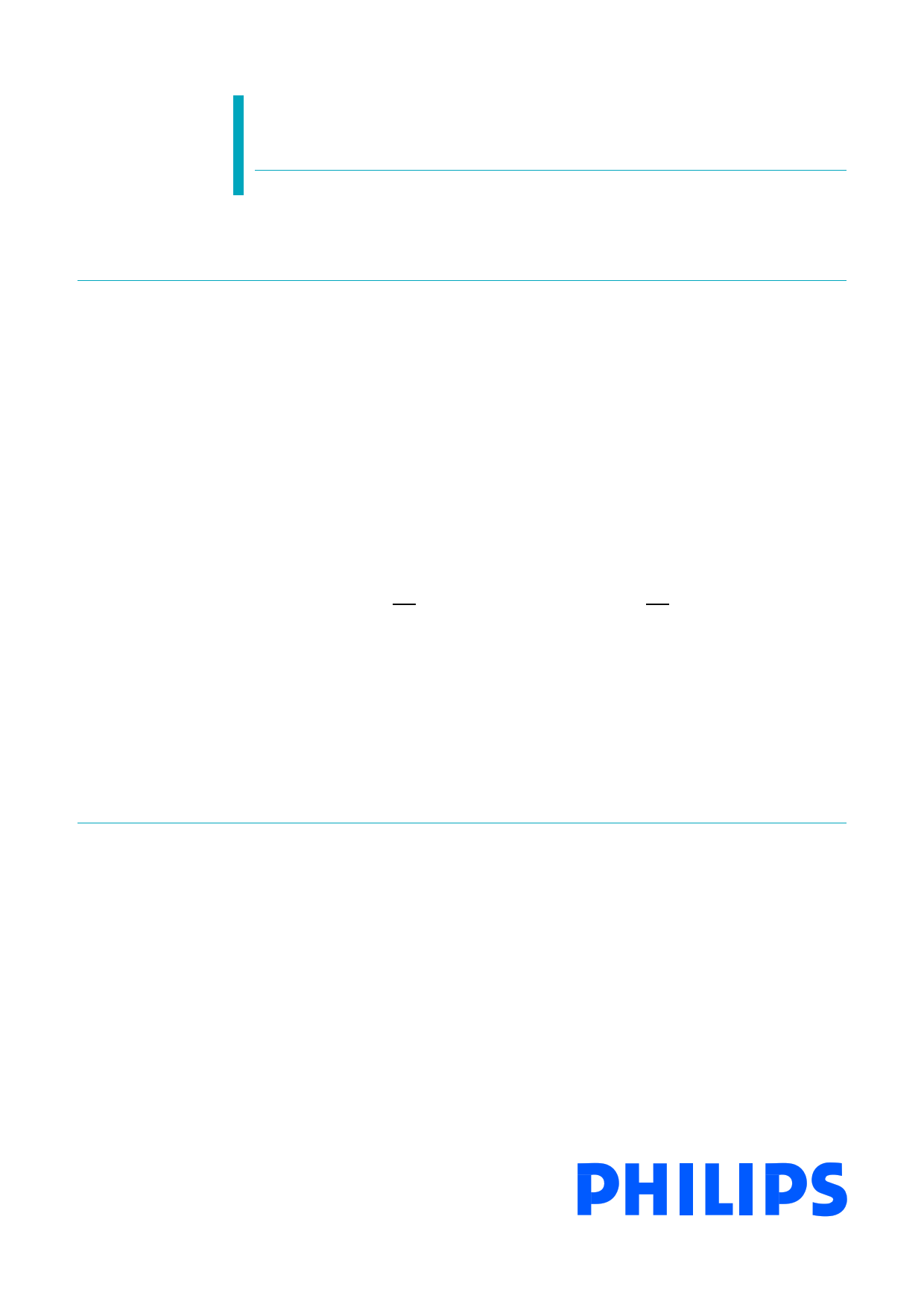

PCK9446

OUTPUT

BUFFER

Rs = 22 Ω Zo = 50 Ω

Ro

IN

14 Ω

Rs = 22 Ω Zo = 50 Ω

14 Ω + 22 Ω || 22 Ω = 50 Ω || 50 Ω

25 Ω = 25 Ω

Fig 5. Optimized dual line termination

12. Test information

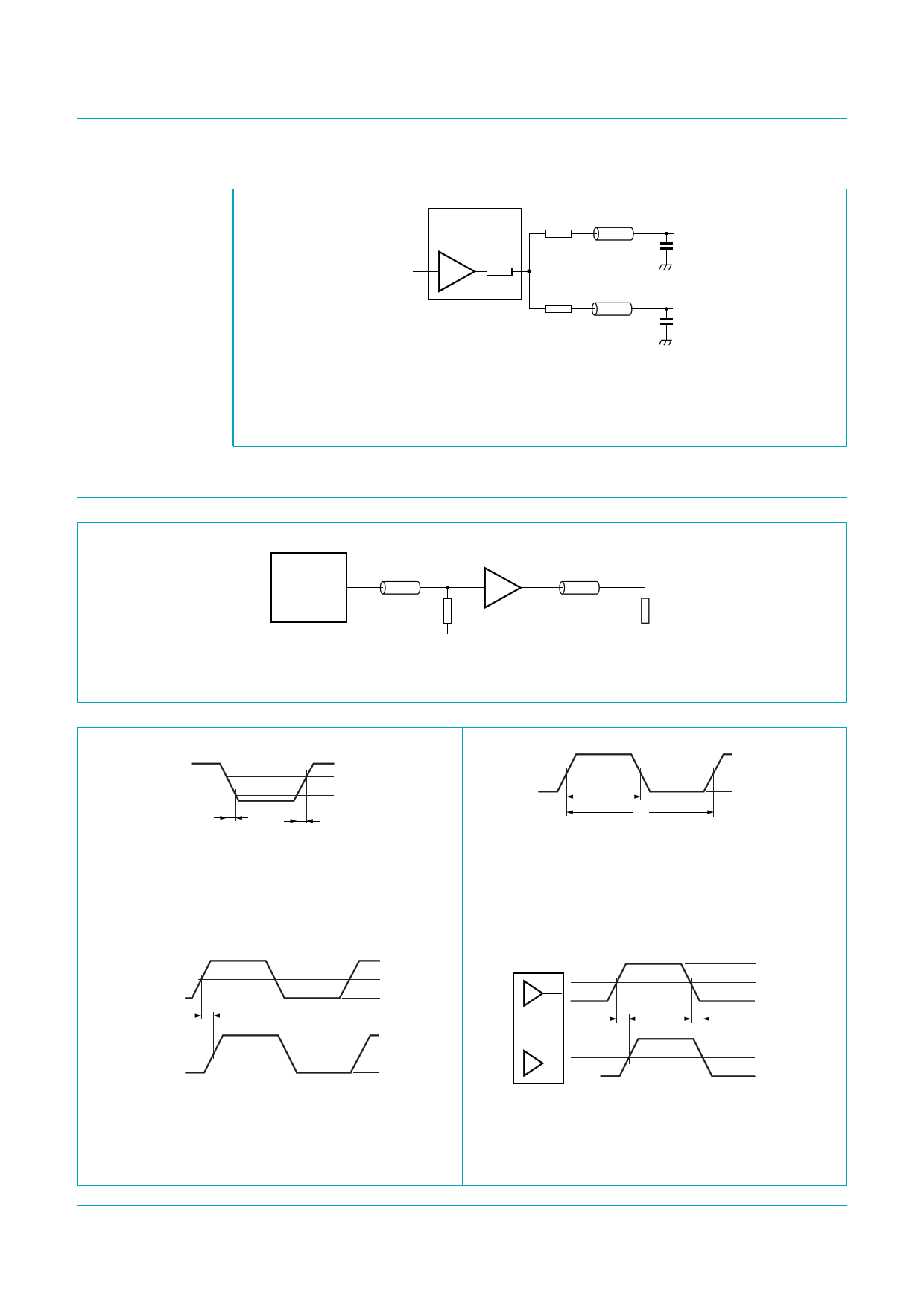

002aaa709

PULSE

GENERATOR

Z = 50 Ω

Zo = 50 Ω

RT = 50 Ω

PCK9446

D.U.T.

Zo = 50 Ω

RT = 50 Ω

VT VT

002aaa710

Fig 6. CLK0, CLK1 PCK9446 AC test reference for VCC = 3.3 V and VCC = 2.5 V

(1)

(2)

tf tr

002aab292

(1) 2.4 V when VCC = 3.3 V; 1.8 V when VCC = 2.5 V.

(2) 0.55 V when VCC = 3.3 V; 0.6 V when VCC = 2.5 V.

Fig 7. Output transition time test reference

tp

To

δo = (tp ÷ To × 100 %)

VCC

0.5VCC

GND

002aab291

The time from the PLL controlled edge to the

non-controlled edge, divided by the time between

PLL controlled edges, expressed as a percentage.

Fig 8. Output duty cycle (δo)

CLK0, CLK1

Qn

tPD

VCC

0.5VCC

GND

VCC

0.5VCC

GND

002aaa712

tsk(o)

VCC

0.5VCC

GND

tsk(o)

VCC

0.5VCC

GND

002aab289

Fig 9. Propagation delay (tPD) test reference

The pin-to-pin skew is defined as the worst case

difference in a propagation delay between any

similar delay path within a single device.

Fig 10. Output skew time (tsk(o))

PCK9446_1

Product data sheet

Rev. 01 — 10 April 2006

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

11 of 17

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet PCK9446.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PCK9446 | LVCMOS clock fan-out buffer | NXP Semiconductors |

| PCK9447 | LVCMOS clock fan-out buffer | NXP Semiconductors |

| PCK9448 | LVCMOS 1 : 12 clock fan-out buffer | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |