|

|

PDF AD7797 Data sheet ( Hoja de datos )

| Número de pieza | AD7797 | |

| Descripción | (AD7796 / AD7797) Sigma-Delta ADC | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD7797 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Low Power, 16-/24-Bit Sigma-Delta ADC

for Bridge Sensors

AD7796/AD7797

FEATURES

RMS noise: 65 nV

Instrumentation amp

Temperature sensor

Internal clock oscillator

Simultaneous 50 Hz/60 Hz rejection

Update rate: 4.17 Hz to 123 Hz

Current: 250 μA typ

Power-down: 1 μA

Power supply: 2.7 V to 5.25 V

–40°C to +85°C temperature range

Independent interface power supply

16-lead TSSOP

INTERFACE

3-wire serial

SPI®, QSPI™, MICROWIRE™, and DSP compatible

Schmitt trigger on SCLK

GENERAL DESCRIPTION

The AD7796/AD7797 are complete, analog front ends for high

precision, bridge sensor applications such as weigh scales. The

AD7796/AD7797 contain a Σ-Δ ADC capable of 16-/24-bit

resolution, respectively. The on-chip instrumentation amplifier

has a fixed gain of 128, allowing small amplitude signals such as

those from bridge sensors to be directly interfaced to the ADC.

Each part has one differential input and contains a temperature

sensor that is internally connected to the ADC. This sensor can

be used to perform temperature compensation of the bridge.

The devices can be operated with the internal clock or an

external clock. The output data rate from the parts is software-

programmable and can be varied from 4.17 Hz to 123 Hz.

The AD7796/AD7797 operate with a power supply from 2.7 V

to 5.25 V. Each part consumes a current of 250 μA typical and is

housed in a 16-lead TSSOP.

APPLICATIONS

Weigh scales

Strain gages

Industrial process control

Instrumentation

Portable instrumentation

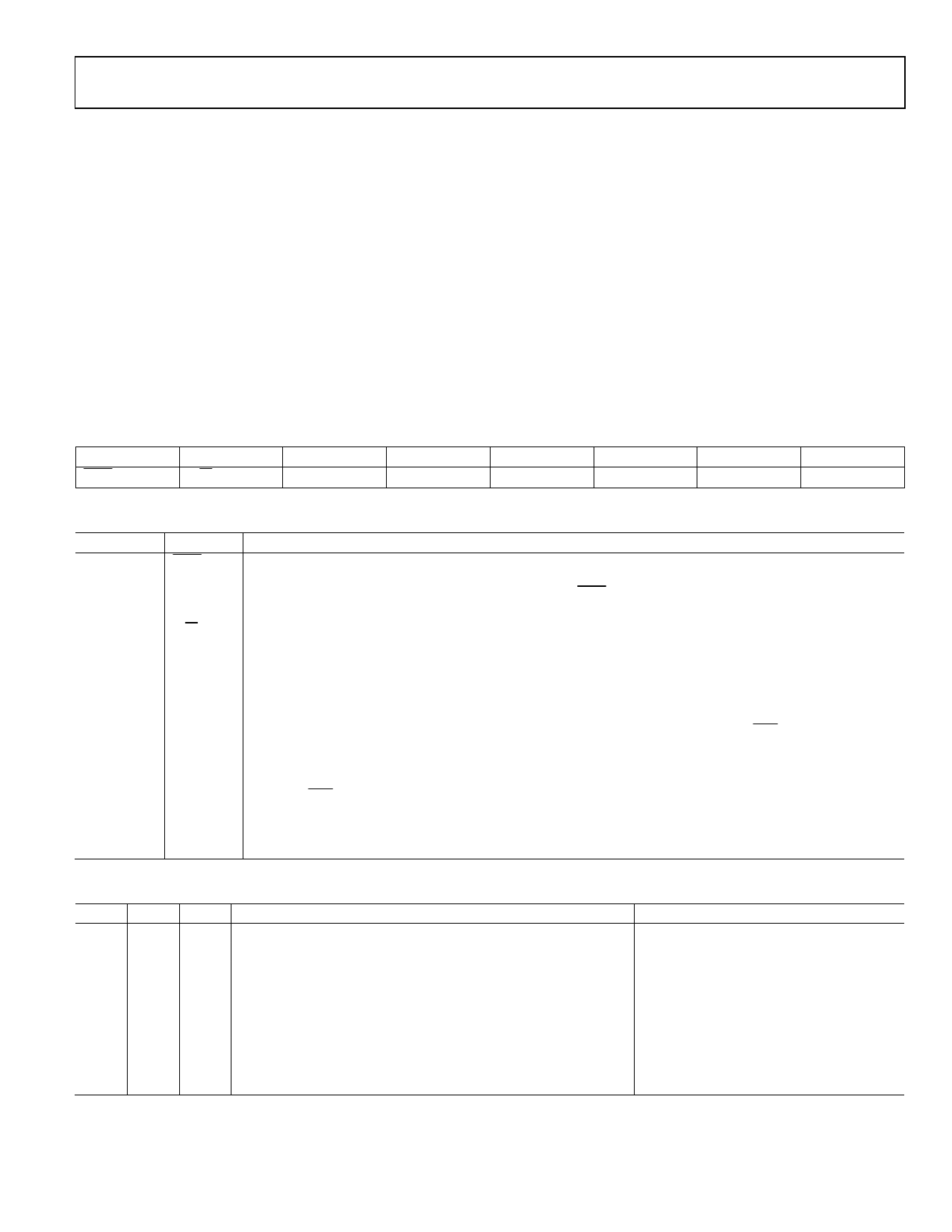

AIN(+)

AIN(–)

FUNCTIONAL BLOCK DIAGRAM

GND AVDD

REFIN(+) REFIN(–)

AVDD

AD7796: 16-BIT ADC

AD7797: 24-BIT ADC

MUX

×128

Σ-Δ

ADC

SERIAL

INTERFACE

AND

CONTROL

LOGIC

DOUT/RDY

DIN

SCLK

CS

GND

AD7796/

AD7797

REFERENCE

TEMP

SENSOR

INTERNAL

CLOCK

Figure 1.

CLK

DVDD

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2006 Analog Devices, Inc. All rights reserved.

1 page

AD7796/AD7797

TIMING CHARACTERISTICS

AVDD = 2.7 V to 5.25 V, DVDD = 2.7 V to 5.25 V, GND = 0 V, Input Logic 0 = 0 V, Input Logic 1 = DVDD, unless otherwise noted.

Table 2.

Parameter1, 2

t3

t4

Read Operation

t1

t2 3

t55, 6

t6

t7

Write Operation

t8

t9

t10

t11

Limit at TMIN, TMAX (B Version)

100

100

0

60

80

0

60

80

10

80

0

10

0

30

25

0

Unit

ns min

ns min

ns min

ns max

ns max

ns min

ns max

ns max

ns min

ns max

ns min

ns min

ns min

ns min

ns min

ns min

Conditions/Comments

SCLK high pulse width

SCLK low pulse width

CS falling edge to DOUT/RDY active time

DVDD = 4.75 V to 5.25 V

DVDD = 2.7 V to 3.6 V

SCLK active edge to data valid delay4

DVDD = 4.75 V to 5.25 V

DVDD = 2.7 V to 3.6 V

Bus relinquish time after CS inactive edge

SCLK inactive edge to CS inactive edge

SCLK inactive edge to DOUT/RDY high

CS falling edge to SCLK active edge setup time4

Data valid to SCLK edge setup time

Data valid to SCLK edge hold time

CS rising edge to SCLK edge hold time

1 Sample tested during initial release to ensure compliance. All input signals are specified with tR = tF = 5 ns (10% to 90% of DVDD) and timed from a voltage level of 1.6 V.

2 See Figure 3 and Figure 4.

3 These numbers are measured with the load circuit of Figure 2 and defined as the time required for the output to cross the VOL or VOH limits.

4 SCLK active edge is falling edge of SCLK.

5 These numbers are derived from the measured time taken by the data output to change 0.5 V when loaded with the circuit of Figure 2. The measured number is then

extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus

relinquish times of the parts and, as such, are independent of external bus loading capacitances.

6 RDY returns high after a read of the ADC. In single conversion mode and continuous conversion mode, the same data can be read again, if required, while RDY is high.

Care should be taken to ensure that subsequent reads do not occur close to the next output update. In continuous read mode, the digital word can be read only once.

ISINK (1.6mA WITH DVDD = 5V,

100µA WITH DVDD = 3V)

TO

OUTPUT

PIN

50pF

1.6V

ISOURCE (200µA WITH DVDD = 5V,

100µA WITH DVDD = 3V)

Figure 2. Load Circuit for Timing Characterization

Rev. A | Page 5 of 24

5 Page

AD7796/AD7797

ON-CHIP REGISTERS

The ADC is controlled and configured via a number of on-chip

registers, which are described on the following pages. In the

following descriptions, set implies a Logic 1 State and cleared

implies a Logic 0 State, unless otherwise stated.

COMMUNICATION REGISTER

RS2, RS1, RS0 = 0, 0, 0

The communication register is an 8-bit write-only register. All

communication to the part must start with a write operation to

this register. The data written to the communication register

determines whether the next operation is a read or write opera-

tion, and selects the register where this operation takes place.

MSB

CR7

WEN(0)

CR6

R/W(0)

CR5

RS2(0)

CR4

RS1(0)

Once the subsequent read or write operation to the selected

register is complete, the interface returns to where it expects a

write operation to the communication register (this is the

default state of the interface). On power-up or after a reset, the

ADC is in this default state waiting for a write operation to the

communication register. In situations where the interface

sequence is lost, a write operation of at least 32 serial clock

cycles with DIN high returns the ADC to this default state by

resetting the entire part. Table 9 outlines the bit designations for

the communication register. CR0 through CR7 indicate the bit

location, with CR denoting that the bits are in the communication

register. CR7 denotes the first bit of the data stream. The number

in brackets indicates the power-on/reset default status of that bit.

CR3

RS0(0)

CR2

CREAD(0)

CR1

0(0)

LSB

CR0

0(0)

Table 9. Communication Register Bit Designations

Bit Location Bit Name Description

CR7

WEN

Write Enable Bit. A 0 must be written to this bit first to ensure that a write to the communication register

occurs. If a 1 is the first bit written, the part does not clock onto subsequent bits in the register; it stays at this

bit location until a 0 is written. Once a 0 is written to the WEN bit, the next seven bits are loaded to the

communication register.

CR6 R/W A 0 in this bit location indicates that the next operation is a write to a specified register. A 1 in this position

indicates that the next operation is a read from the designated register.

CR5 to CR3 RS2 to RS0 Register Address Bits. These address bits determine which ADC registers are being selected during this serial

interface communication. See Table 10.

CR2

CREAD

Continuous Read of the Data Register. When this bit is set to 1 (and the data register is selected), the serial

interface is configured to continuously read the data register. For example, the contents of the data register are

automatically placed on the DOUT pin when the SCLK pulses are applied and after the RDY pin goes low. This

indicates that a conversion is complete. The communication register does not have to be written to for data reads.

To enable continuous read mode, the instruction 01011100 must be written to the communication register.

To exit the continuous read mode, the instruction 01011000 must be written to the communication register

while the RDY pin is low. While in continuous read mode, the ADC monitors activity on the DIN line so it can

receive the instruction to exit continuous read mode. Additionally, a reset occurs if 32 consecutive 1s are seen

on DIN. Therefore, DIN should be held low in continuous read mode until an instruction is written to the device.

CR1 to CR0 0

These bits must be programmed to Logic 0 for correct operation.

Table 10. Register Selection

RS2 RS1 RS0 Register

0 0 0 Communication Register During a Write Operation

0 0 0 Status Register During a Read Operation

0 0 1 Mode Register

0 1 0 Configuration Register

0 1 1 Data Register

1 0 0 ID Register

1 0 1 Reserved

1 1 0 Offset Register

1 1 1 Full-Scale Register

Register Size

8 bits

8 bits

16 bits

16 bits

16 bits (AD7796), 24 bits (AD7797)

8 bits

8 bits

16 bits (AD7796), 24 bits (AD7797)

16 bits (AD7796), 24 bits (AD7797)

Rev. A | Page 11 of 24

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet AD7797.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD779 | 14-Bit 128 kSPS Complete Sampling ADC | Analog Devices |

| AD7790 | 16-Bit Buffered Sigma-Delta ADC | Analog Devices |

| AD7791 | Buffered 24-Bit Sigma-Delta ADC | Analog Devices |

| AD7792 | (AD7792 / AD7793) 16/24-Bit Sigma-Delta ADC | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |