|

|

PDF HM514170C Data sheet ( Hoja de datos )

| Número de pieza | HM514170C | |

| Descripción | Dynamic Random Access Memory | |

| Fabricantes | Hitachi Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HM514170C (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

HM514170C Series

HM51S4170C Series

262,144-word × 16-bit Dynamic Random Access Memory

Rev. 1.0

Jul. 21, 1995

Description

The Hitachi HM51(S)4170C are CMOS dynamic RAM organized as 262,144-word × 16-bit.

HM51(S)4170C have realized higher density, higher performance and various functions by employing 0.8

µm CMOS process technology and some new CMOS circuit design technologies. The HM51(S)4170C

offer fast page mode as a high speed access mode. Multiplexed address input permits the

HM51(S)4170C to be packaged in standard 400-mil 40-pin plastic SOJ and standard 400-mil 44-pin

plastic TSOPII. Internal refresh timer enables HM51S4170C self refresh operation.

Features

• Single 5 V (±10%)

• High speed

— Access time: 70 ns/80 ns (max)

• Low power dissipation

— Active mode: 660 mW/578 mW (max)

— Standby mode: 11 mW (max)

1.1 mW (max) (L-version)

• Fast page mode capability

• 1024 refresh cycles: 16 ms

128 ms (L-version)

• 2 WE -byte control

• 2 variations of refresh

— RAS -only refresh

— CAS -before-RAS refresh

• Battery backup operation (L-version)

• Self refresh operation (HM51S4170C)

1 page

www.DataSheet4U.com

HM514170C, HM51S4170C Series

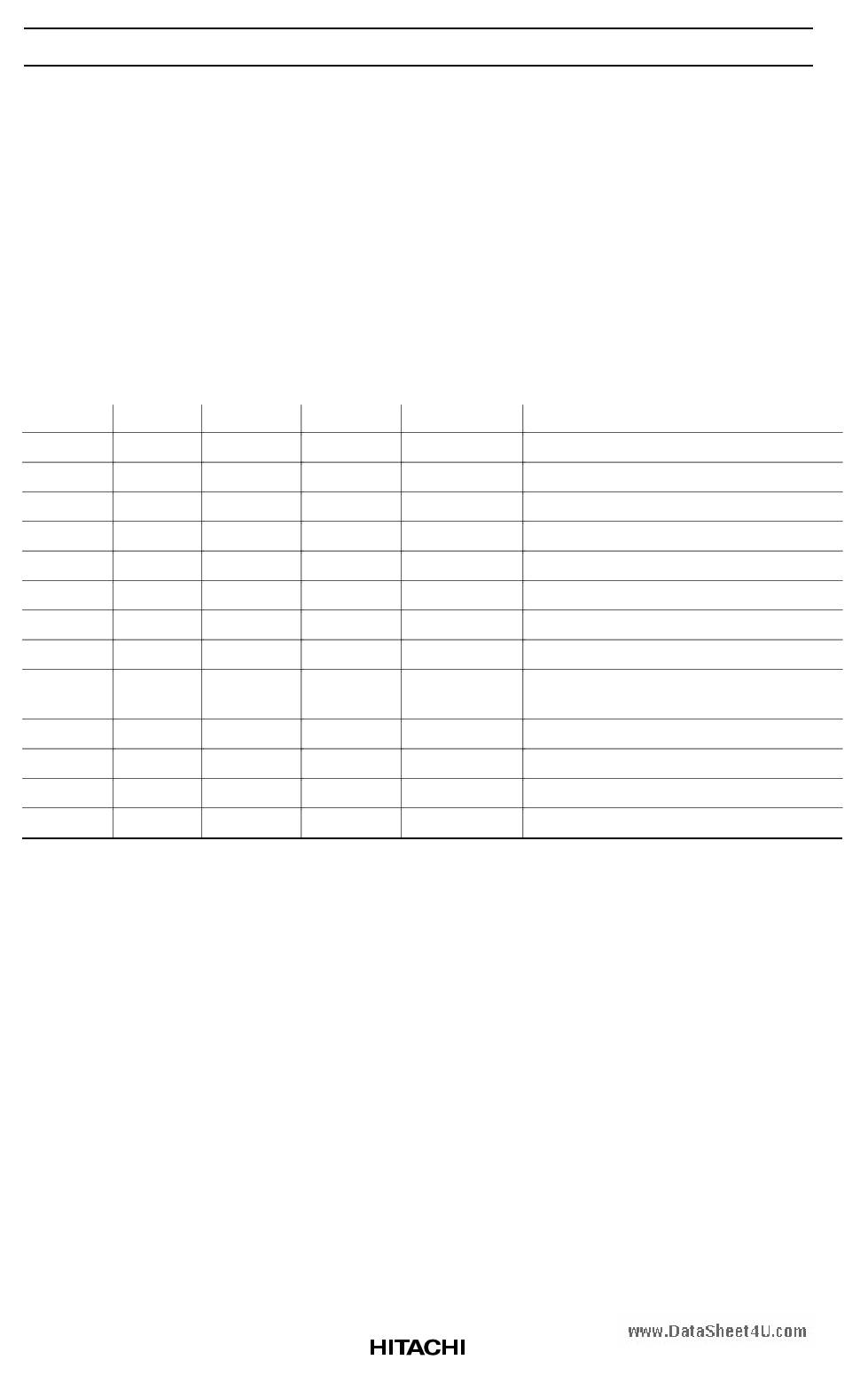

1. Read cycle

2. Early write cycle

3. Delayed write cycle

4. Read-modify-write cycle

5. RAS -only refresh cycle

6. CAS -before-RAS refresh cycle

7. Self refresh cycle (HM51S4170C)

8. Fast page mode read cycle

9. Fast page mode early write cycle

10. Fast page mode delayed write cycle

11. Fast page mode read-modify-write cycle

Inputs

RAS

CAS

UWE

LWE

Output

Operation

H HD

D

Open

Standby

H L H H Valid Standby

L L H H Valid Read cycle

L L L*2 L*2 Open Early write cycle

L

L L*2

L*2

Undefined

Delayed write cycle

L

L

H to L

H to L

Valid

Read-modify-write cycle

L HD

D

Open

RAS-only refresh cycle

H to L

L

D

D

Open

CAS-before-RAS refresh cycle

Self refresh cycle (HM51S4170C)

L

H to L

H

H

Valid

Fast page mode read cycle

L

H to L

L*2

L*2

Open

Fast page mode early write cycle

L

H to L

L*2

L*2

Undefined

Fast page mode delayed write cycle

L

H to L

H to L

H to L

Valid

Fast page mode read modify-write cycle

Notes: 1. H: High (inactive) L: Low (active) D: H or L

2. tWCS ≥ 0 ns Early write cycle

tWCS < 0 ns Delay write cycle

3. Mode is determined by the OR function of the UWE and LWE. (Mode is set by the earliest of

UWE and LWE active edge and reset by the latest of UWE and LWE inactive edge.) However

write OPERATION and output HIZ control are done independently by each UWE, LWE.

5

5 Page

www.DataSheet4U.com

HM514170C, HM51S4170C Series

Self refresh Mode

HM51S4170C

-7 -8

Parameter

Symbol Min Max Min Max Unit Notes

RAS pulse width (self refresh)

t RASS

100 —

100 —

µs 23, 24,

25

RAS precharge time (self refresh)

tRPS 130 — 150 — ns

CAS hold time (self refresh)

tCHS –50 — –50 — ns

Notes: 1. AC measurements assume tT = 5 ns.

2. Assumes that tRCD ≤ tRCD (max) and tRAD ≤ tRAD (max). If tRCD or tRAD is greater than the maximum

recommended value shown in this table, tRAC exceeds the value shown.

3. Measured with a load circuit equivalent to 2 TTL loads and 100 pF.

4. Assumes that tRCD ≥ tRCD (max) and tRAD ≤ tRAD (max).

5. Assumes that tRCD ≤ tRCD (max) and tRAD ≥ tRAD (max).

6. tOFF (max) defines the time at which the output achieves the open circuit condition and is not

referred to output voltage levels.

7. VIH (min) and VIL (max) are reference levels for measuring timing of input signals. Also,

transition times are measured between VIH and VIL.

8. Operation with the tRCD (max) limit insures that tRAC (max) can be met, tRCD (max) is specified as

a reference point only, if tRCD is greater than the specified tRCD (max) limit, then access time is

controlled exclusively by tCAC.

9. Operation with the tRAD (max) limit insures that tRAC (max) can be met, tRAD (max) is specified as

a reference point only, if tRAD is greater than the specified tRAD (max) limit, then access time is

controlled exclusively by tAA.

10. tWCS, tRWD, tCWD and tAWD are not restrictive operating parameters. They are included in the data

sheet as electrical characteristics only: if tWCS ≥ tWCS (min), the cycle is an early write cycle and

the data out pin will remain open circuit (high impedance) throughout the entire cycle; if tRWD ≥

tRWD (min), tCWD ≥ tCWD (min), tAWD ≥ tAWD (min) and tCPW ≥ tCPW (min), the cycle is a read-modify-

write and the data output will contain data read from the selected cell; if neither of the above

sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate.

11. These parameters are referred to CAS leading edge in an early write cycle and to WE leading

edge in a delayed write or a read-modify-write cycle.

12. tRASC defines RAS pulse width in fast page mode cycles.

13. Access time is determined by the longer of tAA or tCAC or tACP.

14. After power up pause for 100 µs, then DRAM initialization requires a minimum of eight RAS

only refresh or eight CAS-before-RAS refresh cycles. If the user will implement CAS-before-

RAS timing in their system, then the eight initialization cycles MUST be CAS-before-RAS

cycles

15. In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying

data to the device.

16. Either tRCH or tRRH must be satisfied for a read cycle.

17. The supply voltage with all VCC pins must be on the same level. The supply voltage with all VSS

pins must be on the same level.

18. A word of data can be written only when UWE and LWE go low at the same time. This implies

that early write cycles cannot be combined with delayed write cycles in the same cycles

because all data is latched at the fall of the first WE. In other words, staggering the WE signals

in one cycle is not permitted.

19. tRCH, tRRH, tWCS, tRWD, tCWD and tAWD are determined by the earlier falling edge of UWE and LWE.

20. tWCH and tRCS are determined by the later rising edge of UWE or LWE.

21. tWP, tRWL, tCWL, tOEH, tDS, tDH and tCPW should be satisfied by both UWE and LWE.

11

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet HM514170C.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HM514170C | Dynamic Random Access Memory | Hitachi Semiconductor |

| HM514170D | (HM514170D / HM514270D) Dynamic RAM | Hitachi Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |