|

|

PDF ADC08B3000 Data sheet ( Hoja de datos )

| Número de pieza | ADC08B3000 | |

| Descripción | 3 GSPS A/D Converter | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ADC08B3000 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

ADVANCE INFORMATION

June 2006

ADC08B3000

High Performance, Low Power, 8-Bit, 3 GSPS A/D

Converter with 4K Buffer

General Description

Note: This product is currently in development. - ALL

specifications are design targets and are subject to

change.

The ADC08B3000 is a single, low power, high performance

CMOS analog-to-digital converter that digitizes signals to 8

bits resolution at sampling rates up to 3.4 GSPS. Consuming

a typical 1.8 Watts at 3 GSPS from a single 1.9 Volt supply,

this device is guaranteed to have no missing codes over the

full operating temperature range. The unique folding and

interpolating architecture, the fully differential comparator

design, the innovative design of the internal sample-and-

hold amplifier and the self-calibration scheme enable a very

flat response of all dynamic parameters upto Nyquist, pro-

ducing a high 7.0 ENOB with a 748 MHz input signal and a

3 GHz sample rate while providing a 10-18 B.E.R. 3 GSPS is

achieved through using a 1.5GHz clock. Output formatting is

offset binary. The device contains a 4K FIFO Capture Buffer

which is used to feed two 8 bit CMOS output busses at a rate

up to 200MHz.

The converter typically consumes less than 20 mW in the

Power Down Mode and is available in a 128-lead, thermally

enhanced exposed pad LQFP and operates over the Indus-

trial (-40˚C ≤ TA ≤ +85˚C) temperature range.

Features

n Internal Sample-and-Hold

n Single +1.9V ±0.1V Operation

n Choice of SDR or DDR output clocking

n Internal selectable 4K Data Buffer

n Clock Phase Adjust for Multiple ADC Synchronization

n Guaranteed No Missing Codes

n Serial Interface for Extended Control

n Fine Adjustment of Input Full-Scale Range and Offset

n Duty Cycle Corrected Sample Clock

Key Specifications

n Resolution

n Max Conversion Rate

n Bit Error Rate

n ENOB @ 748 MHz Input

n SNR @ 748 MHz

n Full Power Bandwidth

n Power Consumption

— Operating

— Power Down Mode

8 Bits

3 GSPS (min)

10-18 (typ)

7.0 Bits (typ)

44 dB (typ)

TBD

1.8 W (typ)

20 mW (typ)

Applications

n Ranging Applications

n Test and measurement Applications

Block Diagram

© 2006 National Semiconductor Corporation DS201601

20160153

www.national.com

1 page

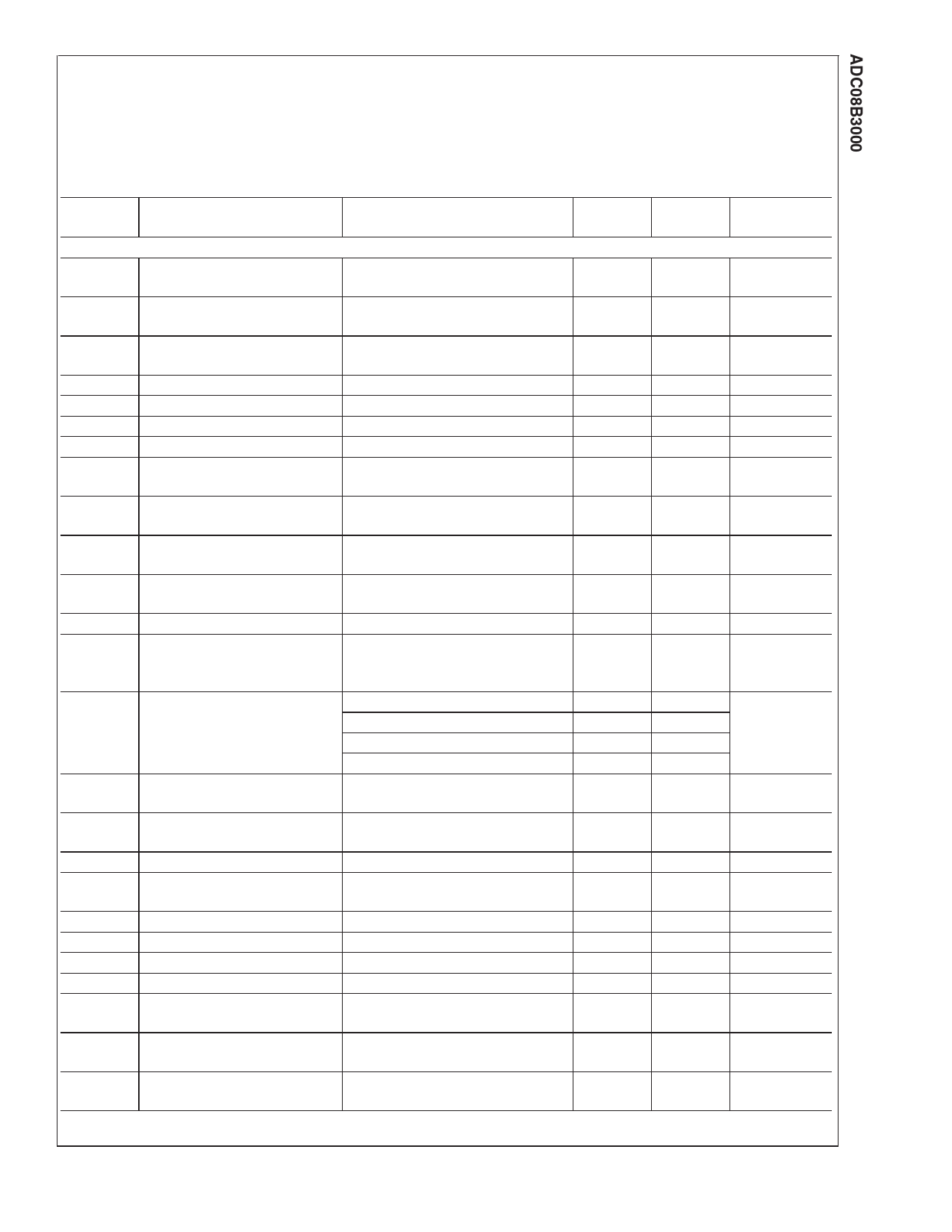

Pin Descriptions and Equivalent Circuits (Continued)

Pin Functions

Pin No.

Symbol

Equivalent Circuit

Description

72 D2<0>

71 D2<1>

70 D2<2>

69 D2<3>

68 D2<4>

67 D2<5>

66 D2<6>

65 D2<7>

Digital Data Output 2. When the REN input is asserted and

2X8 Output Enable is set in the FIFO register, data from

banks Da and Dc are read from the capture buffer and

presented on this port synchronous with each rising edge of

RCLK. When 2X8 Output Enable is not set in the FIFO

register, data output 2 is high-Z.

75 DRDY2

Data Ready 2. DRDY is generated by RCLK and is

synchronized to the output data. The use of this pin assists in

eliminating the latency uncertainty between when RCLK

transitions and when data transitions on the output

89 D1<0>

90 D1<1>

91 D1<2>

92 D1<3>

93 D1<4>

94 D1<5>

95 D1<6>

96 D1<7>

Digital Data Output 1. When the REN input is asserted, data

is read from the capture buffer and presented on this port

synchronous with each rising edge of RCLK. When 2X8

Output Eanble is set in the FIFO resgister, data from banks

Db and Dd only are presented on this port. When REN is

deasserted, this output holds the data from the previous read.

When 2X8 Output Enable is not set in the FIFO register, port

presents data from Da, Db, Dc, Dd banks.

86 DRDY1

79 WENSYNC

80 OR

81 RESET

82 RCLK

Data Ready 1. DRDY is generated by RCLK and is

synchronized to the output data. The use of this pin assists in

eliminating the latency uncertainty between when RCLK

transitions and when data transitions on the output

Synchronized WEN. The control input WEN is synchronized

on-chip with the internal Sampling Clock and is provided at

this output.

Out Of Range output. A logic high on this pin indicates that

the differential input is out of range (outside the range ±300

mV or ±400 mV as defined by the FSR pin). This signal is

asserted if the input signal has over ranged at any time

during the data capture operation. This pin is cleared after the

Capture Buffer is read or after asserting the RESET pin.

A logic high at this input resets all Capture Buffer control logic

in the chip.

Read Clock. Free running clock that is used to read data from

the Capture Buffer. The parallel data on the data output port

and the EF flag are asserted synchronous to this clock.

5 www.national.com

5 Page

Converter Electrical Characteristics (Continued)

NOTE: This product is currently in development and the parameters specified in this section are DESIGN TARGETS.

The specifications in this section cannot be guaranteed until device characterization has taken place. The following

specifications apply after calibration for VA = VDR = +1.9VDC, OutV = 1.9V, VIN FSR (a.c. coupled) = differential 870mVP-P, CL

= 10 pF, Differential, a.c. coupled Sinewave Input Clock, fCLK = 1.5 GHz at 0.5VP-P with 50% duty cycle, VBG = Floating, Non-

Extended Control Mode, SDR Mode, REXT = 3300Ω ±0.1%, Analog Signal Source Impedance = 100Ω Differential. Boldface

limits apply for TA = TMIN to TMAX. All other limits TA = 25˚C, unless otherwise noted. (Notes 6, 7)

Symbol

Parameter

Conditions

Typical

(Note 8)

Limits

(Note 8)

Units

(Limits)

AC ELECTRICAL CHARACTERISTICS

fCLK1

Maximum Input Clock

Frequency

Sampling rate is 2x clock input

1.7 1.5 GHz (min)

fCLK2

Minimum Input Clock

Frequency

Sampling rate is 2x clock input

500

MHz

Input Clock Duty Cycle

500MHz ≤ Input clock frequency ≤

1.5 GHz (Note 12)

50

20 % (min)

80 % (max)

tCL

tCH

tRS

tRH

tRPW

Input Clock Low Time

Input Clock High Time

Reset Setup Time

Reset Hold Time

Reset Pulse Width

(Note 11)

(Note 11)

(Note 11)

(Note 11)

(Note 11)

333 133 ps (min)

333 133 ps (min)

150 ps

250 ps

Clock Cycles

4

(min)

Differential Low to High

tLHT Transition Time

10% to 90%, CL = 2.5 pF

250

ps

Differential High to Low

tHLT Transition Time

10% to 90%, CL = 2.5 pF

250

ps

Input CLK+ Fall to Acquisition of

tAD

Sampling (Aperture) Delay

Data

1.3

ns

tAJ Aperture Jitter

0.4

Input Clock to Data Output

50% of Input Clock transition to 50%

tOD

Delay (in addition to Pipeline

of Data transition

3.1

Delay)

ps rms

ns

Dd Outputs

13

Pipeline Delay (Latency)

Db Outputs

14 Input Clock

(Note 11)

Dc Outputs

13.5

Cycles

Da Outputs

14.5

Over Range Recovery Time

Differential VIN step from ±1.2V to

0V to get accurate conversion

1

Input Clock

Cycle

PD low to Rated Accuracy

tWU Conversion (Wake-Up Time)

500 ns

fSCLK

tSSU

Serial Clock Frequency

Data to Serial Clock Setup

Time

(Note 11)

(Note 11)

100 MHz

2.5 ns (min)

tSH Data to Serial Clock Hold Time (Note 11)

Serial Clock Low Time

1 ns (min)

4 ns (min)

Serial Clock High Time

4 ns (min)

tCAL

tCAL_L

Calibration Cycle Time

CAL Pin Low Time

See Figure 3 (Note 11)

1.4 x 105

Clock Cycles

Clock Cycles

80

(min)

tCAL_H

CAL Pin High Time

See Figure 3 (Note 11)

Clock Cycles

80

(min)

tCalDly

Calibration delay determined by See Section 1.1.1, Figure 3, (Note

pin 127

11)

225 Clock Cycles

(min)

11 www.national.com

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ADC08B3000.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADC08B3000 | 3 GSPS A/D Converter | National Semiconductor |

| ADC08B3000 | ADC08B3000 8-Bit 3 GSPS High Perf Low Pwr ADC w/4K Buffer (Rev. M) | Texas Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |