|

|

PDF ADF4193 Data sheet ( Hoja de datos )

| Número de pieza | ADF4193 | |

| Descripción | Fast Settling PLL Frequency Synthesizer | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADF4193 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Data Sheet

Low Phase Noise, Fast Settling PLL

Frequency Synthesizer

ADF4193

FEATURES

New, fast settling, fractional-N PLL architecture

Single PLL replaces ping-pong synthesizers

Frequency hop across GSM band in 5 µs with phase settled

by 20 µs

0.5° rms phase error at 2 GHz RF output

Digitally programmable output phase

RF input range up to 3.5 GHz

3-wire serial interface

On-chip, low noise differential amplifier

Phase noise figure of merit: −216 dBc/Hz

Loop filter design possible using ADIsimPLL™

Qualified for automotive applications

APPLICATIONS

GSM/EDGE base stations

PHS base stations

Instrumentation and test equipment

GENERAL DESCRIPTION

The ADF4193 frequency synthesizer can be used to implement

local oscillators in the upconversion and downconversion

sections of wireless receivers and transmitters. Its architecture

is specifically designed to meet the GSM/EDGE lock time

requirements for base stations. It consists of a low noise, digital

phase frequency detector (PFD), and a precision differential

charge pump. There is also a differential amplifier to convert

the differential charge pump output to a single-ended voltage

for the external voltage-controlled oscillator (VCO).

The Σ-Δ based fractional interpolator, working with the N

divider, allows programmable modulus fractional-N division.

Additionally, the 4-bit reference (R) counter and on-chip

frequency doubler allow selectable reference signal (REFIN)

frequencies at the PFD input. A complete phase-locked loop

(PLL) can be implemented if the synthesizer is used with an

external loop filter and a VCO. The switching architecture

ensures that the PLL settles inside the GSM time slot guard

period, removing the need for a second PLL and associated

isolation switches. This decreases cost, complexity, PCB area,

shielding, and characterization on previous ping-pong GSM

PLL architectures.

REFIN

MUXOUT

CLK

DATA

LE

FUNCTIONAL BLOCK DIAGRAM

SDVDD DVDD1 DVDD2 DVDD3 AVDD1

VP1 VP2 VP3

RSET

×2

DOUBLER

HIGH Z

OUTPUT

MUX

24-BIT

DATA

REGISTER

4-BIT R

COUNTER

÷2

DIVIDER

VDD

DGND

LOCK DETECT

RDIV

NDIV

FRACTIONAL

INTERPOLATOR

REFERENCE

+ PHASE

FREQUENCY

– DETECTOR

CHARGE +

PUMP –

DIFFERENTIAL

AMPLIFIER –

+

N COUNTER

FRACTION MODULUS

REG

REG

INTEGER

REG

ADF4193

SW1

CPOUT+

CPOUT–

SW2

CMR

AIN–

AIN+

AOUT

SW3

RFIN+

RFIN–

AGND1

AGND2

DGND1

DGND2

Figure 1.

DGND3 SDGND SWGND

Rev. G

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibilityisassumedbyAnalogDevices for itsuse,nor foranyinfringementsofpatentsor other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2005–2015 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

1 page

ADF4193

Data Sheet

SPECIFICATIONS

AVDD = DVDD = SDVDD = 3 V ± 10%, VP1, VP2 = 5 V ± 10%, VP3 = 5.35 V ± 5%, AGND = DGND = GND = 0 V, RSET = 2.4 kΩ, dBm

referred to 50 Ω, TA = TMIN to TMAX, unless otherwise noted.

Table 1.

Parameter

RF CHARACTERISTICS

RF Input Frequency (RFIN)

RF Input Sensitivity

Maximum Allowable Prescaler

Output Frequency3

REFIN CHARACTERISTICS

REFIN Input Frequency

B Version1

0.4/3.5

−10/0

470

10/300

C Version2

0.4/3.5

−10/0

470

10/300

REFIN Edge Slew Rate

REFIN Input Sensitivity

REFIN Input Capacitance

REFIN Input Current

PHASE DETECTOR

Phase Detector Frequency

CHARGE PUMP

ICP Up/Down

High Value

Low Value

Absolute Accuracy

RSET Range

ICP Three-State Leakage

ICP Up vs. Down Matching

ICP vs. VCP

ICP vs. Temperature

DIFFERENTIAL AMPLIFIER

Input Current

Output Voltage Range

VCO Tuning Range

Output Noise

LOGIC INPUTS

VIH, Input High Voltage

VIL, Input Low Voltage

IINH, IINL, Input Current

CIN, Input Capacitance

LOGIC OUTPUTS

VOH, Output High Voltage

VOL, Output Low Voltage

POWER SUPPLIES

AVDD

DVDD

VP1, VP2

VP3

IDD (AVDD + DVDD + SDVDD)

IDD (VP1 + VP2)

IDD (VP3)

IDD Power-Down

300

0.7/VDD

0 to VDD

10

±100

26

300

0.7/VDD

0 to VDD

10

±100

30

6.6 6.6

104 104

55

1/4 1/4

11

0.1 0.1

11

11

1

1.4/(VP3 − 0.3)

1.8/(VP3 − 0.8)

7

1

1.4/(VP3 − 0.3)

1.8/(VP3 − 0.8)

7

1.4 1.4

0.7 0.7

±1 ±2

10 10

VDD − 0.4

0.4

VDD − 0.4

0.4

2.7/3.3

AVDD

4.5/5.5

5.0/5.65

27

27

30

10

2.7/3.3

AVDD

4.5/5.5

5.0/5.65

35

30

35

10

Unit Test Conditions/Comments

GHz min/max

dBm min/max

MHz max

See Figure 21 for input circuit

MHz min/max

V/µs min

V p-p min/max

V max

pF max

µA max

For f > 120 MHz, set REF/2 bit = 1. For f <

10 MHz, use a dc-coupled square wave

AC-coupled

CMOS-compatible

MHz max

mA typ

µA typ

% typ

kΩ min/max

nA typ

% typ

% typ

% typ

nA typ

V min/max

V min/max

nV/√Hz typ

V min

V max

µA max

pF max

V min

V max

V min/V max

V min/V max

V min/V max

mA max

mA max

mA max

µA typ

With RSET = 2.4 kΩ

With RSET = 2.4 kΩ

Nominally RSET = 2.4 kΩ

0.75 V ≤ VCP ≤ VP – 1.5 V

0.75 V ≤ VCP ≤ VP – 1.5 V

0.75 V ≤ VCP ≤ VP – 1.5 V

At 20 kHz offset

IOH = 500 µA

IOL = 500 µA

AVDD ≤ VP1, VP2 ≤ 5.5 V

VP1, VP2 ≤ VP3 ≤ 5.65 V

22 mA typ

22 mA typ

24 mA typ

Rev. G | Page 4 of 29

5 Page

ADF4193

5

4 VTUNE

3

CPOUT+

2

1

0

–1 0

CPOUT–

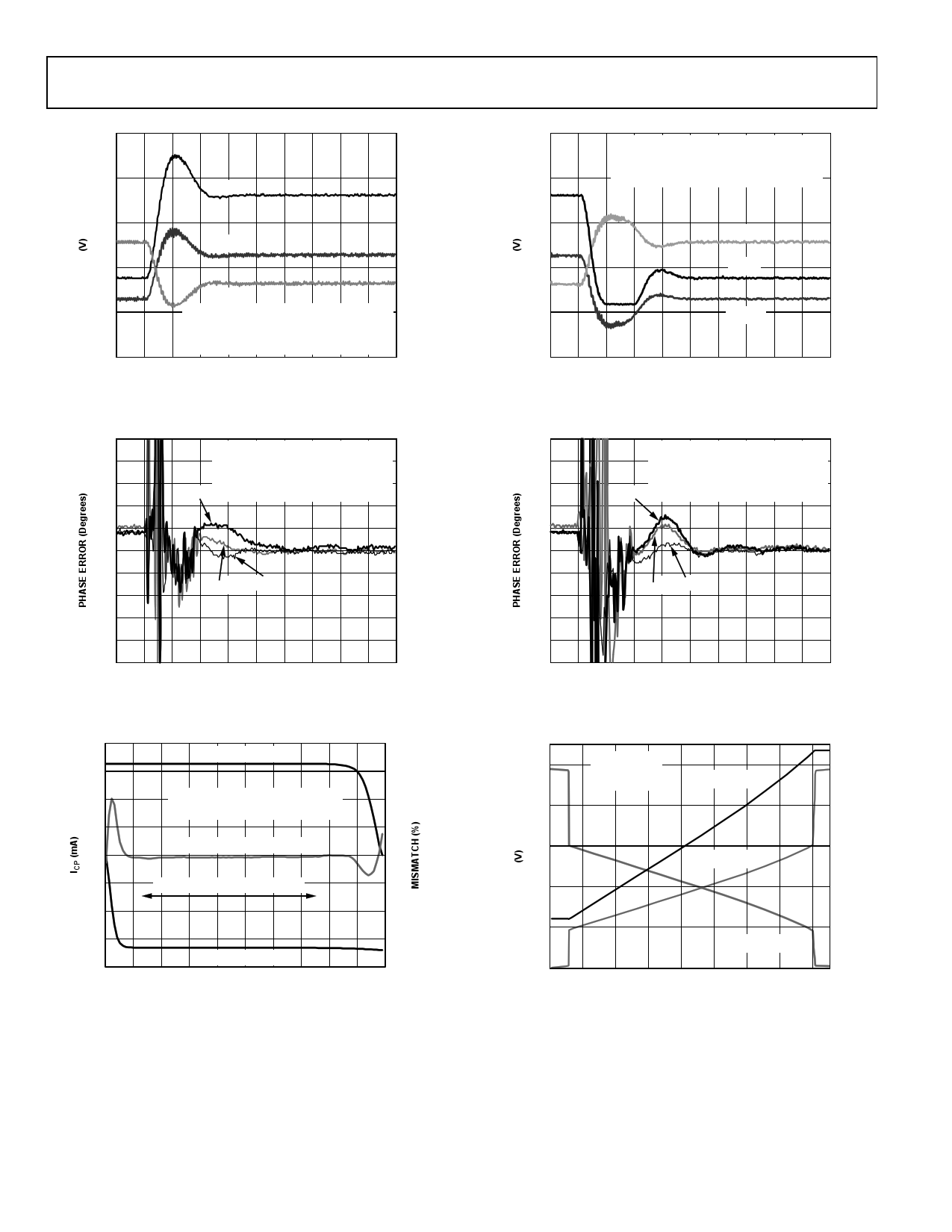

DCS1800 Tx SETUP, 60kHz LOOP BW.

MEASURED ON EVAL-ADF4193-EB1

EVALUATION BOARD.

TIMERS: ICP = 28, SW1/SW2, SW3 = 35.

FREQUENCY LOCK IN WIDE BW MODE @ 4s.

123456789

TIME (s)

Figure 10. VTUNE Settling Transient for a 75 MHz Jump from 1818 MHz to

1893 MHz with Sirenza 1843T VCO

50

DCS1800 Tx SETUP, 60kHz LOOP BW.

40

MEASURED ON EVAL-ADF4193-EB1

EVALUATION BOARD WITH AD8302

PHASE DETECTOR.

30 TIMERS: ICP = 28, SW1/SW2, SW3 = 35.

+25C PEAK PHASE ERROR < 5 @ 17.8s

20

10

0

–10

–20 –40C +85C

–30

–40

–50

–5

0

5 10 15 20 25 30 35 40 45

TIME (s)

Figure 11. Phase Settling Transient for a 75 MHz Jump from 1818 MHz to

1893 MHz (VTUNE 1.8 V to 3.7 V with Sirenza 1843T VCO)

8 2.0

ICPOUT + P, ICPOUT – P

6 1.5

4

IUP = | ICPOUT + P | + | ICPOUT – N |

1.0

IDOWN = | ICPOUT – P | + | ICPOUT + N |

2 0.5

CHARGE PUMP MISMATCH (%)

0

0

–2 NORMAL OPERATING RANGE

–4

–0.5

–1.0

–6 –1.5

ICPOUT + N, ICPOUT – N

–8 –2.0

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

CPOUT + / CPOUT – VOLTAGE (V)

Figure 12. Differential Charge Pump Output Compliance Range and

Charge Pump Mismatch with VP1 = VP2 = 5 V

Data Sheet

5

DCS1800 Tx SETUP, 60kHz LOOP BW.

MEASURED ON EVAL-ADF4193-EB1

EVALUATION BOARD.

4

TIMERS: ICP = 28, SW1/SW2, SW3 = 35.

FREQUENCY LOCK IN WIDE BW MODE @ 5s.

3

CPOUT–

2 VTUNE

1 CPOUT+

0

–1 0 1 2 3 4 5 6 7 8 9

TIME (s)

Figure 13. VTUNE Settling Transient for a 75 MHz Jump Down from 1893 MHz to

1818 MHz, the Bottom of the Allowed Tuning Range with the Sirenza 1843T VCO

50

DCS1800 Tx SETUP, 60kHz LOOP BW.

40

MEASURED ON EVAL-ADF4193-EB1

EVALUATION BOARD WITH AD8302

PHASE DETECTOR.

30 TIMERS: ICP = 28, SW1/SW2, SW3 = 35.

+25C PEAK PHASE ERROR < 5 @ 19.2s

20

10

0

–10

–20 –40C +85C

–30

–40

–50

–5

0

5 10 15 20 25 30 35 40 45

TIME (s)

Figure 14. Phase Settling Transient for a 75 MHz Jump from 1893 MHz to

1818 MHz (VTUNE = 3.7 V to 1.8 V with Sirenza 1843T VCO)

5

VP1 = VP2 = 5V

VP3 = 5.5V

VCMR = 3.3V

AOUT (= VTUNE)

4

3

CPOUT+ (= AIN+)

2

1

CPOUT– (= AIN–)

0

1780

1800

1820

1840 1860 1880 1900

FREQUENCY (MHz)

1920

1940

Figure 15. Tuning Range with a Sirenza 1843T VCO and a 5.5 V Differential

Amplifier Power Supply Voltage

Rev. G | Page 10 of 29

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ADF4193.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADF4193 | Fast Settling PLL Frequency Synthesizer | Analog Devices |

| ADF4196 | 6 GHz PLL Frequency Synthesizer | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |