|

|

PDF ADCMP603 Data sheet ( Hoja de datos )

| Número de pieza | ADCMP603 | |

| Descripción | Single-Supply TTL/CMOS Comparator | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADCMP603 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Rail-to-Rail, Very Fast, 2.5 V to 5.5 V,

Single-Supply TTL/CMOS Comparator

ADCMP603

FEATURES

Fully specified rail to rail at VCC = 2.5 V to 5.5 V

Input common-mode voltage from −0.2 V to VCC + 0.2 V

Low glitch CMOS-/TTL-compatible output stage

Complementary outputs

3.5 ns propagation delay

12 mW at 3.3 V

Shutdown pin

Single-pin control for programmable hysteresis and latch

Power supply rejection > 50 dB

−40°C to +125°C operation

APPLICATIONS

High speed instrumentation

Clock and data signal restoration

Logic level shifting or translation

Pulse spectroscopy

High speed line receivers

Threshold detection

Peak and zero-crossing detectors

High speed trigger circuitry

Pulse-width modulators

Current-/voltage-controlled oscillators

Automatic test equipment (ATE)

GENERAL DESCRIPTION

The ADCMP603 is a very fast comparator fabricated on

XFCB2, an Analog Devices, Inc. proprietary process. This

comparator is exceptionally versatile and easy to use. Features

include an input range from VEE − 0.5 V to VCC + 0.2 V, low noise

complementary TTL-/CMOS-compatible output drivers, latch

inputs with adjustable hysteresis and a shutdown input.

The device offers 3.5 ns propagation delay with 10 mV

overdrive on 4 mA typical supply current.

A flexible power supply scheme allows the device to operate

with a single +2.5 V positive supply and a −0.5 V to +2.8 V

input signal range up to a +5.5 V positive supply with a −0.5 V

to +5.8 V input signal range. Split input/output supplies with no

sequencing restrictions support a wide input signal range while

still allowing independent output swing control and power

savings.

FUNCTIONAL BLOCK DIAGRAM

VCCI

VCCO

VP NONINVERTING

INPUT

VN INVERTING

INPUT

ADCMP603

TTL

Q OUTPUT

Q OUTPUT

LE/HYS INPUT

SDN INPUT

Figure 1.

The device passes 4.5 kV HBM ESD testing and the absolute

maximum ratings include current limits for all pins.

The complementary TTL-/CMOS-compatible output stage is

designed to drive up to 5 pF with full timing specs and to

degrade in a graceful and linear fashion as additional

capacitance is added. The comparator input stage offers robust

protection against large input overdrive, and the outputs do not

phase reverse when the valid input signal range is exceeded.

Latch and programmable hysteresis features are also provided

with a unique single-pin control option.

The ADCMP603 is available in a 12-lead LFCSP package.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2006 Analog Devices, Inc. All rights reserved.

1 page

ADCMP603

TIMING INFORMATION

Figure 2 illustrates the ADCMP603 latch timing relationships. Table 2 provides definitions of the terms shown in Figure 2.

LATCH ENABLE

tS

tH

tPL

1.1V

DIFFERENTIAL

INPUT VOLTAGE

VIN

VOD

VN ± VOS

Q OUTPUT

Q OUTPUT

Table 2. Timing Descriptions

Symbol Timing

tPDH Input to output high delay

tPDL Input to output low delay

tPLOH Latch enable to output high delay

tPLOL Latch enable to output low delay

tH Minimum hold time

tPL Minimum latch enable pulse width

tS Minimum setup time

tR Output rise time

tF Output fall time

VOD Voltage overdrive

tPDL

tPLOH

tPDH

tF

tR

Figure 2. System Timing Diagram

tPLOL

50%

50%

Description

Propagation delay measured from the time the input signal crosses the reference (± the

input offset voltage) to the 50% point of an output low-to-high transition.

Propagation delay measured from the time the input signal crosses the reference (± the

input offset voltage) to the 50% point of an output high-to-low transition.

Propagation delay measured from the 50% point of the latch enable signal low-to-high

transition to the 50% point of an output low-to-high transition.

Propagation delay measured from the 50% point of the latch enable signal low-to-high

transition to the 50% point of an output high-to-low transition.

Minimum time after the negative transition of the latch enable signal that the input signal

must remain unchanged to be acquired and held at the outputs.

Minimum time that the latch enable signal must be high to acquire an input signal change.

Minimum time before the negative transition of the latch enable signal occurs that an

input signal change must be present to be acquired and held at the outputs.

Amount of time required to transition from a low to a high output as measured at the 20%

and 80% points.

Amount of time required to transition from a high to a low output as measured at the 20%

and 80% points.

Difference between the input voltages VA and VB.

Rev. 0 | Page 5 of 16

5 Page

OPTIMIZING PERFORMANCE

As with any high speed comparator, proper design and layout

techniques are essential for obtaining the specified performance.

Stray capacitance, inductance, inductive power and ground

impedances, or other layout issues can severely limit performance

and often cause oscillation. Large discontinuities along input

and output transmission lines can also limit the specified pulse-

width dispersion performance. The source impedance should

be minimized as much as is practicable. High source impedance,

in combination with the parasitic input capacitance of the

comparator, causes an undesirable degradation in bandwidth at

the input, thus degrading the overall response. Thermal noise

from large resistances can easily cause extra jitter with slowly

slewing input signals; higher impedances encourage undesired

coupling.

COMPARATOR PROPAGATION

DELAY DISPERSION

The ADCMP603 comparator is designed to reduce propagation

delay dispersion over a wide input overdrive range of 5 mV to

VCCI – 1 V. Propagation delay dispersion is the variation in

propagation delay that results from a change in the degree of

overdrive or slew rate (that is, how far or how fast the input

signal exceeds the switching threshold).

Propagation delay dispersion is a specification that becomes

important in high speed, time-critical applications, such as data

communication, automatic test and measurement, and instru-

mentation. It is also important in event-driven applications, such

as pulse spectroscopy, nuclear instrumentation, and medical

imaging. Dispersion is defined as the variation in propagation

delay as the input overdrive conditions are changed (Figure 15

and Figure 16).

ADCMP603 dispersion is typically < 2 ns as the overdrive varies

from 10 mV to 125 mV. This specification applies to both

positive and negative signals because the device has very closely

matched delays for both positive-going and negative-going

inputs.

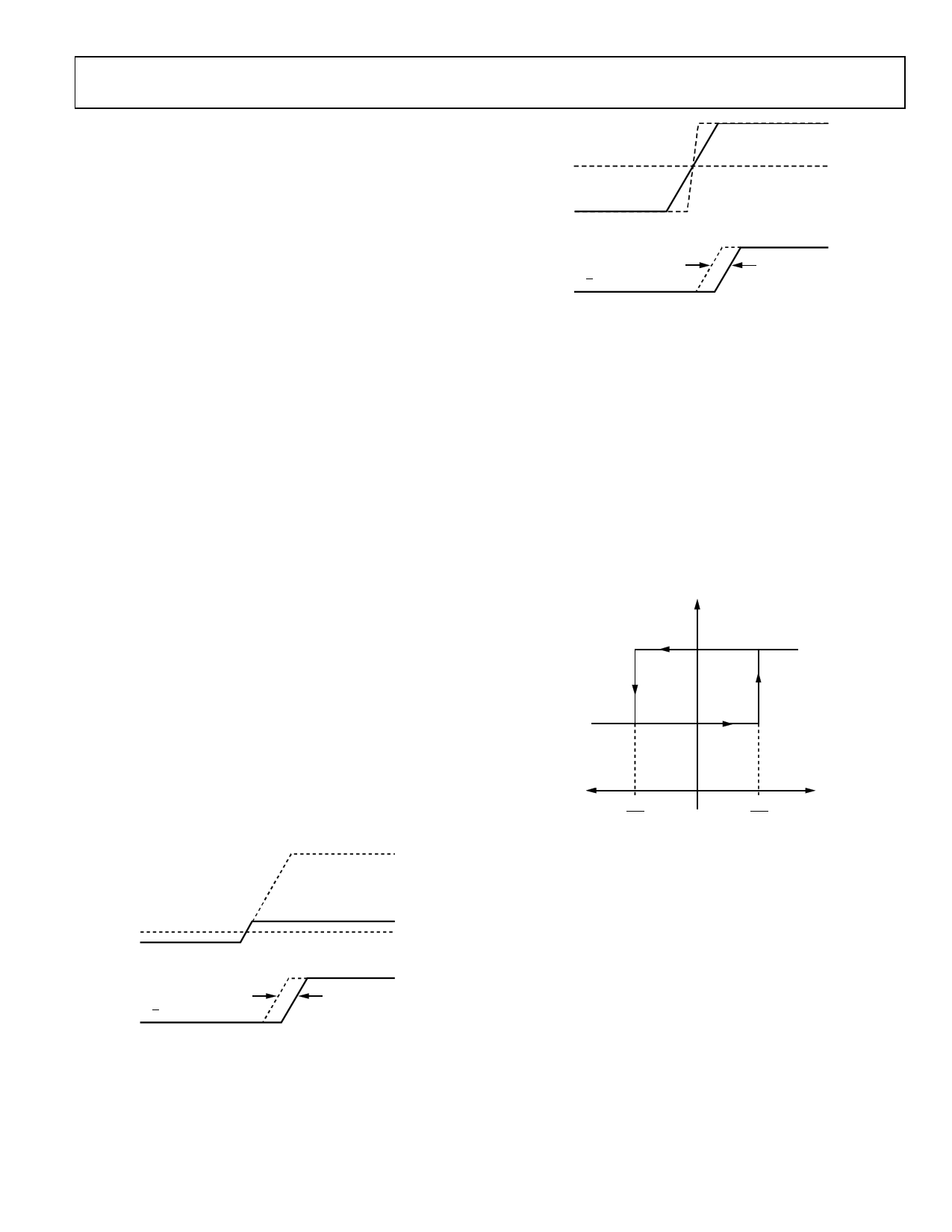

500mV OVERDRIVE

INPUT VOLTAGE

10mV OVERDRIVE

VN ± VOS

DISPERSION

Q/Q OUTPUT

Figure 15. Propagation Delay—Overdrive Dispersion

INPUT VOLTAGE

1V/ns

10V/ns

ADCMP603

VN ± VOS

DISPERSION

Q/Q OUTPUT

Figure 16. Propagation Delay—Slew Rate Dispersion

COMPARATOR HYSTERESIS

The addition of hysteresis to a comparator is often desirable in a

noisy environment, or when the differential input amplitudes

are relatively small or slow moving. Figure 17 shows the transfer

function for a comparator with hysteresis. As the input voltage

approaches the threshold (0.0 V, in this example) from below

the threshold region in a positive direction, the comparator

switches from low to high when the input crosses +VH/2, and the

new switching threshold becomes −VH/2. The comparator remains

in the high state until the new threshold, −VH/2, is crossed from

below the threshold region in a negative direction. In this manner,

noise or feedback output signals centered on 0.0 V input cannot

cause the comparator to switch states unless it exceeds the region

bounded by ±VH/2.

OUTPUT

VOH

VOL

–VH 0

2

INPUT

+VH

2

Figure 17. Comparator Hysteresis Transfer Function

The customary technique for introducing hysteresis into a

comparator uses positive feedback from the output back to the

input. One limitation of this approach is that the amount of

hysteresis varies with the output logic levels, resulting in

hysteresis that is not symmetric about the threshold. The

external feedback network can also introduce significant

parasitics that reduce high speed performance and induce

oscillation in some cases.

Rev. 0 | Page 11 of 16

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet ADCMP603.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADCMP600 | (ADCMP600 - ADCMP602) Single-Supply TTL/CMOS Comparator | Analog Devices |

| ADCMP601 | (ADCMP600 - ADCMP602) Single-Supply TTL/CMOS Comparator | Analog Devices |

| ADCMP602 | (ADCMP600 - ADCMP602) Single-Supply TTL/CMOS Comparator | Analog Devices |

| ADCMP603 | Single-Supply TTL/CMOS Comparator | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |