|

|

PDF HM64YLB36514 Data sheet ( Hoja de datos )

| Número de pieza | HM64YLB36514 | |

| Descripción | 16M Synchronous Late Write Fast Static RAM | |

| Fabricantes | Renesas Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HM64YLB36514 (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

HM64YLB36514 Series

16M Synchronous Late Write Fast Static RAM

(512-kword × 36-bit, Register-Latch Mode)

REJ03C0039-0001Z

Preliminary

Rev.0.10

May.15.2003

Description

The HM64YLB36514 is a synchronous fast static RAM organized as 512-kword × 36-bit. It has realized

high speed access time by employing the most advanced CMOS process and high speed circuit designing

technology. It is most appropriate for the application which requires high speed, high density memory and

wide bit width configuration, such as cache and buffer memory in system. It is packaged in standard 119-

bump BGA.

Note: All power supply and ground pins must be connected for proper operation of the device.

Features

• 2.5 V ± 5% operation and 1.5 V (VDDQ)

• 16M bit density

• Internal self-timed late write

• Byte write control (4 byte write selects, one for each 9-bit)

• Optional ×18 configuration

• HSTL compatible I/O

• Programmable impedance output drivers

• Differential pseudo-HSTL clock inputs

• Asynchronous G output control

• Asynchronous sleep mode

• FC-BGA 119pin package with SRAM JEDEC standard pinout

• Limited set of boundary scan JTAG IEEE 1149.1 compatible

• Protocol: Single differential clock register-latch mode

Preliminary: The specifications of this device are subject to change without notice. Please contact your

nearest Renesas Technology's Sales Dept. regarding specifications.

Rev.0.10, May.15.2003, page 1 of 22

1 page

HM64YLB36514 Series

Truth Table

ZZ SS G SWE SWEa SWEb SWEc SWEd K K Operation DQ (n)

H ×× ×

×

×

×

× × × Sleep

High-Z

mode

L H× ×

×

×

×

× L-H H-L Dead

High-Z

(not

selected)

L ×H H

×

×

×

× × × Dead

High-Z

(dummy

read)

L LL H

×

×

×

× L-H H-L Read

DOUT

(a, b,

c, d)

0 to 8

L L× L

L

L

L

L L-H H-L Write

High-Z

a, b, c, d

byte

L L× L

H

L

L

L L-H H-L Write

High-Z

b, c, d

byte

L L× L

L

H

L

L L-H H-L Write

High-Z

a, c, d

byte

L L× L

L

L

H

L L-H H-L Write

High-Z

a, b, d

byte

L L× L

L

L

L

H L-H H-L Write

High-Z

a, b, c

byte

L L× L

H

H

L

L L-H H-L Write

High-Z

c, d byte

L L× L

L

H

H

L L-H H-L Write

High-Z

a, d byte

L L× L

L

L

H

H L-H H-L Write

High-Z

a, b byte

L L× L

H

L

L

H L-H H-L Write

High-Z

b, c byte

L L× L

H

H

H

L L-H H-L Write

High-Z

d byte

L L× L

H

H

L

H L-H H-L Write

High-Z

c byte

L L× L

H

L

H

H L-H H-L Write

High-Z

b byte

L L × L L H H H L-H H-L Write High-Z

a byte

Notes:

1.

H:

V , L:

IH

V,

IL

×:

V or V

IH IL

2. SWE, SS, SWEa to SWEd, and SA are sampled at the rising edge of K clock.

DQ (n+1)

High-Z

×

High-Z

×

D

IN

(a, b, c, d)

0 to 8

DIN

(b, c, d)

0 to 8

DIN

(a, c, d)

0 to 8

D

IN

(a, b, d)

0 to 8

DIN

(a, b, c)

0 to 8

DIN (c, d)

0 to 8

D (a, d)

IN

0 to 8

DIN (a, b)

0 to 8

DIN (b, c)

0 to 8

DIN (d)

0 to 8

D (c)

IN

0 to 8

DIN (b)

0 to 8

DIN (a)

0 to 8

Rev.0.10, May.15.2003, page 5 of 22

5 Page

HM64YLB36514 Series

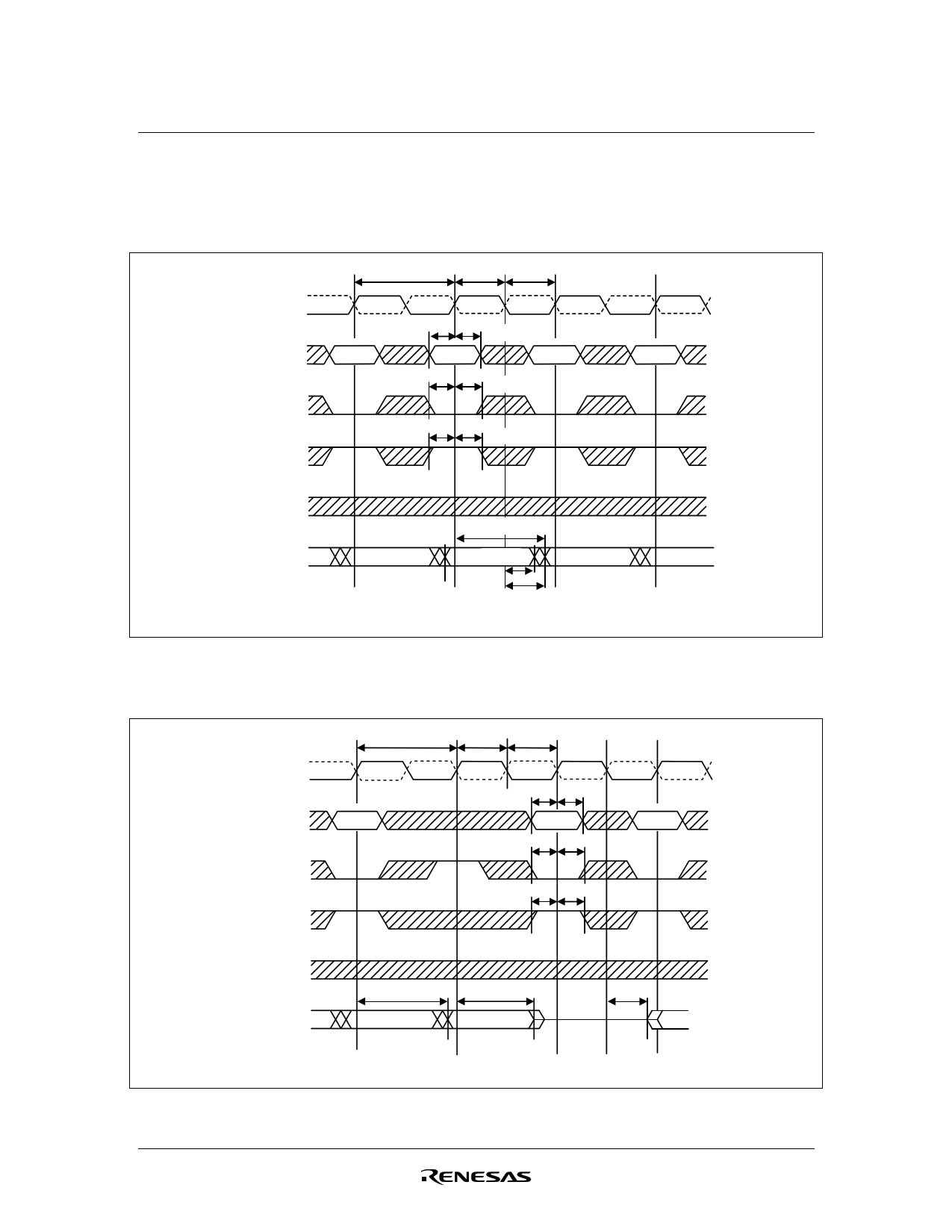

Timing Waveforms

Read Cycle-1

K, K

SA

SS

SWE

SWEx

DQ

Note: ZZ = VIL

tKHKH

tKHKL

tKLKH

tAVKH

tKHAX

A1 A2 A3

tAVKH

tKHAX

tAVKH

tKHAX

tKHQV

Q0 Q1 Q2

tKLQX

tKLQV

A4

Q3

Read Cycle-2 (SS Controlled)

K, K

tKHKH

SA

SS

SWE

SWEx

DQ

Note: ZZ = VIL

A1

tKHQV

Q0

tKHKL

tKLKH

tAVKH tKHAX

A3

tAVKH tKHAX

tAVKH tKHAX

A4

tKHQZ

Q1

tKLQX2

Q3

Rev.0.10, May.15.2003, page 11 of 22

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet HM64YLB36514.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HM64YLB36514 | 16M Synchronous Late Write Fast Static RAM | Renesas Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |