|

|

PDF HDMP-0422 Data sheet ( Hoja de datos )

| Número de pieza | HDMP-0422 | |

| Descripción | Single Port Bypass Circuit | |

| Fabricantes | Hewlett-Packard | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HDMP-0422 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Agilent HDMP-0422

Single Port Bypass Circuit with CDR &

Data Valid Detection Capability

for Fibre Channel Arbitrated Loops

Data Sheet

Description

The HDMP-0422 is a Single Port

Bypass Circuit (PBC) with Clock

and Data Recovery (CDR)

capability included. This integrated

circuit provides a low-cost, low-

power physical-layer solution for

Fibre Channel Arbitrated Loop

(FC-AL) disk array configurations.

By using a PBC such as the HDMP-

0422, hard disks may be pulled out

or swapped while other disks in the

array are available to the system.

A PBC consists of multiple 2:1

multiplexers daisy chained along

with a CDR. Each port has two

modes of operation: “disk in loop”

and “disk bypassed.” When the

“disk in loop” mode is selected, the

loop goes into and out of the disk

drive at that port. For example,

data goes from the HDMP-0422’s

TO_NODE[n]± differential output

pins to the Disk Drive Transceiver

IC’s (e.g. an HDMP-1636A) Rx

differential input pins. Data from

the Disk Drive Transceiver IC’s Tx

differential outputs goes to the

HDMP-0422’s FM_NODE[n]±

differential input pins. Figures 2

and 3 show connection diagrams

for disk drive array applications.

When the “disk bypassed” mode is

selected, the disk drive is either

absent or non-functional and the

loop bypasses the hard disk.

The “disk bypassed” mode is

enabled by pulling the BYPASS[n]-

pin low. Leave BYPASS[n]-

floating to enable the “disk in

loop” mode. HDMP-0422s may be

cascaded with other members of

the HDMP-04XX/HDMP-05XX

family through the appropriate

FM_NODE[n]± and

TO_NODE[n]± pins to

accommodate any number of hard

disks (see Figure 4). The unused

cells in the HDMP-0422 may be

bypassed by using pulldown

resistors on the BYPASS[n]- pins

for these cells.

Features

• Supports 1.0625 GBd Fibre

Channel operation

• Supports 1.25 GBd Gigabit

Ethernet (GE) operation

• Single PBC/CDR in one package

• CDR location determined by

choice of cable input/output

• Amplitude valid and data valid

detection (Fibre channel rate only)

on FM_NODE[0] input

• Equalizers on all inputs

• High-speed LVPECL I/O

• Buffered Line Logic (BLL) outputs

(no external bias resistors

required)

• 0.46 W typical power at

VCC = 3.3 V

• 24 Pin, low-cost SSOP package

Applications

• RAID, JBOD, BTS cabinets

• One 2:1 muxes

• One 1:2 buffers

• 1 ≥ N Gigabit serial buffer

• N ≥ 1 Gigabit serial mux

An HDMP-0422 may also be used

as two 1:1 buffers, one with a CDR

and one without. For example, an

HDMP-0422 may be placed in

front of a CMOS ASIC to clean the

jitter of the outgoing signal (CDR

path) and to better read the

incoming signal (non-CDR paths).

In addition, the HDMP-0422 may

be configured as one 2:1

multiplexers or as one 1:2 buffers.

HDMP-0422

CAUTION: As with all semiconductor ICs, it is advised that normal static precautionsb be taken in

the handling and assembly of this component to prevent damage and/or degradation which may be

induced by electrostatic discharge (ESD).

1 page

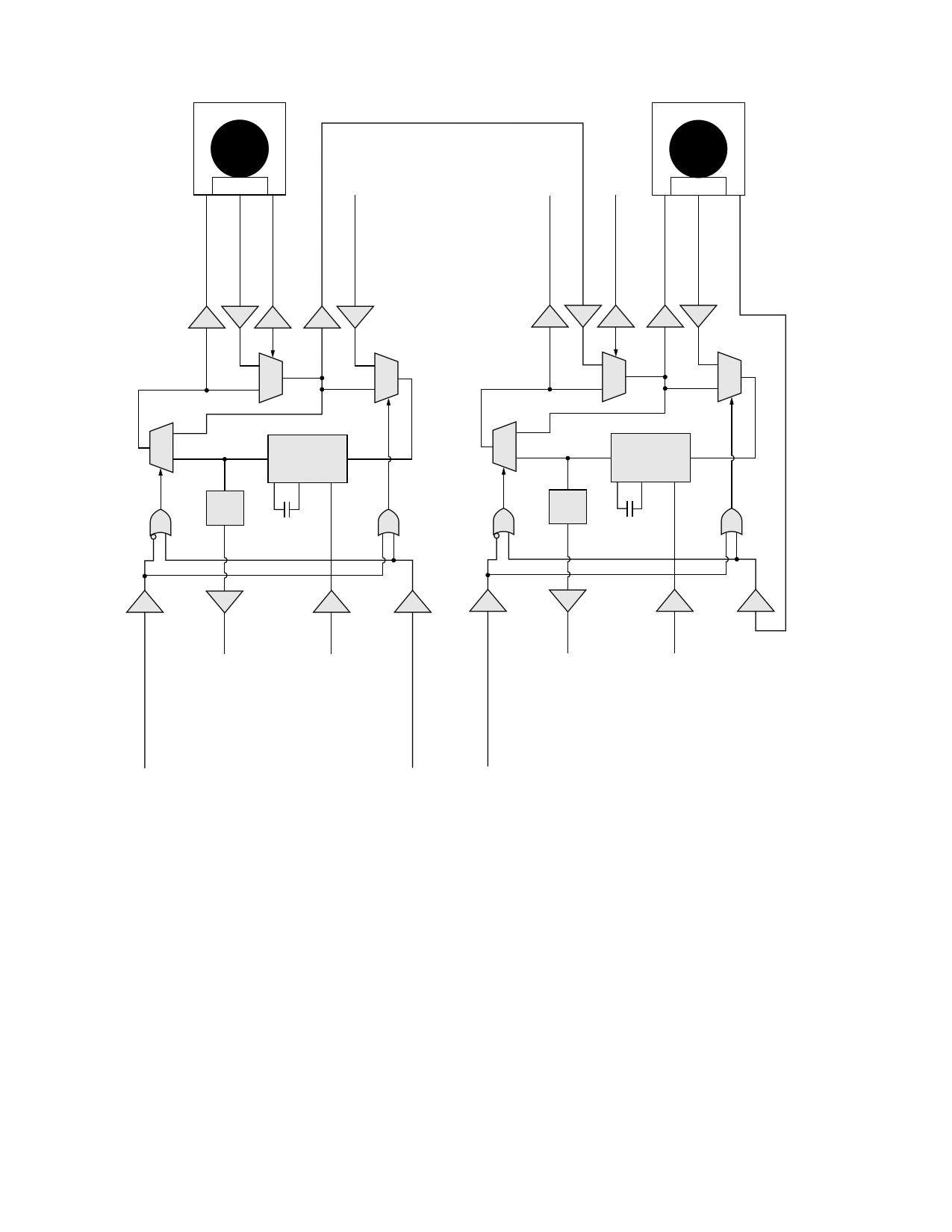

HARD DISK A

SERDES

HARD DISK A

SERDES

EQU

BLL TTL

EQU

BLL

11

00

0

1 CDR

DV

CPLL

EQU

BLL TTL

EQU

BLL

11

00

0

1 CDR

DV

CPLL

TTL

TTL

TTL

TTL TTL TTL

TTL TTL

Figure 4. Connection diagram for multiple HDMP-0422s.

5

5 Page

Simplified I/O Cells

O_LVTTL

VCC

I_LVTTL

VCC

VCC

GND

ESD

PROTECTION

GND

ESD

PROTECTION

Figure 9. O-LVTTL and I-LVTTL simplified circuit schematic.

GND

VBB

1.4 V

75 Ω

HS_OUT

VCCHS

VCC

VCC

VCC

TO_NODE[n]+

Z0 = 75 Ω 0.01 µF FM_NODE[n]+

HS_IN

+

–+

–

ESD

PROTECTION

TO_NODE[n]–

GND

GND

2*Z0 = 150 Ω

Z0 = 75 Ω 0.01 µF

FM_NODE[n]–

GND

GND

ESD

PROTECTION

NOTE:

1. FM_NODE[n] INPUTS SHOULD NEVER BE CONNECTED TO GROUND AS PERMANENT DAMAGE TO THE DEVICE MAY RESULT.

Figure 10. HS_OUT and HS_IN simplified circuit schematic.

11

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet HDMP-0422.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HDMP-0421 | Port Bypass Circuits | Hewlett-Packard |

| HDMP-0422 | Single Port Bypass Circuit | Hewlett-Packard |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |