|

|

PDF INDR331B Data sheet ( Hoja de datos )

| Número de pieza | INDR331B | |

| Descripción | (INDx166B / INDx331B) Long Distance Digital Display Link Transmitter & Receiver | |

| Fabricantes | Inova | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de INDR331B (archivo pdf) en la parte inferior de esta página. Total 40 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Preliminary Data Sheet

INDT/R166B

INDT/R331B

Order this document by Q_DS_IND166-331

Long Distance Digital Display

Link Transmitter & Receiver

The GigaSTaR Digital Display Link 166/331-series is an

innovative high-speed link featuring simultaneous

transmission of digital video, audio and bi-directional

sideband data over one standard shielded twisted pair

cable up to 50 m (500 m with fiber optics). It supports

VGA…UXGA as well as Digital TV (DTV) and High-

Definition TV (HDTV) formats up to 720p or HDTV1080i

with up to 16.7 million colors. The sideband channels

provide bandwidth up to 264 Mbps to connect peripheral

components like keyboard, mouse, disc drive and audio

devices.

Compared to the 165/330-series the 166/331 offer

additional features like a tristate pixel interface (Rx only)

and an integrated pixel buffer to reducing pixel clock

variations. The 166/331 may be used as direct drop-in

replacement for the 165/330 under specified conditions.

INDT/R166B

INDT/R331B

INDT/R166B

INDT/R331B

VESA Format

at 18bit/60Hz

VGA…WXGA

VESA Format

at 24bit/60Hz

VGA…XGA

VGA…UXGA

VGA…SXGA

HDTV (24 bit)

480p (60fps), 720p (30fps)

480p (60fps), 720p (60fps), 1080i (30fps)

Features:

• Parallel graphics controller and LC-display interfaces:

− 18- / 24-bit (1 pixel/clock)

− 36- / 48-bit (2 pixel/clock)

• Pixel data clocking on rising/falling/both clock edges

• Pixel Clock frequency: 24 – 161 MHz

• Direct adaptation to DVI and LDI/LVDS standard interface

devices

• 4 channel audio interface (IEC958 compliant S/P-DIF)

• High- and low-speed bi-directional sideband data channels

• Single + 3.3 V power supply

• Extended temperature range: -40 – +85 °C

Applications:

• Long distance multimedia consoles

• High resolution industrial remote terminals

• Video broadcast systems

• Long distance camera links

• Machine vision systems

• Digital TV equipment

• Video Projectors and Home Cinemas

• DVI Extension products

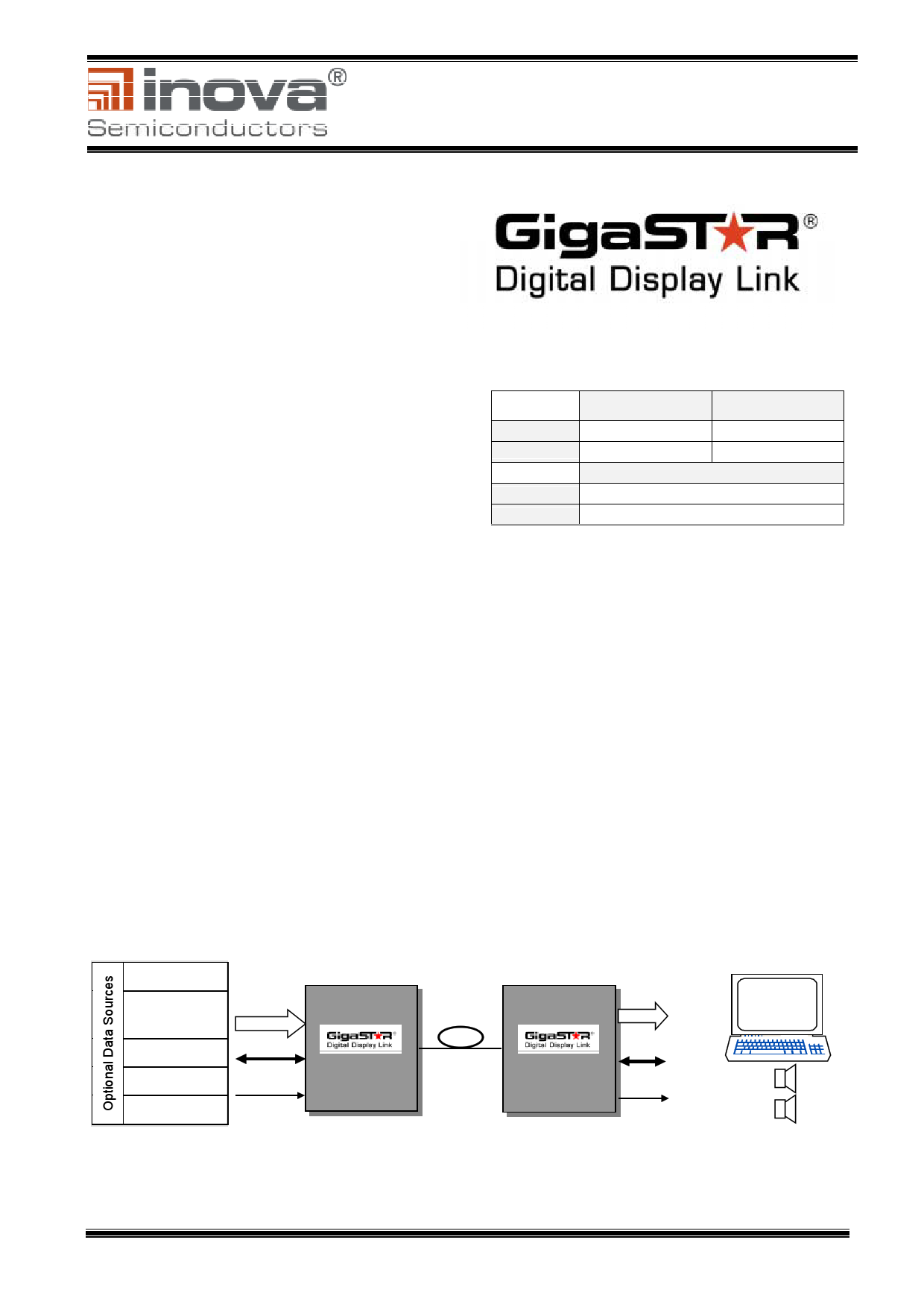

Typical Application:

PC

Graphics

C o n tro lle r

Camera

DVD

HDTV

VIDEO Transmitter

Receiver

DATA

AUDIO

INDT166B

or

INDT331B

STP-cable

INDR166B

or

INDR331B

VIDEO

TFT

LC-Display

DATA

AUDIO

Date: 2005-03-14 Revision: 0.1

Page 1 of 40

1 page

Preliminary Data Sheet

INDT/R166B

INDT/R331B

The transmitter’s pixel interface accepts pixel data with a pixel clock frequency of 24 – 161 MHz (full pixel mode). For the

Tx side in single-ended mode, PX_CLK+ is the clock input and PX_CLK– has to be tied to GND. A differential pixel clcok

mode on the Rx side is not available. All pixel data and pixel clock inputs of the transmitter can be selected through the

VREF-pin to either work with conventional graphic controllers with 3.3 V output voltage swing or to work with latest

controllers with low voltage swing (1.0 – 2.0 V, see Figure 3.3: VREF Reference Circuitry). The pixel data and pixel

clock outputs of the receiver provide a 3.3 V CMOS compliant output.

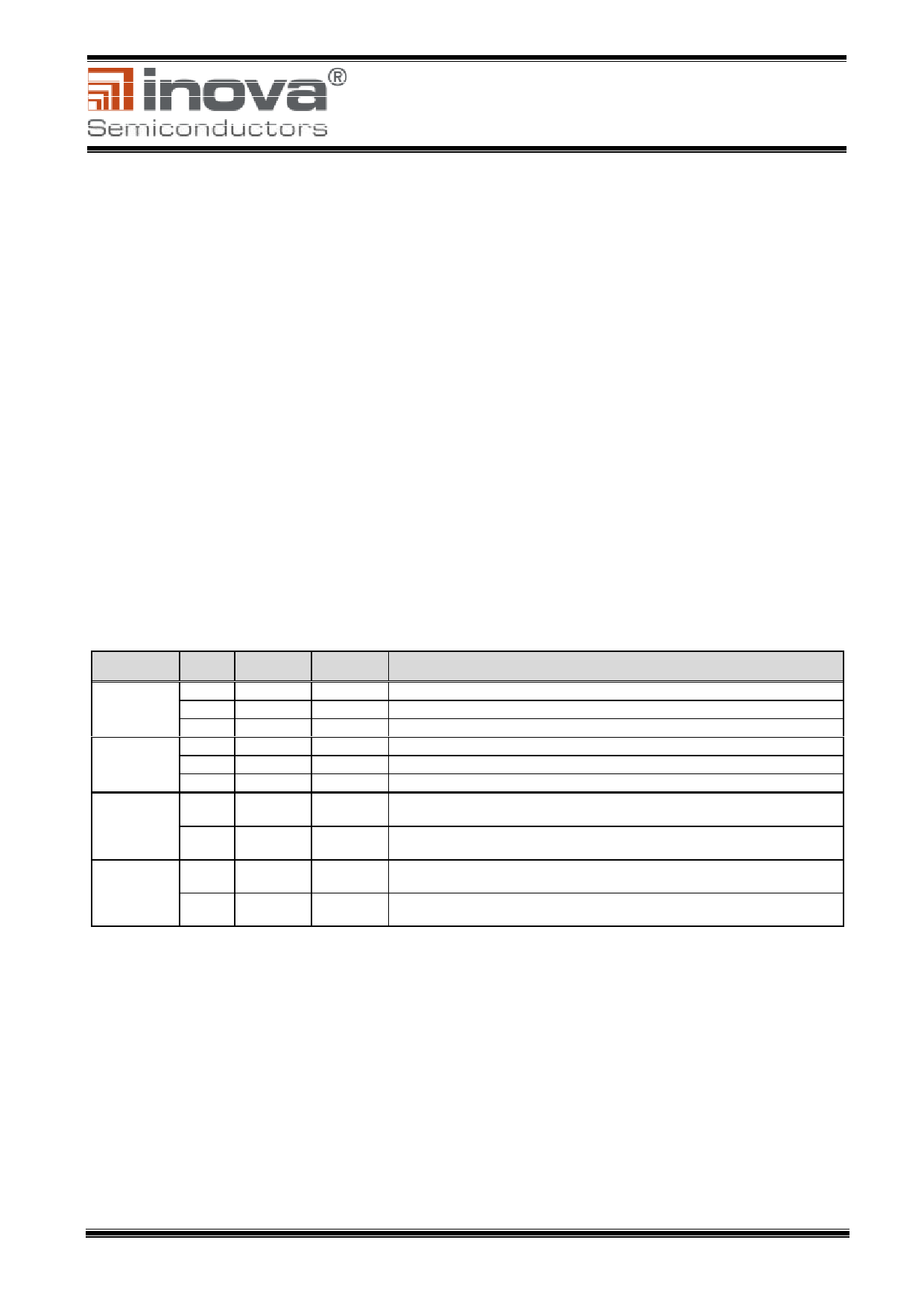

1.2.2 Pixel Interface Modes

The pixel interface is configurable to accommodate all the various graphic interface standards in the market. The width of

the pixel interface is a function of the selected operating mode.

• In full-pixel mode the bit width of the pixel interface can be set to support an 18- or 24-bit wide parallel video interface.

1 pixel per sampling edge is transmitted.

• In double-pixel mode the bit width of the pixel interface can be set to support a 36- or 48-bit wide parallel video

interface. 2 pixels per sampling edge are transmitted.

1.2.3 Pixel Clock Sampling Modes

The pixel interface can be set to support data sampling at the rising, falling or at both edges of the pixel clock,

depending on the selected mode.

Table 1.4 and , Figure 1.4, Figure 1.5 summarize the various options for configuring the pixel interface.

Pixel Mode

18-bit

(Full Pixel)

24-bit

(Full Pixel)

36-bit

(Double

Pixel)

48-bit

(Double

Pixel)

Clock

Edge

rising

falling

both

rising

falling

both

rising

PX_CLK+

↑

↓

↑↓

↑

↓

↑↓

↑

falling

↓

rising

↑

falling

↓

PX_CLK-

–

–

–

–

–

–

–

–

–

–

Description

18 bits of pixel(n) sampled at rising edge of PX_CLK+

18 bits of pixel(n) sampled at falling edge of PX_CLK+

18 bits of pixel(n) sampled at both edges of PX_CLK+

24 bits of pixel(n) sampled at rising edge of PX_CLK+

24 bits of pixel(n) sampled at falling edge of PX_CLK+

24 bits of pixel(n) sampled at both edges of PX_CLK+

18 bits of pixel(n) and

18 bits of pixel(n+1) sampled at rising edge of PX_CLK+

18 bits of pixel(n) and

18 bits of pixel(n+1) sampled at falling edge of PX_CLK+

24 bits of pixel(n) and

24 bits of pixel(n+1) sampled at rising edge of PX_CLK+

24 bits of pixel(n) and

24 bits of pixel(n+1) sampled at falling edge of PX_CLK+

Table 1.4: Overview – Pixel Interface Configurations

Date: 2005-03-14 Revision: 0.1

Page 5 of 40

5 Page

Preliminary Data Sheet

INDT/R166B

INDT/R331B

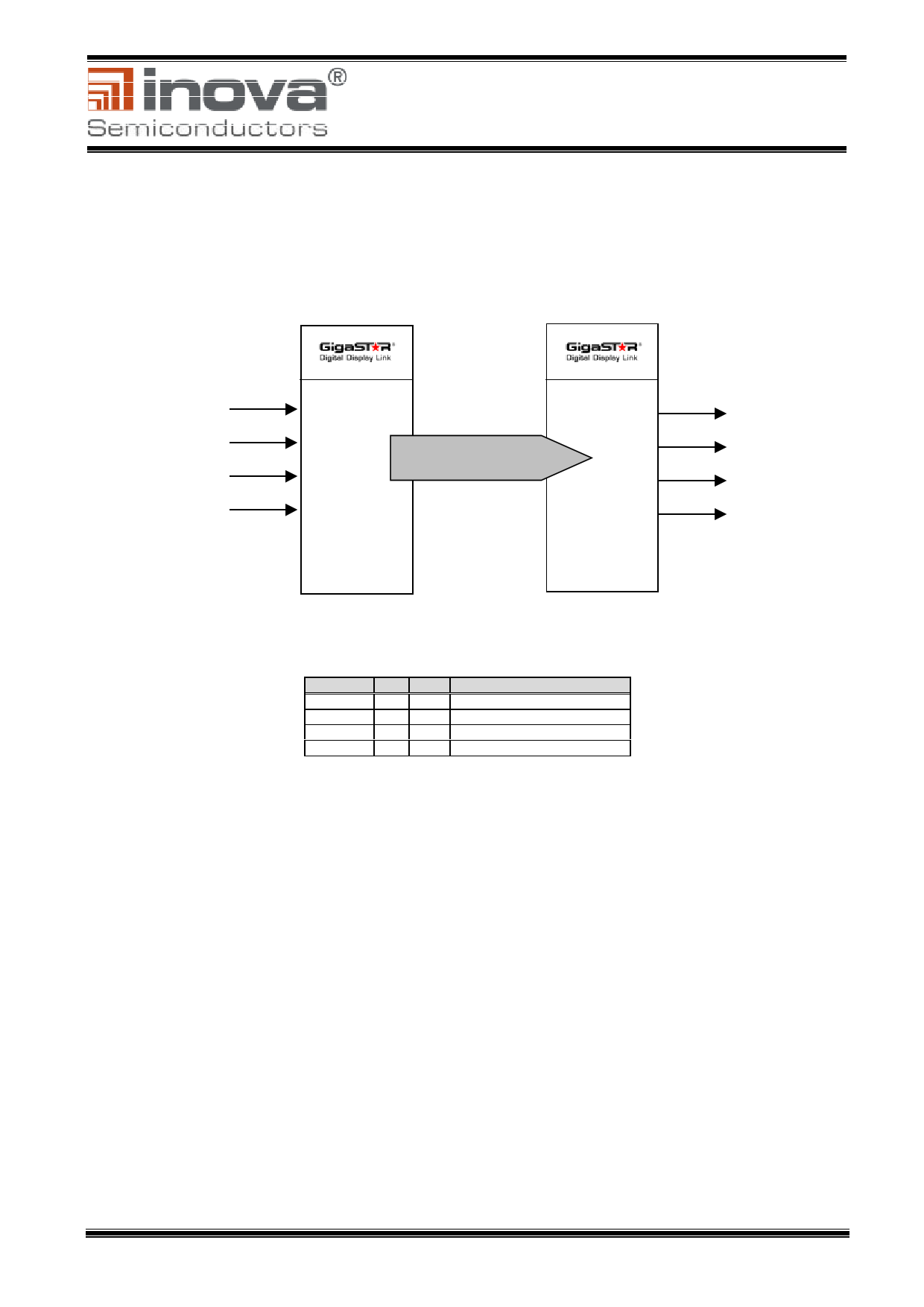

1.4 Audio Interface

The audio interface provides four serial audio channels, which are compliant to the Standard IEC958 Digital audio interface

from the EBU (European Broadcasting Union), also known as S/P-DIF Interface. It supports sampling frequencies of 44,1

kHz and 48,0 kHz. The audio data interface can be disabled to free up bandwidth for pixel data transmission.

AI_C0

AI_C1

AI_C2

AI_C3

Audio

S/P DIF

Downstream

Audio

S/P DIF

INDT

Transmitter

INDR

Reveiver

Figure 1.7: Audio Interface

Signal

AI_C0

AI_C1

AI_C2

AI_C3

Tx Rx Description

IN OUT S/P-DIF Audio Channel 0

IN OUT S/P-DIF Audio Channel 1

IN OUT S/P-DIF Audio Channel 2

IN OUT S/P-DIF Audio Channel 3

Table 1.9: Audio Interface Signals

AI_C0

AI_C1

AI_C2

AI_C3

Date: 2005-03-14 Revision: 0.1

Page 11 of 40

11 Page | ||

| Páginas | Total 40 Páginas | |

| PDF Descargar | [ Datasheet INDR331B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| INDR331B | (INDx166B | INDx331B) Long Distance Digital Display Link Transmitter & Receiver |

| INDR331B | (INDx166B / INDx331B) Long Distance Digital Display Link Transmitter & Receiver | Inova |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |