|

|

PDF HY29DS163 Data sheet ( Hoja de datos )

| Número de pieza | HY29DS163 | |

| Descripción | (HY29DS162 / HY29DS163) Simultaneous Read/Write Flash Memory | |

| Fabricantes | Hynix Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HY29DS163 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

HY29DS162/HY29DS163

16 Megabit (2M x 8/1M x 16) Super-Low Voltage,

Dual Bank, Simultaneous Read/Write, Flash Memory

KEY FEATURES

n Single Power Supply Operation

− Read, program, and erase operations

from 1.8 to 2.2 V (2.0V ± 10%)

− Ideal for battery-powered applications

n Simultaneous Read/Write Operations

− Host system can program or erase in one

bank while simultaneously reading from any

sector in the other bank with zero latency

between read and write operations

n High Performance

− 120 and 130 ns access time versions with

± 10% power supply and 30pF load

n Ultra Low Power Consumption (Typical

Values)

− Automatic sleep mode current: 200 nA

− Standby mode current: 200 nA

− Read current: 5 mA (at 5 MHz)

− Program/erase current: 15 mA

n Boot-Block Sector Architecture with 39

Sectors in Two Banks for Fast In-System

Code Changes

n Secured Sector: An Extra 64 Kbyte Sector

that Can Be:

− Factory locked and identifiable: 16 bytes

available for a secure, random factory-

programmed Electronic Serial Number

− Customer lockable: Can be read, program-

med, or erased just like other sectors

n Flexible Sector Architecture

− Sector Protection allows locking of a

sector or sectors to prevent program or

erase operations within that sector

− Temporary Sector Unprotect allows

changes in locked sectors (requires high

voltage on RESET# pin)

n Automatic Erase Algorithm Erases Any

Combination of Sectors or the Entire Chip

n Automatic Program Algorithm Writes and

Verifies Data at Specified Addresses

n Compliant with Common Flash Memory

Interface (CFI) Specification

n Minimum 100,000 Write Cycles per Sector

(1,000,000 cycles Typical)

n Compatible with JEDEC Standards

− Pinout and software compatible with

single-power supply Flash devices

− Superior inadvertent write protection

n Data# Polling and Toggle Bits

− Provide software confirmation of completion

of program or erase operations

n Ready/Busy# Pin

− Provides hardware confirmation of

completion of program or erase operations

n Erase Suspend

− Suspends an erase operation to allow

programming data to or reading data from

a sector in the same bank

− Erase Resume can then be invoked to

complete the suspended erasure

n Hardware Reset Pin (RESET#) Resets the

Device to Reading Array Data

n WP#/ACC Input Pin

− Write protect (WP#) function allows

hardware protection of two outermost boot

sectors, regardless of sector protect status

− Acceleration (ACC) function provides

accelerated program times

n Fast Program and Erase Times

− Sector erase time: 1 sec typical

− Byte/Word program time utilizing

Acceleration function: 13 µs typical

n Space Efficient Packaging

− 48-pin TSOP and 48-ball FBGA packages

LOGIC DIAGRAM

20

A[19:0]

DQ[7:0]

CE#

OE#

WE#

RESET#

BYTE#

DQ[14:8]

DQ[15]/A[-1]

WP#/ACC

RY/BY#

8

7

Preliminary

Revision 1.3, April 2001

1 page

HY29DS162/HY29DS163

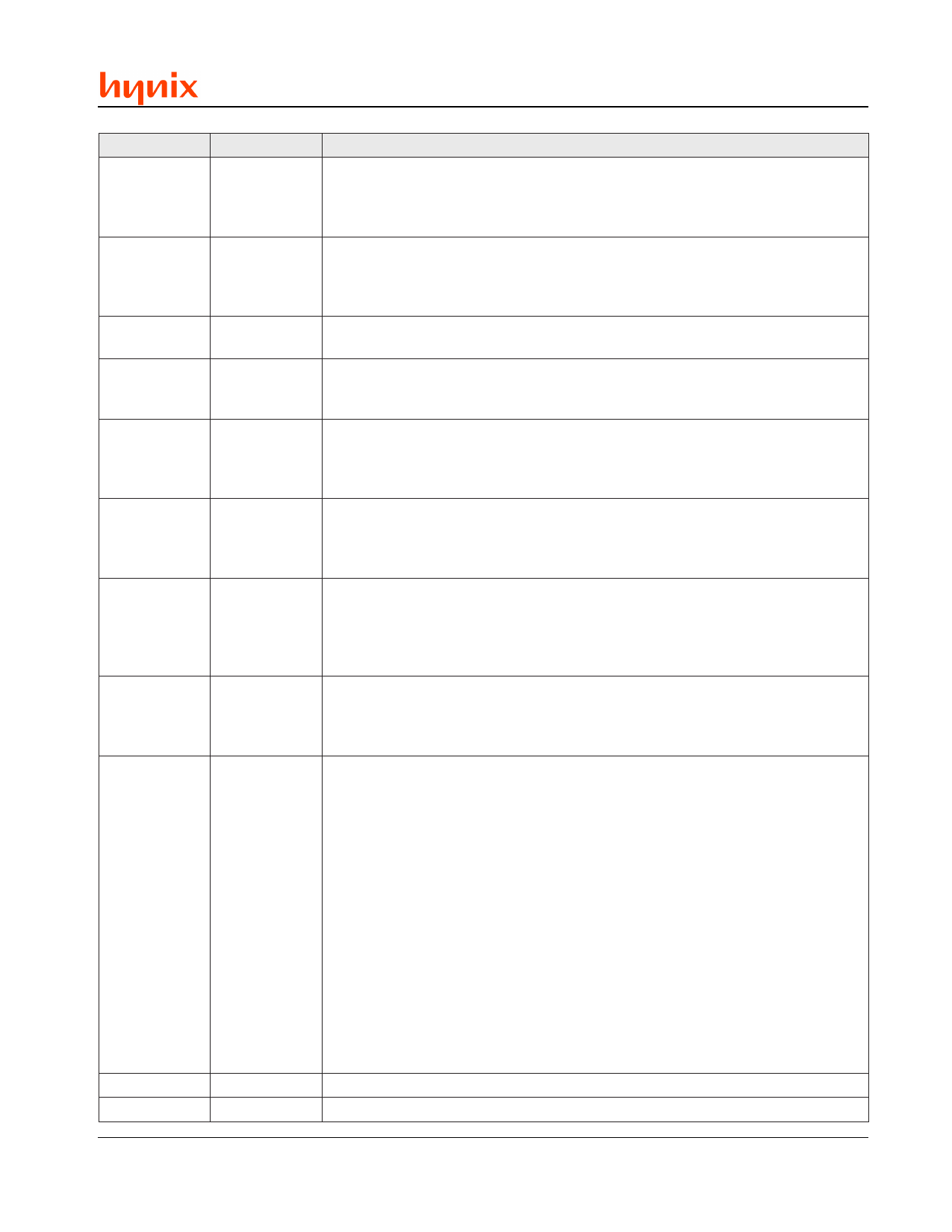

SIGNAL DESCRIPTIONS

Name

Type

Description

A[19:0]

Inputs

Address, active High. In word mode, these 20 inputs select one of 1,048,576

(1M) words within the array for read or write operations. In byte mode, these

inputs are combined with the DQ[15]/A[-1] input (LSB) to select one of 2,097,152

(2M) bytes within the array for read or write operations.

DQ[15]/A[-1],

DQ[14:0]

Data Bus, active High. In word mode, these pins provide a 16-bit data path

Inputs/Outputs for read and write operations. In byte mode, DQ[7:0] provide an 8-bit data path

Tri-state and DQ[15]/A[-1] is used as the LSB of the 21-bit byte address input. DQ[14:8]

are unused and remain tri-stated in byte mode.

BYTE#

Input

Byte Mode, active Low. Controls the Byte/Word configuration of the device.

Low selects Byte mode, High selects Word mode.

Chip Enable, active Low. This input must be asserted to read data from or

CE#

Input

write data to the HY29DS16x. When High, the data bus is tri-stated and the

device is placed in the Standby mode.

OE#

Input

Output Enable, active Low. This input must be asserted for read operations

and negated for write operations. BYTE# determines whether a byte or a word

is read during the read operation. When High, data outputs from the device are

disabled and the data bus pins are placed in the high impedance state.

WE#

Input

Write Enable, active Low. Controls writing of command sequences in order to

program data or erase sectors of the memory array. A write operation takes

place when WE# is asserted while CE# is Low and OE# is High. BYTE#

determines whether a byte or a word is written during the write operation.

RESET#

Input

Hardware Reset, active Low. Provides a hardware method of resetting the

HY29DS16x to the read array state. When the device is reset, it immediately

terminates any operation in progress. The data bus is tri-stated and all read/write

commands are ignored while the input is asserted. While RESET# is asserted,

the device will be in the Standby mode.

RY/BY#

Output

Open Drain

Ready/Busy Status. Indicates whether a write or erase command is in

progress or has been completed. Valid after the rising edge of the final WE#

pulse of a command sequence. It remains Low while the device is actively

programming data or erasing, and goes High when it is ready to read array data.

Write Protect, active Low/Accelerate (VHH).

Write Protect Function: Placing this pin at VIL disables program and erase

operations in two of the eight 8 Kbyte/4 Kword boot sectors. The affected

sectors are S0 and S1 in a bottom-boot device, or S37 and S38 in a top-boot

device. If the pin is placed at VIH, the protection state of those two sectors

reverts to whether they were last set to be protected or unprotected using the

method described in the Sector Group Protection and Unprotection sections.

WP#/ACC

Input

Accelerate Function: If VHH is applied to this input, the device enters the Unlock

Bypass mode, temporarily unprotects any protected sectors, and uses the

higher voltage on the pin to reduce the time required for program operations.

The system would then use the two-cycle program command sequence as

required by the Unlock Bypass mode. Removing VHH from the pin returns the

device to normal operation.

This pin must not be at VHH for operations other than accelerated programming,

or device damage may result. Leaving the pin unconnected may result in

inconsistent device operation.

VCC -- 2-volt (nominal) power supply.

VSS -- Power and signal ground.

r1.3/Apr 01

5

5 Page

The HY29DS16x is automatically set for reading

array data after device power-up and after a hard-

ware reset to ensure that no spurious alteration of

the memory content occurs during the power tran-

sition. No command is necessary in this mode to

obtain array data, and both banks of the device

remain enabled for read accesses until the com-

mand register contents are altered.

This device features the capability of reading data

from one bank of the memory while a program or

erase operation is in progress in the other bank.

If the host reads from an address within an eras-

ing or erase-suspended sector, or from a bank

where a programming operation is taking place,

the device outputs status data instead of array data

(see Write Operation Status section). After com-

pleting an Automatic Program or Automatic Erase

algorithm within a bank, that bank automatically

returns to the read array data mode.

When the host issues an Erase Suspend com-

mand, the bank specified in the command enters

the Erase- Suspended Read mode. While in that

mode, the host can read data from, or program

data into, any sector in that bank except the

sector(s) being erased. After completing a pro-

gramming operation in the Erase Suspend mode,

the system may once again read array data with

the same exception noted above.

The host must issue a hardware reset or the soft-

ware reset command to return a sector to the read

array data mode if DQ[5] goes high during a pro-

gram or erase cycle, or to return the device to the

read array data mode while it is in the Electronic

ID mode.

Write Operation

Certain operations, including programming data

and erasing sectors of memory, require the host

to write a command or command sequence to the

HY29DS16x. Writes to the device are performed

by placing the byte or word address on the device’s

address inputs while the data to be written is input

on DQ[15:0] (BYTE# = High) or DQ[7:0] (BYTE#

= Low). The host system must drive the CE# and

WE# pins Low and drive OE# High for a valid write

operation to take place. All addresses are latched

on the falling edge of WE# or CE#, whichever

happens later. All data is latched on the rising

edge of WE# or CE#, whichever happens first.

HY29DS162/HY29DS163

The “Device Commands” section of this data sheet

provides details on the specific device commands

implemented in the HY29DS16x.

Accelerated Program Operation

This device offers improved performance for pro-

gramming operations through the ‘Accelerate

(ACC)’ function. This is one of two functions pro-

vided by the WP#/ACC pin and is intended prima-

rily to allow faster manufacturing throughput at the

factory.

If VHH is applied to this input, the device enters the

Unlock Bypass mode, temporarily unprotects any

protected sectors, and uses the higher voltage on

the pin to reduce the time required for program

operations. The host system would then use the

two-cycle program command sequence as re-

quired by the Unlock Bypass mode. Removing

VHH from the pin returns the device to normal op-

eration.

This pin must not be at VHH for operations other

than accelerated programming, or device damage

may result. Leaving the pin floating or uncon-

nected may result in inconsistent device opera-

tion.

Write Protect Function

The Write Protect function provides a hardware

method of protecting certain boot sectors without

using VID. This is the second function provided by

the WP#/ACC pin.

Placing this pin at VIL disables program and erase

operations in two of the eight 8 Kbyte (4 Kword)

boot sectors. The affected sectors are sectors S0

and S1 in a bottom-boot device, or S37 and S38

in a top-boot device. If the pin is placed at VIH, the

protection state of those two sectors reverts to

whether they were last set to be protected or un-

protected using the method described in the Sec-

tor Group Protection and Unprotection sections.

Standby Operation

When the system is not reading or writing to the

device, it can place the device in the Standby

mode. In this mode, current consumption is greatly

reduced, and the data bus outputs are placed in

the high impedance state, independent of the OE#

input. The Standby mode can invoked using two

methods.

r1.3/Apr 01

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HY29DS163.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HY29DS162 | (HY29DS162 / HY29DS163) Simultaneous Read/Write Flash Memory | Hynix Semiconductor |

| HY29DS163 | (HY29DS162 / HY29DS163) Simultaneous Read/Write Flash Memory | Hynix Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |