|

|

PDF FM3264 Data sheet ( Hoja de datos )

| Número de pieza | FM3264 | |

| Descripción | (FM3204 - FM32256) Integrated Processor Companion | |

| Fabricantes | Ramtron | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de FM3264 (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Pre-Production

FM3204/16/64/256

Integrated Processor Companion with Memory

Features

High Integration Device Replaces Multiple Parts

• Serial Nonvolatile Memory

• Low Voltage Reset

• Watchdog Timer

• Early Power-Fail Warning/NMI

• Two 16-bit Event Counters

• Serial Number with Write-lock for Security

Processor Companion

• Active-low Reset Output for VDD and Watchdog

• Programmable VDD Reset Trip Point

• Manual Reset Filtered and Debounced

• Programmable Watchdog Timer

• Dual Battery-backed Event Counter Tracks

System Intrusions or other Events

• Comparator for Early Power-Fail Interrupt

• 64-bit Programmable Serial Number with Lock

Description

The FM32xx is a family of integrated devices that

includes the most commonly needed functions for

processor-based systems. Major features include

nonvolatile memory available in various sizes, low-

VDD reset, watchdog timer, nonvolatile event counter,

lockable 64-bit serial number area, and general

purpose comparator that can be used for an early

power-fail (NMI) interrupt or other purpose. The

family operates from 2.7 to 5.5V.

The FM32xx family is software and pinout

compatible with the FM31xx family which also

includes a real-time clock. The common features

allow a system design that easily can be assembled

with or without timekeeping by simply selecting the

FM31xx or FM32xx, respectively.

Each FM32xx provides nonvolatile RAM available in

sizes including 4Kb, 16Kb, 64Kb, and 256Kb

versions. Fast write speed and unlimited endurance

allow the memory to serve as extra RAM or

conventional nonvolatile storage. This memory is

truly nonvolatile rather than battery backed.

The processor companion includes commonly needed

CPU support functions. Supervisory functions

include a reset output signal controlled by either a

low VDD condition or a watchdog timeout. /RST goes

This is a product in pre-production phase of development. Device

characterization is complete and Ramtron does not expect to change

the specifications. Ramtron will issue a Product Change Notice if

any specification changes are made.

Rev 2.1

Dec. 2004

Ferroelectric Nonvolatile RAM

• 4Kb, 16Kb, 64Kb, and 256Kb versions

• Unlimited Read/Write Endurance

• 10 year Data Retention

• NoDelay™ Writes

Fast Two-wire Serial Interface

• Up to 1 MHz Maximum Bus Frequency

• Supports Legacy Timing for 100 kHz & 400 kHz

• Device Select Pins for up to 4 Memory Devices

• Companion Controlled via 2-wire Interface

Easy to Use Configurations

• Operates from 2.7 to 5.5V

• Small Footprint 14-pin SOIC (-S)

o “Green” 14-pin SOIC (-G)

• Pin Compatible with FM31xx Series

• Low Operating Current

• -40°C to +85°C Operation

active when VDD drops below a programmable

threshold and remains active for 100 ms after VDD

rises above the trip point. A programmable watchdog

timer runs from 100 ms to 3 seconds. The watchdog

timer is optional, but if enabled it will assert the reset

signal for 100 ms if not restarted by the host before

the timeout. A flag-bit indicates the source of the

reset.

A general-purpose comparator compares an external

input pin to the onboard 1.2V reference. This is

useful for generating an early warning power-fail

interrupt (NMI) but can be used for any purpose. The

family also includes a programmable 64-bit serial

number that can be locked making it unalterable.

Additionally the FM32xx offers a dual event counter

that tracks the number of rising or falling edges

detected on dedicated input pins. The counter can

optionally be battery backed and even battery

operated by attaching a backup power source to the

VBAK pin. If VBAK is connected to a battery or

capacitor, then events will be counted even in the

absence of VDD.

Ramtron International Corporation

1850 Ramtron Drive, Colorado Springs, CO 80921

(800) 545-FRAM, (719) 481-7000

www.ramtron.com

Page 1 of 20

1 page

VDD

VTP

tRPU

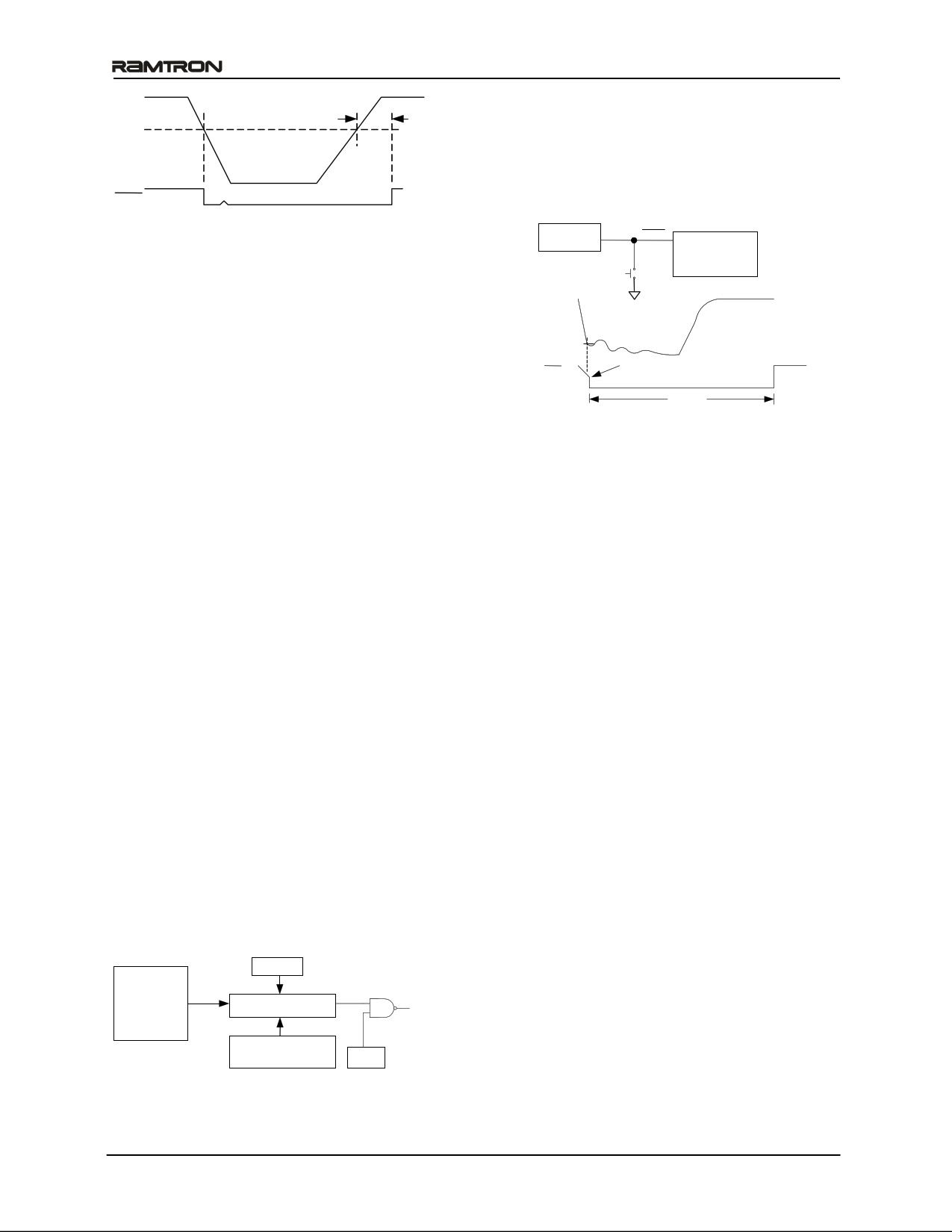

RST

Figure 2. Low Voltage Reset

The watchdog timer can also be used to assert the

reset signal (/RST). The watchdog is a free running

programmable timer. The period can be software

programmed from 100 ms to 3 seconds in 100 ms

increments via a 5-bit nonvolatile register. All

programmed settings are minimum values and vary

with temperature according to the operating

specifications. The watchdog has two additional

controls associated with its operation, a watchdog

enable bit (WDE) and timer restart bits (WR). Both

the enable bit must be set and the watchdog must

timeout in order to drive /RST active. If a reset event

occurs, the timer will automatically restart on the

rising edge of the reset pulse. If not enabled, the

watchdog timer runs but has no effect on /RST. Note

that setting the maximum timeout setting (11111b)

disables the counter to save power. The second

control is a nibble that restarts the timer preventing a

reset. The timer should be restarted after changing the

timeout value.

The watchdog timeout value is located in register

0Ah, bits 4-0, and the watchdog enable is bit 7. The

watchdog is restarted by writing the pattern 1010b to

the lower nibble of register 09h. Writing this pattern

will also cause the timer to load new timeout values.

Writing other patterns to this address will not affect

its operation. Note the watchdog timer is free-

running. Prior to enabling it, users should restart the

timer as described above. This assures that the full

timeout period will be set immediately after enabling.

The watchdog is disabled when VDD is below VTP.

The following table summarizes the watchdog bits. A

block diagram follows.

Watchdog timeout

Watchdog enable

Watchdog restart

WDT4-0

WDE

WR3-0

0Ah, bits 4-0

0Ah, bit 7

09h, bits 3-0

100 ms

clock

Timebase

WR3-0 = 1010b to restart

Counter

/RST

Watchdog

timeout

WDE

Figure 3. Watchdog Timer

Rev 2.1

Dec. 2004

FM3204/16/64/256

Manual Reset

The /RST pin is bi-directional and allows the

FM32xx to filter and de-bounce a manual reset

switch. The /RST input detects an external low

condition and responds by driving the /RST signal

low for 100 ms.

MCU

RST

Reset

Switch

FM32xx

Switch

Behavior

RST

FM32xx

drives

100 ms

Figure 4. Manual Reset

Note that an internal weak pull-up on /RST

eliminates the need for additional external

components.

Reset Flags

In case of a reset condition, a flag will be set to

indicate the source of the reset. A low VDD reset or

manual reset is indicated by the POR flag, register

09h bit 6. A watchdog reset is indicated by the WTR

flag, register 09h bit 7. Note that the flags are

internally set in response to reset sources, but they

must be cleared by the user. When the register is

read, it is possible that both flags are set if both have

occurred since the user last cleared them.

Early Power Fail Comparator

An early power fail warning can be provided to the

processor well before VDD drops out of spec. The

comparator is used to create a power fail interrupt

(NMI). This can be accomplished by connecting the

PFI pin to the unregulated power supply via a resistor

divider. An application circuit is shown below. The

voltage on the PFI input pin is compared to an

onboard 1.2V reference. When the PFI input voltage

drops below this threshold, the comparator will drive

the PFO pin to a low state. The comparator has 100

mV (max) of hysteresis to reduce noise sensitivity,

only for a rising PFI signal. For a falling PFI edge,

there is no hysteresis.

Page 5 of 20

5 Page

Two-wire Interface

The FM32xx employs an industry standard two-wire

bus that is familiar to many users. This product is

unique since it incorporates two logical devices in

one chip. Each logical device can be accessed

individually. Although monolithic, it appears to the

system software to be two separate products. One is

a memory device. It has a Slave Address (Slave ID =

1010b) that operates the same as a stand-alone

memory device. The second device is a real-time

clock and processor companion which have a unique

Slave Address (Slave ID = 1101b).

FM3204/16/64/256

By convention, any device that is sending data onto

the bus is the transmitter while the target device for

this data is the receiver. The device that is

controlling the bus is the master. The master is

responsible for generating the clock signal for all

operations. Any device on the bus that is being

controlled is a slave. The FM32xx is always a slave

device.

The bus protocol is controlled by transition states in

the SDA and SCL signals. There are four conditions:

Start, Stop, Data bit, and Acknowledge. The figure

below illustrates the signal conditions that specify

the four states. Detailed timing diagrams are shown

in the Electrical Specifications section.

SCL

SDA

76

0

Stop

Start

Data bits

Data bit Acknowledge

(Master) (Master)

(Transmitter)

(Transmitter) (Receiver)

Figure 7. Data Transfer Protocol

Start Condition

A Start condition is indicated when the bus master

drives SDA from high to low while the SCL signal is

high. All read and write transactions begin with a

Start condition. An operation in progress can be

aborted by asserting a Start condition at any time.

Aborting an operation using the Start condition will

ready the FM32xx for a new operation.

If the power supply drops below the specified VTP

during operation, any 2-wire transaction in progress

will be aborted and the system must issue a Start

condition prior to performing another operation.

Stop Condition

A Stop condition is indicated when the bus master

drives SDA from low to high while the SCL signal is

high. All operations must end with a Stop condition.

If an operation is pending when a stop is asserted,

the operation will be aborted. The master must have

control of SDA (not a memory read) in order to

assert a Stop condition.

Data/Address Transfer

All data transfers (including addresses) take place

while the SCL signal is high. Except under the two

conditions described above, the SDA signal should

not change while SCL is high.

Acknowledge

The Acknowledge (ACK) takes place after the 8th

data bit has been transferred in any transaction.

During this state the transmitter must release the

SDA bus to allow the receiver to drive it. The

receiver drives the SDA signal low to acknowledge

receipt of the byte. If the receiver does not drive

SDA low, the condition is a No-Acknowledge

(NACK) and the operation is aborted.

The receiver might NACK for two distinct reasons.

First is that a byte transfer fails. In this case, the

NACK ends the current operation so that the part can

be addressed again. This allows the last byte to be

recovered in the event of a communication error.

Second and most common, the receiver does not

send an ACK to deliberately terminate an operation.

For example, during a read operation, the FM32xx

will continue to place data onto the bus as long as the

receiver sends ACKs (and clocks). When a read

operation is complete and no more data is needed,

the receiver must NACK the last byte. If the receiver

ACKs the last byte, this will cause the FM32xx to

attempt to drive the bus on the next clock while the

master is sending a new command such as a Stop.

Rev 2.1

Dec. 2004

Page 11 of 20

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet FM3264.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| FM3264 | (FM3204 - FM32256) Integrated Processor Companion | Ramtron |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |