|

|

PDF DP83848T Data sheet ( Hoja de datos )

| Número de pieza | DP83848T | |

| Descripción | Industrial Temperature Single Port 10/100 Ethernet Transceiver | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DP83848T (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

October 2006

DP83848T PHYTER® Mini

DP83848K PHYTER® Mini LS

Industrial Temperature Single Port 10/100 Ethernet Transceiver

General Description

Features

The DP83848T/K addresses the quality, reliability and •

small form factor required for space sensitive applications •

in embedded systems operating in the industrial tempera-

ture range.

•

•

The DP83848T/K offers performance far exceeding the

IEEE specifications, with superior interoperability and •

industry leading performance beyond 137m of Cat-V •

cable. The DP83848T/K also offers Auto-MDIX to remove •

cabling complications. DP83848T/K has superior ESD pro-

tection, greater than 4KV Human Body Model, providing

•

extremely high reliability and robust operation, ensuring a •

high level performance in all applications.

•

DP83848K offers two flexible LED indicators - one for Link

and the other for Speed.

A 25MHz clock out that eliminates the need and hence the •

space and cost, of an additional Media Access Control •

(MAC) clock

DP83848T.

source

component

is

available

only

in

•

The DP83848T/K is offered in a tiny 6mm x 6mm LLP 40- •

pin package and is ideal for industrial controls, build- •

ing/factory automation, transportation and test equipment.

•

Applications

•

• Peripheral devices

•

• Mobile devices

• Factory and building automation

• Basestations

Low-power 3.3V, 0.18µm CMOS technology

3.3V MAC Interface

Auto-MDIX for 10/100 Mb/s

Energy Detection Mode

MII Interface

MII serial management interface (MDC and MDIO)

IEEE 802.3u Auto-Negotiation and Parallel Detection

IEEE 802.3u ENDEC, 10BASE-T transceivers and filters

IEEE 802.3u PCS, 100BASE-TX transceivers and filters

Integrated ANSI X3.263 compliant TP-PMD physical su-

blayer with adaptive equalization and Baseline Wander

compensation

Error-free Operation beyond 137 meters

ESD protection - Greater than 4KV Human body model

LED support for Link in DP83848T

LED support for Link and Speed in DP83848K

Supports system clock from oscillator (Not available in

DP83848K)

Single register access for complete PHY status

10/100 Mb/s packet BIST (Built in Self Test)

40 pin LLP package (6mm) x (6mm) x (0.8mm)

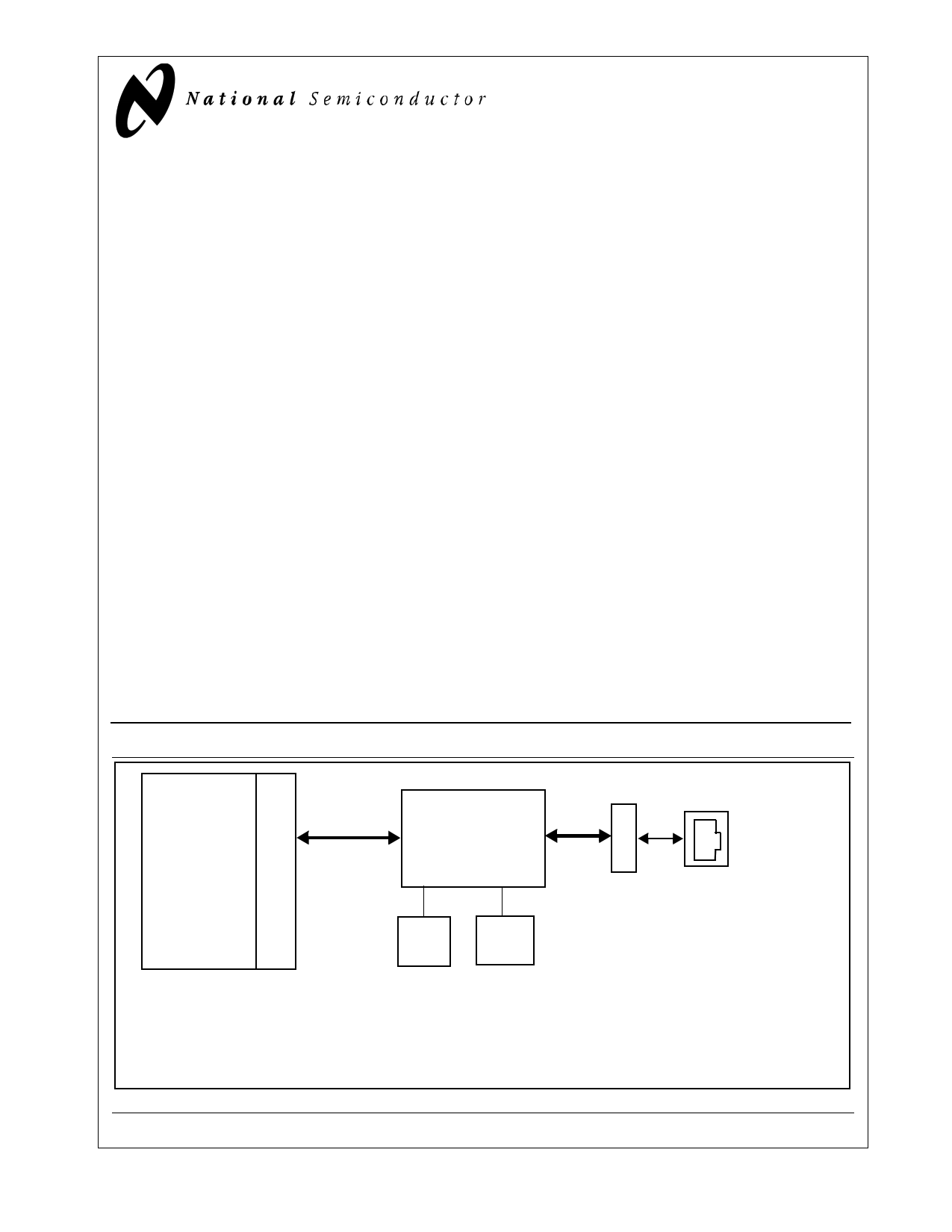

System Diagram

MPU/CPU

MII

PHYTER

Mini/ PHYTER

Mini LS

10/100 Ethernet

Transceiver

10BASE-T

or

100BASE-TX

Clock

Source

Status

LED/s

Typical Ethernet Application

PHYTER® is a registered trademark of National Semiconductor Corporation.

© 2006 National Semiconductor Corporation

www.national.com

1 page

8.2.18 10 Mb/s Jabber Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

8.2.19 10BASE-T Normal Link Pulse Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

8.2.20 Auto-Negotiation Fast Link Pulse (FLP) Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

8.2.21 100BASE-TX Signal Detect Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

8.2.22 100 Mb/s Internal Loopback Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

8.2.23 10 Mb/s Internal Loopback Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

8.2.24 Isolation Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

8.2.25 25 MHz_OUT Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

5 www.national.com

5 Page

Signal Name

COL

Type

S, O, PU

1.3 CLOCK INTERFACE

Pin #

35

Description

MII COLLISION DETECT: Asserted high to indicate detection of

a collision condition (simultaneous transmit and receive activity)

in 10 Mb/s and 100 Mb/s Half Duplex Modes.

While in 10BASE-T Half Duplex mode with heartbeat enabled this

pin is also asserted for a duration of approximately 1µs at the end

of transmission to indicate heartbeat (SQE test).

In Full Duplex Mode, for 10 Mb/s or 100 Mb/s operation, this sig-

nal is always logic 0. There is no heartbeat function during 10

Mb/s full duplex operation.

Signal Name

X1

Type

I

X2

25MHz_OUT

O

O

1.4 LED INTERFACE

See Table 4 for LED Mode Selection.

Pin #

28

27

21

Description

CRYSTAL/OSCILLATOR INPUT: This pin is the primary clock

reference input for the DP83848T/K and must be connected to a

25 MHz 0.005% (+50 ppm) clock source. The DP83848T/K sup-

ports either an external crystal resonator connected across pins

X1 and X2, or an external CMOS-level oscillator source connect-

ed to pin X1 only.

CRYSTAL OUTPUT: This pin is the primary clock reference out-

put to connect to an external 25 MHz crystal resonator device.

This pin must be left unconnected if an external CMOS oscillator

clock source is used.

25 MHz CLOCK OUTPUT:

This pin provides a 25 MHz clock output to the system.

This allows other devices to use the reference clock from the

DP83848T without requiring additional clock sources.

Note: This pin is not available in DP83848K.

Signal Name

LED_LINK

LED_SPEED

1.5 RESET

Type

S, O, PU

S, O, PU

Pin #

22

21

Description

LINK LED: In Mode 1, this pin indicates the status of the LINK.

The LED will be ON when Link is good.

LINK/ACT LED: In Mode 2, this pin indicates transmit and receive

activity in addition to the status of the Link. The LED will be ON

when Link is good. It will blink when the transmitter or receiver is

active.

SPEED LED: This LED is ON when DP83848K is in 100Mb/s and

OFF when DP83848K is in 10Mb/s. Functionality of this LED is in-

dependent of the mode selected.

Note: This pin is not available in DP83848T.

Signal Name

RESET_N

Type

I, PU

Pin #

23

Description

RESET: Active Low input that initializes or re-initializes the

DP83848T/K. Asserting this pin low for at least 1 µs will force a

reset process to occur. All internal registers will re-initialize to their

default states as specified for each bit in the Register Block sec-

tion. All strap options are re-initialized as well.

11 www.national.com

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet DP83848T.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DP83848-EP | PHYTER Extreme Temperature Single Port 10/100 Mb/s Ethernet Physical Layer (Rev. D) | Texas Instruments |

| DP83848-HT | DP83848-HT PHYTER Military Temperature Single Port 10/100 MB/S Ethernet Physical Layer Transceiver | Texas Instruments |

| DP83848C | PHYTER - Commercial Temperature Single Port 10/100 Mb/s Ethernet Physical Layer Transceiver | National Semiconductor |

| DP83848C | PHYTER QFP Single Port 10/100 Mb/s Ethernet Physical Layer Transceiver (Rev. E) | Texas Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |