|

|

PDF EPM7512B Data sheet ( Hoja de datos )

| Número de pieza | EPM7512B | |

| Descripción | (EPM7000B) Programmable Logic Device | |

| Fabricantes | Altera Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de EPM7512B (archivo pdf) en la parte inferior de esta página. Total 66 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

September 2003, ver. 3.4

®

MAX 7000B

Programmable Logic

Device

Data Sheet

Features...

f

■ High-performance 2.5-V CMOS EEPROM-based programmable logic

devices (PLDs) built on second-generation Multiple Array MatriX

(MAX®) architecture (see Table 1)

– Pin-compatible with the popular 5.0-V MAX 7000S and 3.3-V

MAX 7000A device families

– High-density PLDs ranging from 600 to 10,000 usable gates

– 3.5-ns pin-to-pin logic delays with counter frequencies in excess

of 303.0 MHz

■ Advanced 2.5-V in-system programmability (ISP)

– Programs through the built-in IEEE Std. 1149.1 Joint Test Action

Group (JTAG) interface with advanced pin-locking capability

– Enhanced ISP algorithm for faster programming

– ISP_Done bit to ensure complete programming

– Pull-up resistor on I/O pins during in-system programming

– ISP circuitry compliant with IEEE Std. 1532

For information on in-system programmable 5.0-V MAX 7000S or 3.3-V

MAX 7000A devices, see the MAX 7000 Programmable Logic Device Family

Data Sheet or the MAX 7000A Programmable Logic Device Family Data Sheet.

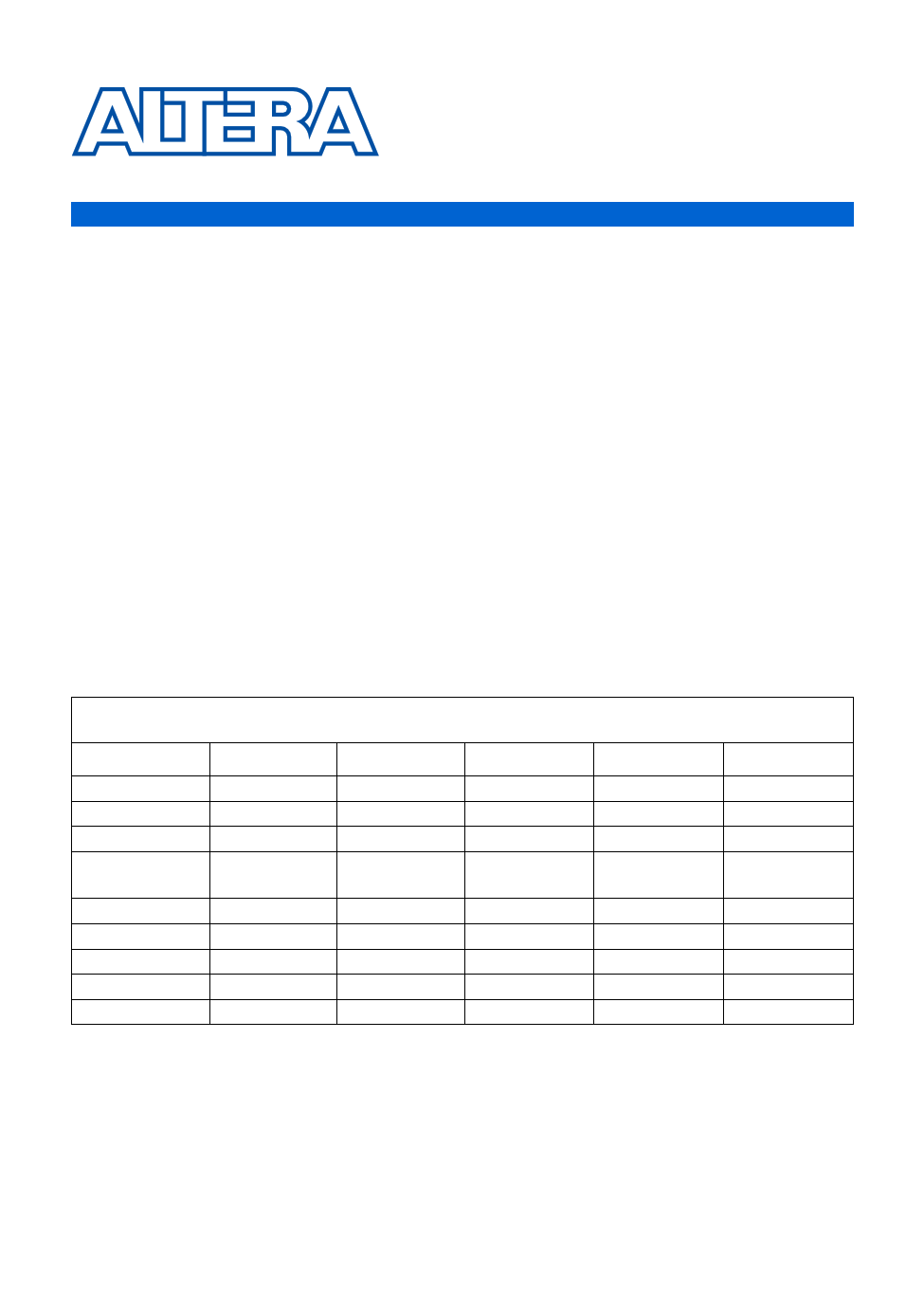

Table 1. MAX 7000B Device Features

Feature

Usable gates

Macrocells

Logic array blocks

Maximum user I/O

pins

tPD (ns)

tSU (ns)

tFSU (ns)

tCO1 (ns)

fCNT (MHz)

EPM7032B

600

32

2

36

3.5

2.1

1.0

2.4

303.0

EPM7064B

1,250

64

4

68

3.5

2.1

1.0

2.4

303.0

EPM7128B

2,500

128

8

100

4.0

2.5

1.0

2.8

243.9

EPM7256B

5,000

256

16

164

5.0

3.3

1.0

3.3

188.7

EPM7512B

10,000

512

32

212

5.5

3.6

1.0

3.7

163.9

Altera Corporation

DS-MAX7000B-3.4

1

1 page

MAX 7000B Programmable Logic Device Data Sheet

MAX 7000B devices provide programmable speed/power optimization.

Speed-critical portions of a design can run at high speed/full power,

while the remaining portions run at reduced speed/low power. This

speed/power optimization feature enables the designer to configure one

or more macrocells to operate up to 50% lower power while adding only

a nominal timing delay. MAX 7000B devices also provide an option that

reduces the slew rate of the output buffers, minimizing noise transients

when non-speed-critical signals are switching. The output drivers of all

MAX 7000B devices can be set for 3.3 V, 2.5 V, or 1.8 V and all input pins

are 3.3-V, 2.5-V, and 1.8-V tolerant, allowing MAX 7000B devices to be

used in mixed-voltage systems.

MAX 7000B devices are supported by Altera development systems, which

are integrated packages that offer schematic, text—including VHDL,

Verilog HDL, and the Altera Hardware Description Language (AHDL)—

and waveform design entry, compilation and logic synthesis, simulation

and timing analysis, and device programming. Altera software provides

EDIF 2 0 0 and 3 0 0, LPM, VHDL, Verilog HDL, and other interfaces for

additional design entry and simulation support from other industry-

standard PC- and UNIX-workstation-based EDA tools. Altera software

runs on Windows-based PCs, as well as Sun SPARCstation, and HP 9000

Series 700/800 workstations.

f

For more information on development tools, see the MAX+PLUS II

Programmable Logic Development System & Software Data Sheet and the

Quartus Programmable Logic Development System & Software Data Sheet.

Functional

Description

The MAX 7000B architecture includes the following elements:

■ LABs

■ Macrocells

■ Expander product terms (shareable and parallel)

■ PIA

■ I/O control blocks

The MAX 7000B architecture includes four dedicated inputs that can be

used as general-purpose inputs or as high-speed, global control signals

(clock, clear, and two output enable signals) for each macrocell and I/O

pin. Figure 1 shows the architecture of MAX 7000B devices.

Altera Corporation

5

5 Page

MAX 7000B Programmable Logic Device Data Sheet

Figure 4. MAX 7000B Parallel Expanders

Unused product terms in a macrocell can be allocated to a neighboring macrocell.

From

Previous

Macrocell

Product-

Term

Select

Matrix

Preset

Clock

Clear

Macrocell

Product-

Term Logic

36 Signals 16 Shared

from PIA Expanders

Product-

Term

Select

Matrix

Preset

Clock

Clear

Macrocell

Product-

Term Logic

To Next

Macrocell

Programmable Interconnect Array

Logic is routed between LABs on the PIA. This global bus is a

programmable path that connects any signal source to any destination on

the device. All MAX 7000B dedicated inputs, I/O pins, and macrocell

outputs feed the PIA, which makes the signals available throughout the

entire device. Only the signals required by each LAB are actually routed

from the PIA into the LAB. Figure 5 shows how the PIA signals are routed

into the LAB. An EEPROM cell controls one input to a two-input AND gate,

which selects a PIA signal to drive into the LAB.

Altera Corporation

11

11 Page | ||

| Páginas | Total 66 Páginas | |

| PDF Descargar | [ Datasheet EPM7512B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| EPM7512AE | Programmable Logic Device | Altera Corporation |

| EPM7512B | (EPM7000B) Programmable Logic Device | Altera Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |