|

|

PDF IDT71P72604 Data sheet ( Hoja de datos )

| Número de pieza | IDT71P72604 | |

| Descripción | (IDT71P72x04) 18Mb Pipelined QDRII SRAM Burst of 2 | |

| Fabricantes | IDT | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IDT71P72604 (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Advance

18Mb Pipelined

QDR™II SRAM

Burst of 2

Information

IDT71P72204

IDT71P72104

IDT71P72804

Features

Description

IDT71P72604

x 18Mb Density (2Mx8, 2Mx9, 1Mx18, 512kx36)

The IDT QDRIITM Burst of two SRAMs are high-speed synchronous

x Separate, Independent Read and Write Data Ports

memories with independent, double-data-rate (DDR), read and write

- Supports concurrent transactions

data ports. This scheme allows simultaneous read and write access for

x Dual Echo Clock Output

the maximum device throughput, with two data items passed with each

x 2-Word Burst on all SRAM accesses

read or write. Four data word transfers occur per clock cycle, providing

x DDR (Double Data Rate) Multiplexed Address Bus

quad-data-rate (QDR) performance. Comparing this with standard SRAM

- One Read and One Write request per clock cycle common I/O (CIO), single data rate (SDR) devices, a four to one in-

x DDR (Double Data Rate) Data Buses

crease in data access is achieved at equivalent clock speeds. Consider-

- Two word burst data per clock on each port

ing that QDRII allows clock speeds in excess of standard SRAM de-

- Four word transfers per clock cycle (2 word

vices, the throughput can be increased well beyond four to one in most

bursts on 2 ports)

applications.

x Depth expansion through Control Logic

Using independent ports for read and write data access, simplifies

x HSTL (1.5V) inputs that can be scaled to receive signals system design by eliminating the need for bi-directional buses. All buses

from 1.4V to 1.9V.

associated with the QDRII are unidirectional and can be optimized for

x Scalable output drivers

signal integrity at very high bus speeds. The QDRII has scalable output

- Can drive HSTL, 1.8V TTL or any voltage level impedance on its data output bus and echo clocks, allowing the user to

from 1.4V to 1.9V.

tune the bus for low noise and high performance.

- Output Impedance adjustable from 35 ohms to 70

The QDRII has a single DDR address bus with multiplexed read and

ohms write addresses. All read addresses are received on the first half of the

x 1.8V Core Voltage (VDD)

clock cycle and all write addresses are received on the second half of the

x 165-ball, 1.0mm pitch, 13mm x 15mm fBGA Package

clock cycle. The read and write enables are received on the first half of

x JTAG Interface

the clock cycle. The byte and nibble write signals are received on both

halves of the clock cycle simultaneously with the data they are controlling

on the data input bus.

The QDRII has echo clocks, which provide the user with a clock

Functional Block Diagram

(Note1)

D

DATA

REG

DATA

REG

(Note1)

(Note1)

SA (Note2)

ADD

REG

(Note2)

R

W

BWx

CTRL

(Note3) LOGIC

WRITE DRIVER

18M

MEMORY

ARRAY

(Note4)

(Note4)

(Note1) Q

Notes

K CLK

K GEN

C SELECT OUTPUT CONTROL

C

CQ

CQ

6109 drw 16

1) Represents 8 data signal lines for x8, 9 signal lines for x9, 18 signal lines for x18, and 36 signal lines for x36

2) Represents 20 address signal lines for x8 and x9, 19 address signal lines for x18, and 18 address signal lines for x36.

3) Represents 1 signal line for x9, 2 signal lines for x18, and four signal lines for x36. On x8 parts, the BW is a “nibble write” and there are 2

signal lines.

4) Represents 16 data signal lines for x8, 18 signal lines for x9, 36 signal lines for x18, and 72 signal lines for x36.

MAY 2004

1

©2003 Integrated Device Technology, Inc. “QDR SRAMs and Quad Data Rate RAMs comprise a new family of products developed by Cypress Semiconductor, IDT, and Micron Technology, Inc. “ DSC-6109/0C

1 page

IDT71P72204 (2M x 8-Bit), 71P72104 (2M x 9-Bit), 71P72804 (1M x 18-Bit) 71P72604 (512K x 36-Bit)

Advance Information

18 Mb QDR II SRAM Burst of 2

Commercial Temperature Range

Pin Configuration 2M x 8

1 2 3 4 5 6 7 8 9 10 11

A CQ VSS/ SA W NW1 K

SA (2)

NC R

SA VSS/ CQ

SA (1)

B NC NC NC SA NC K NW0 SA NC NC Q3

C NC NC NC VSS SA SA SA VSS NC NC D3

D NC D4 NC VSS VSS VSS VSS VSS NC NC NC

E

NC NC

Q4

VDDQ

VSS

VSS

VSS VDDQ

NC

D2

Q2

F NC NC NC VDDQ VDD VSS VDD VDDQ NC NC NC

G

NC

D5

Q5

VDDQ

VDD

VSS

VDD VDDQ

NC

NC NC

H

Doff

VREF

VDDQ

VDDQ

VDD

VSS

VDD

VDDQ

VDDQ

VREF

ZQ

J NC NC NC VDDQ VDD VSS VDD VDDQ NC Q1 D1

K NC NC NC VDDQ VDD VSS VDD VDDQ NC NC NC

L

NC Q6

D6

VDDQ

VSS

VSS

VSS VDDQ

NC

NC

Q0

M NC NC NC VSS VSS VSS VSS VSS NC NC D0

N NC D7 NC VSS SA SA SA VSS NC NC NC

P NC NC Q7 SA SA C SA SA NC NC NC

R

TDO TCK

SA

SA

SA

C

SA SA SA TMS TDI

6109 tbl 12

165-ball FBGA Pinout

TOP VIEW

NOTES:

1. A10 is reserved for the 36Mb expansion address.

2. A2 is reserved for the 72Mb expansion address.

6.542

5 Page

IDT71P72204 (2M x 8-Bit), 71P72104 (2M x 9-Bit), 71P72804 (1M x 18-Bit) 71P72604 (512K x 36-Bit)

Advance Information

18 Mb QDR II SRAM Burst of 2

Commercial Temperature Range

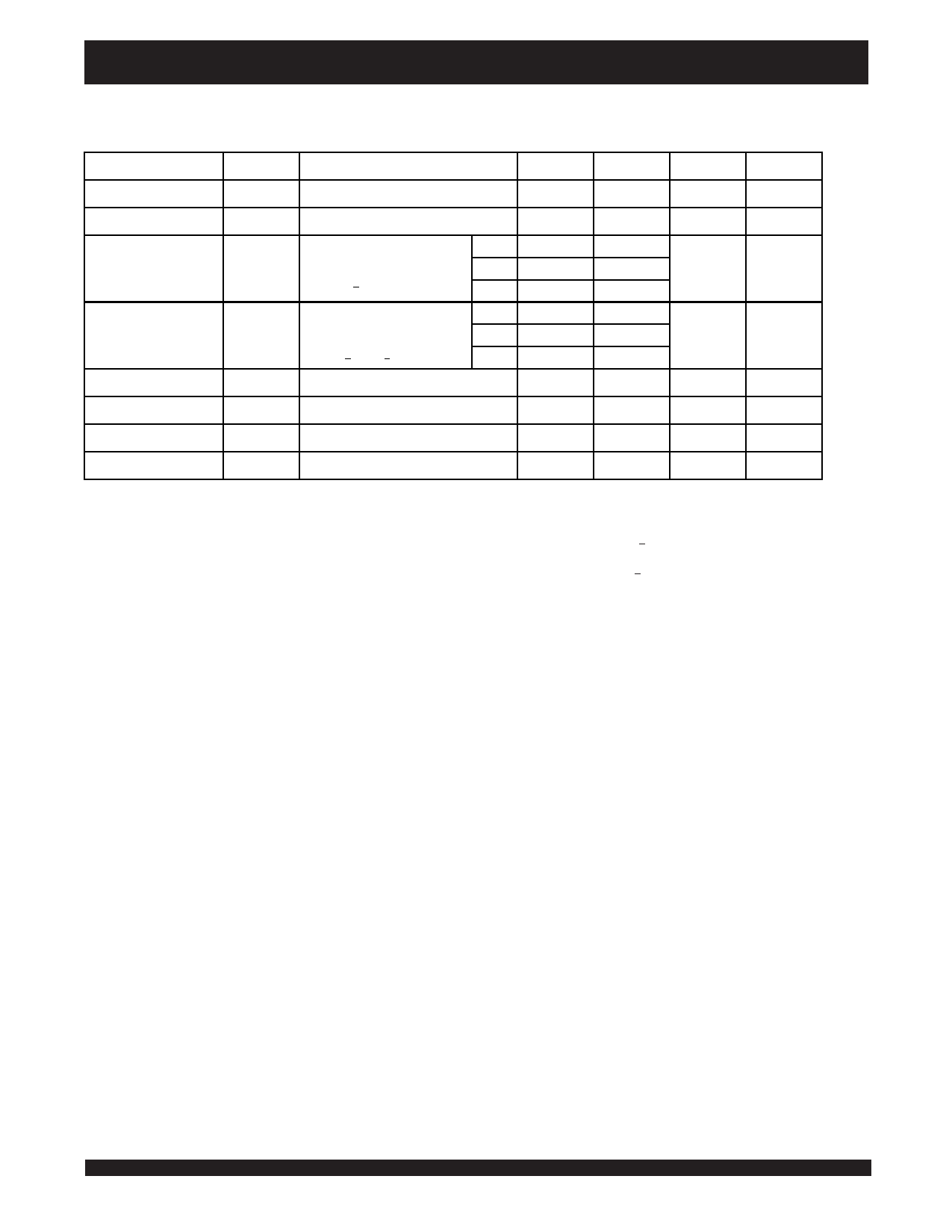

DC Electrical Characteristics Over the Operating Temperature and

Supply Voltage Range (VDD = 1.8 ± 100mV, VDDQ = 1.4V to 1.9V)

Parameter

Input Leakage Current

Output Leakage Current

Symbol

IIL

IOL

Test Conditions

VDD = Max VIN = VSS to VDDQ

Output Disabled

Min Max Unit

-10 +10 µA

-10 +10 µA

Operating Current

(x36,x18,x9,x8): DDR

Standby Current: NOP

Output High Voltage

Output Low Voltage

IDD

ISB1

VOH1

VOL1

VDD = Max,

IOUT = 0mA (outputs open),

Cycle Time > tKHKH Min

Device Deselected (in NOP state),

Iout = 0mA (outputs open),

f=Max,

All Inputs <0.2V or > VDD -0.2V

RQ = 250Ω, IOH = -15mA

RQ = 250Ω, IOL = 15mA

250MHZ

200MHZ

167MHZ

250MHZ

200MHZ

167MHZ

-

-

-

-

-

-

VDDQ/2-0.12

VDDQ/2-0.12

TBD

TBD

TBD

TBD

TBD

TBD

VDDQ/2+0.12

VDDQ/2+0.12

mA

mA

V

V

Output High Voltage

Output Low Voltage

VOH2

VOL2

IOH = -0.1mA

IOL = 0.1mA

VDDQ-0.2

VSS

VDDQ

0.2

V

V

NOTES:

1. Operating Current is measured at 100% bus utilization.

2. Standby Current is only after all pending read and write burst operations are completed.

3. Outputs are impedance-controlled. IOH = -(VDDQ/2)/(RQ/5) and is guaranteed by device characterization for 175Ω < RQ < 350Ω. This

parameter is tested at RQ = 250Ω, which gives a nominal 50Ω output impedance.

4. Outputs are impedance-controlled. IOL = (VDDQ/2)/(RQ/5) and is guaranteed by device characterization for 175Ω < RQ < 350Ω. This

parameter is tested at RQ = 250Ω, which gives a nominal 50Ω output impedance.

5. This measurement is taken to ensure that the output has the capability of pulling to the VDDQ rail, and is not intended to be used as an

impedance measurement point.

6. This measurement is taken to ensure that the output has the capability of pulling to Vss, and is not intended to be used as an impedance

measurement point.

7. Programmable Impedance Mode.

Note

1

2

3,7

4,7

5

6

6109 tbl 10c

61.412

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet IDT71P72604.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IDT71P72604 | (IDT71P72x04) 18Mb Pipelined QDRII SRAM Burst of 2 | IDT |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |