|

|

PDF 56F807 Data sheet ( Hoja de datos )

| Número de pieza | 56F807 | |

| Descripción | 16-bit Hybrid Processor | |

| Fabricantes | Motorola Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 56F807 (archivo pdf) en la parte inferior de esta página. Total 52 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Freescale Semiconductor, Inc.

DSP56F807/D

Rev. 12.0, 02/2004

56F807

Technical Data

56F807 16-bit Hybrid Processor

• Up to 40 MIPS at 80MHz core frequency

• DSP and MCU functionality in a unified,

C-efficient architecture

• Up to 64K × 16- bit words each of external

Program and Data memory

• Two 6 channel PWM Modules

• Hardware DO and REP loops

• Four 4 channel, 12-bit ADCs

• MCU-friendly instruction set supports both

DSP and controller functions: MAC, bit

manipulation unit, 14 addressing modes

• 60K × 16-bit words Program Flash

• 2K × 16-bit words Program RAM

• 8K × 16-bit words Data Flash

• 4K × 16-bit words Data RAM

• 2K × 16-bit words Boot Flash

• Two Quadrature Decoders

• CAN 2.0 B Module

• Two Serial Communication Interfaces (SCIs)

• Serial Peripheral Interface (SPI)

• Up to four General Purpose Quad Timers

• JTAG/OnCETM port for debugging

• 14 Dedicated and 18 Shared GPIO lines

• 160-pin LQFP or 160 MAPBGA Packages

6

PWM Outputs

Current Sense Inputs

3

Fault Inputs

4

6

PWM Outputs

3 Current Sense Inputs

Fault Inputs

4

4 A/D1 ADCA

4 A/D2 VREF

4

A/D1 ADCB

A/D2

4 VREF2

Quadrature

Decoder 0

4 /Quad Timer

PWMA

PWMB

RSTO

EXTBOOT

RESET IRQB

IRQA

6

JTAG/

OnCE

Port

VPP VCAPC VDD VSS VDDA

28

10* 3

VSSA

3

Digital Reg Analog Reg

Low Voltage

Supervisor

Interrupt

Controller

Program Controller

and

Hardware Looping Unit

Address

Generation

Unit

Data ALU

16 x 16 + 36 → 36-Bit MAC

Three 16-bit Input Registers

Two 36-bit Accumulators

Bit

Manipulation

Unit

Quadrature

Decoder 1

Program Memory

4

/Quad Timer B

61440 x 16 Flash

2048 x 16 SRAM

Quad Timer C

2 Boot Flash

Quad Timer D

2048 x 16 Flash

4 / Alt Func

CAN 2.0A/B

Data Memory

2

SCI0

8192 x 16 Flash

4096 x 16 SRAM

or

2 GPIO

SCI1

or

2 GPIO

COP/

Watchdog

SPI Applica-

or tion-Specific

4

GPIO

Memory &

Dedicated

GPIO

Peripherals

14

••

PAB

PDB

•

XDB2

CGDB

• • •XAB1

•XAB2

•INTERRUPT

IPBB

CONTROLS CONTROLS

16 16

COP RESET

MODULE CONTROLS

ADDRESS BUS [8:0]

DATA BUS [15:0]

IPBus Bridge

(IPBB)

16-Bit

56800

Core

PLL

Clock Gen

CLKO

XTAL

EXTAL

External 6

Address Bus

A[00:05]

A[06:15] or

External

Bus

Interface

Unit

Switch

External

Data Bus

Switch

GPIO-E2:E3 &

10 GPIO-A0:A7

D[00:15]

16

PS Select

Bus DS Select

Control

WR Enable

RD Enable

*includes TCS pin which is reserved for factory use and is tied to VSS

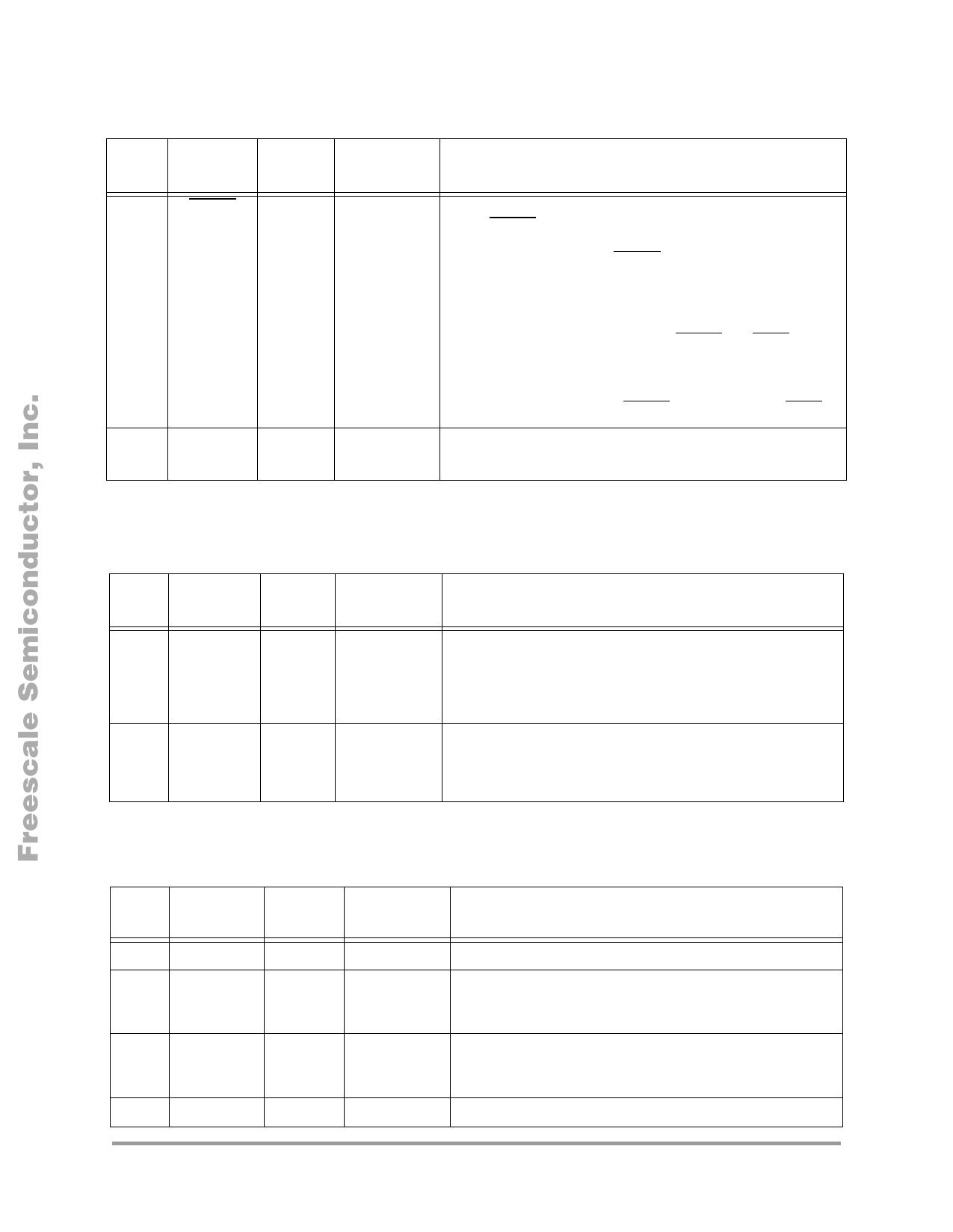

Figure 1. 56F807 Block Diagram

© Motorola, Inc., 2004. All rights reserved.

For More Information On This Product,

Go to: www.freescale.com

1 page

www.DataSheet4U.com

Freescale Semiconductor, Inc.

Product Documentation

1.4 Product Documentation

The four documents listed in Table 1 are required for a complete description and proper design with the 56F807.

Documentation is available from local Motorola distributors, Motorola semiconductor sales offices, Motorola

Literature Distribution Centers, or online at http://www.motorola.com/semiconductors.

Table 1. 56F807 Chip Documentation

Topic

Description

Order Number

DSP56800

Family Manual

DSP56F801/803/805/807

User’s Manual

56F807

Technical Data Sheet

56F807

Product Brief

DSP56F807

Errata

Detailed description of the 56800 family architecture,

and 16-bit core processor and the instruction set

DSP56800FM/D

Detailed description of memory, peripherals, and

interfaces of the 56F801, 56F803, 56F805, and

56F807

DSP56F801-7UM/D

Electrical and timing specifications, pin descriptions,

and package descriptions (this document)

DSP56F807/D

Summary description and block diagram of the 56F807 DSP56F807PB/D

core, memory, peripherals and interfaces

Details any chip issues that might be present

DSP56F807E/D

1.5 Data Sheet Conventions

This data sheet uses the following conventions:

OVERBAR

This is used to indicate a signal that is active when pulled low. For example, the RESET pin is

active when low.

“asserted”

A high true (active high) signal is high or a low true (active low) signal is low.

“deasserted” A high true (active high) signal is low or a low true (active low) signal is high.

Examples:

Signal/Symbol

Logic State

Signal State

Voltage1

PIN

True

Asserted

VIL/VOL

PIN

False

Deasserted

VIH/VOH

PIN

True

Asserted

VIH/VOH

PIN

False

Deasserted

1. Values for VIL, VOL, VIH, and VOH are defined by individual product specifications.

VIL/VOL

56F807 Technical Data

For More Information On This Product,

Go to: www.freescale.com

5

5 Page

www.DataSheet4U.com

Freescale Semiconductor, Inc.

GPIO Signals

Table 10. Interrupt and Program Control Signals (Continued)

No. of

Pins

Signal

Name

Signal

Type

State During

Reset

Signal Description

1

RESET

Input

(Schmitt)

1 EXTBOOT Input

(Schmitt)

Input

Input

Reset—This input is a direct hardware reset on the processor.

When RESET is asserted low, the device is initialized and

placed in the Reset state. A Schmitt trigger input is used for

noise immunity. When the RESET pin is deasserted, the initial

chip operating mode is latched from the EXTBOOT pin. The

internal reset signal will be deasserted synchronous with the

internal clocks, after a fixed number of internal clocks.

To ensure complete hardware reset, RESET and TRST should

be asserted together. The only exception occurs in a

debugging environment when a hardware device reset is

required and it is necessary not to reset the OnCE/JTAG

module. In this case, assert RESET, but do not assert TRST.

External Boot—This input is tied to VDD to force device to boot

from off-chip memory. Otherwise, it is tied to VSS.

2.6 GPIO Signals

Table 11. Dedicated General Purpose Input/Output (GPIO) Signals

No. of

Pins

Signal

Name

8 GPIOB0-G

PIOB7

6 GPIOD0-G

PIOD5

Signal

Type

Input

or

Output

Input

or

Output

State During

Reset

Signal Description

Input

Input

Port B GPIO—These eight pins are dedicated General

Purpose I/O (GPIO) pins that can individually be programmed

as input or output pins.

After reset, the default state is GPIO input.

Port D GPIO—These six pins are dedicated GPIO pins that

can individually be programmed as an input or output pins.

After reset, the default state is GPIO input.

2.7 Pulse Width Modulator (PWM) Signals

Table 12. Pulse Width Modulator (PWMA and PWMB) Signals

No. of

Pins

Signal

Name

Signal

Type

State During

Reset

Signal Description

6 PWMA0-5 Output Tri- stated PWMA0-5— Six PWMA output pins.

3 ISA0-2 Input

Input

ISA0-2— These three input current status pins are used for

(Schmitt)

top/bottom pulse width correction in complementary channel

operation for PWMA.

4 FAULTA0-3 Input

(Schmitt)

Input

FAULTA0-3— These Fault input pins are used for disabling

selected PWMA outputs in cases where fault conditions

originate off-chip.

6 PWMB0-5 Output Tri- stated PWMB0-5— Six PWMB output pins.

56F807 Technical Data

For More Information On This Product,

Go to: www.freescale.com

11

11 Page | ||

| Páginas | Total 52 Páginas | |

| PDF Descargar | [ Datasheet 56F807.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 56F801 | 16-bit Hybrid Controller | Motorola Semiconductors |

| 56F801 | 16-bit Digital Signal Controllers | Freescale Semiconductor |

| 56F8011 | (56F8011 / 56F8013) 16-Bit Digital Signal Controller | Motorola Semiconductor |

| 56F8013 | 16-bit Digital Signal Controllers | Freescale Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |