|

|

PDF AD8684 Data sheet ( Hoja de datos )

| Número de pieza | AD8684 | |

| Descripción | High Speed JFET Operational Amplifiers | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD8684 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

Dual/Quad Low Power, High Speed

JFET Operational Amplifiers

AD8682/AD8684

FEATURES

Low supply current: 250 μA/amp maximum

High slew rate: 9 V/μs

Bandwidth: 3.5 MHz typical

Low offset voltage: 1 mV maximum @ 25°C

Low input bias current: 20 pA maximum @ 25°C

CMRR: 90 dB typical

Fast settling time

Unity-gain stable

APPLICATIONS

Portable telecommunications

Low power industrial and instrumentation

Loop filters

Active and precision filters

Integrators

Strain gauge amplifiers

Portable medical instrumentation

Supply current monitoring

GENERAL DESCRIPTION

The AD8682 and AD8684 are dual and quad low power, precision

(1 mV) JFET amplifiers featuring excellent speed at low supply

currents. The slew rate is typically 9 V/μs with a supply current

under 250 μA per amplifier. These unity-gain stable amplifiers

have a typical gain bandwidth of 3.5 MHz. The JFET input stage

ensures bias current is typically a few picoamps and below

125 pA maximum over the full temperature operating range.

PIN CONFIGURATIONS

OUT A 1

–IN A 2

+IN A 3

V– 4

AD8682

TOP VIEW

(Not to Scale)

8 V+

7 OUT B

6 –IN B

5 +IN B

Figure 1. 8-Lead SOIC_N and 8-Lead MSOP

OUT A 1

–IN A 2

+IN A 3

V+ 4

+IN B 5

–IN B 6

OUT B 7

AD8684

14 OUT D

13 –IN D

12 +IN D

11 V–

10 +IN C

9 –IN C

8 OUT C

TOP VIEW

(Not to Scale)

Figure 2. 14-Lead SOIC_N and 14-Lead TSSOP

The devices are ideal for portable, low power applications,

especially with high source impedance. The devices are unity-gain

stable and can drive higher capacity loads (G = 1, noninverting),

as an example of their excellent dynamic response over a wide

range of conditions, delivering dc precision performance at low

quiescent currents.

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113 ©2006–2008 Analog Devices, Inc. All rights reserved.

1 page

TYPICAL PERFORMANCE CHARACTERISTICS

80 180

VS = ±15V

TA = 25°C

60 135

40 90

20 45

00

–20 –45

–40

1k

10k 100k

FREQUENCY (Hz)

1M

–90

10M

Figure 3. AD8682 Open-Loop Gain and Phase vs. Frequency

45

VS = ±15V

40 RL = 10kΩ

35

30

25

20

15

10

5

0

–75 –50 –25

0

25 50 75 100 125

TEMPERATURE (°C)

Figure 4. AD8682 Open-Loop Gain vs. Temperature

80

VS = ±15V

70

RL = 2kΩ

VIN = 100mV p-p

AVCL = 1

60 TA = 25°C

50

40

+OS

–OS

30

20

10

0

0 100 200 300 400 500

LOAD CAPACITANCE (pF)

Figure 5. Small Signal Overshoot vs. Load Capacitance

AD8682/AD8684

70

VS = ±15V

60 TA = 25°C

50

AVCL = 100

40

30

AVCL = 10

20

10

AVCL = 1

0

–10

–20

–30

1k

10k 100k

FREQUENCY (Hz)

1M

Figure 6. AD8682 Closed-Loop Gain vs. Frequency

10M

30

VS = ±15V

RL = 10kΩ

25 CL = 50pF

–SR

20

15

10

+SR

5

0

–75 –50 –25

0

25 50 75 100 125

TEMPERATURE (°C)

Figure 7. Slew Rate vs. Temperature

1000

VS = ±15V

VCM = 0V

100

10

1

0.1

–75 –50 –25

0

25 50 75 100 125

TEMPERATURE (°C)

Figure 8. AD8682 Input Bias Current vs. Temperature

Rev. B | Page 5 of 16

5 Page

AD8682/AD8684

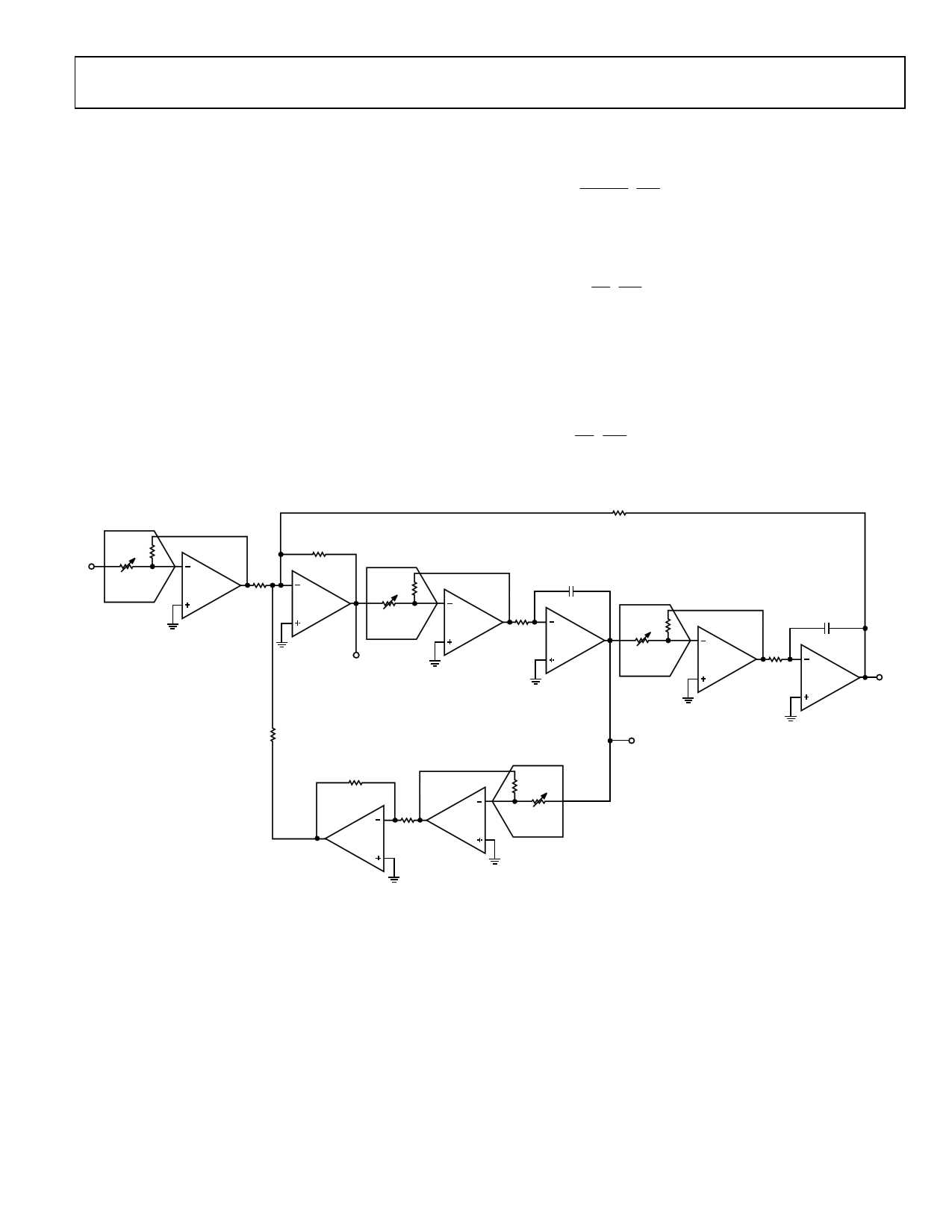

PROGRAMMABLE STATE VARIABLE FILTER

The circuit shown in Figure 35 can be used to accurately program

the Q factor; the cutoff frequency (fC); and the gain of a two-

pole state variable filter. The AD8684 has been used in this

design because of its high bandwidth, low power, and low noise.

This circuit takes only three packages to build because of the

quad configuration of the op amps and DACs.

The DACs shown are used in voltage mode; therefore, many

values are dependent on the accuracy of the DAC only and not

on the absolute values of the DAC resistive ladders. As a result, this

makes the circuit unusually accurate for a programmable filter.

Adjusting DAC 1 changes the signal amplitude across R1; therefore,

the DAC attenuation × R1 determines the amount of signal current

that charges the integrating capacitor, C1.

This cutoff frequency can be expressed as

fC

=

2πR11C1 ⎜⎝⎛

D1

256

⎟⎠⎞

where D1 is the digital code for the DAC.

DAC 3 is used to set the gain. The gain equation is

Gain

=

R4

R5

⎜⎝⎛

D3

256

⎟⎠⎞

DAC 2 is used to set the Q of the circuit. Adjusting this DAC

controls the amount of feedback from the band-pass node to

the input summing node. Note that the digital value of the

DAC is in the numerator; therefore, zero code is not a valid

operating point.

Q

=

R2

R3

⎜⎝⎛

256

D2

⎟⎠⎞

DAC 3

VIN

1/4

DAC8408

1/4

AD8684

R5

2kΩ

R6

2kΩ

R4

2kΩ

1/4

AD8684

DAC 1

1/4

DAC8408

HIGH PASS

R7

2kΩ

1/4

AD8684

C1

1000pF

R1

2kΩ

1/4

AD8684

DAC 4

1/4

DAC8408

1/4

AD8684

C1

1000pF

R1

2kΩ

1/4

AD8684

LOW

PASS

R3

2kΩ

1/4

AD8684

R2

2kΩ

1/4

AD8684

DAC 2

1/4

DAC8408

BAND PASS

Figure 35. Programmable State Variable Filter

Rev. B | Page 11 of 16

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet AD8684.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD8682 | High Speed JFET Operational Amplifiers | Analog Devices |

| AD8684 | High Speed JFET Operational Amplifiers | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |