No Preview Available !

CXD2498R

Timing Generator for Frame Readout CCD Image Sensor

Description

The CXD2498R is a timing generator IC which

generates the timing pulses for performing frame

readout using the ICX282 CCD image sensor.

48 pin LQFP (Plastic)

Features

• Base oscillation frequency 45MHz

• Electronic shutter function

• Supports various drive modes such as draft and

AF mode

• Horizontal driver for CCD image sensor

• Vertical driver for CCD image sensor

Applications

Digital still cameras

Structure

Silicon gate CMOS IC

Applicable CCD Image Sensors

ICX282 (Type 2/3, 5070K pixels)

Absolute Maximum Ratings

• Supply voltage VDD VSS – 0.3 to +7.0

VL –10.0 to VSS

VH VL – 0.3 to +26.0

• Input voltage VI VSS – 0.3 to VDD + 0.3

• Output voltage VO1 VSS – 0.3 to VDD + 0.3

VO2 VL – 0.3 to VSS + 0.3

VO3 VL – 0.3 to VH + 0.3

• Operating temperature

Topr –20 to +75

• Storage temperature

Tstg

–55 to +150

V

V

V

V

V

V

V

°C

°C

Recommended Operating Conditions

• Supply voltage

VDDa, VDDb, VDDc 3.0 to 3.6

VM 0.0

VH 14.5 to 15.5

VL –7.0 to –8.0

• Operating temperature

Topr –20 to +75

V

V

V

V

°C

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

–1–

E00X63-PS

1 page

CXD2498R

Pin

No.

Symbol

32 SCK

33 SEN

34 VD

35 HD

36 VSS5

37 VM

38 V2

39 V4

40 V1A

41 VH

42 V1B

43 V1C

44 V3A

45 VL

46 V3B

47 V3C

48 SUB

I/O Description

I Serial interface clock input for internal mode settings.

I Serial interface strobe input for internal mode settings.

I/O Vertical sync signal input/output.

I/O Horizontal sync signal input/output.

— GND

— GND (GND for vertical driver)

O CCD vertical register clock output.

O CCD vertical register clock output.

O CCD vertical register clock output.

— 15.0V power supply. (Power supply for vertical driver)

O CCD vertical register clock output.

O CCD vertical register clock output.

O CCD vertical register clock output.

— –7.5V power supply. (Power supply for vertical driver)

O CCD vertical register clock output.

O CCD vertical register clock output.

O CCD electronic shutter pulse output.

Schmitt trigger input

Schmitt trigger input

–5–

5 Page

CXD2498R

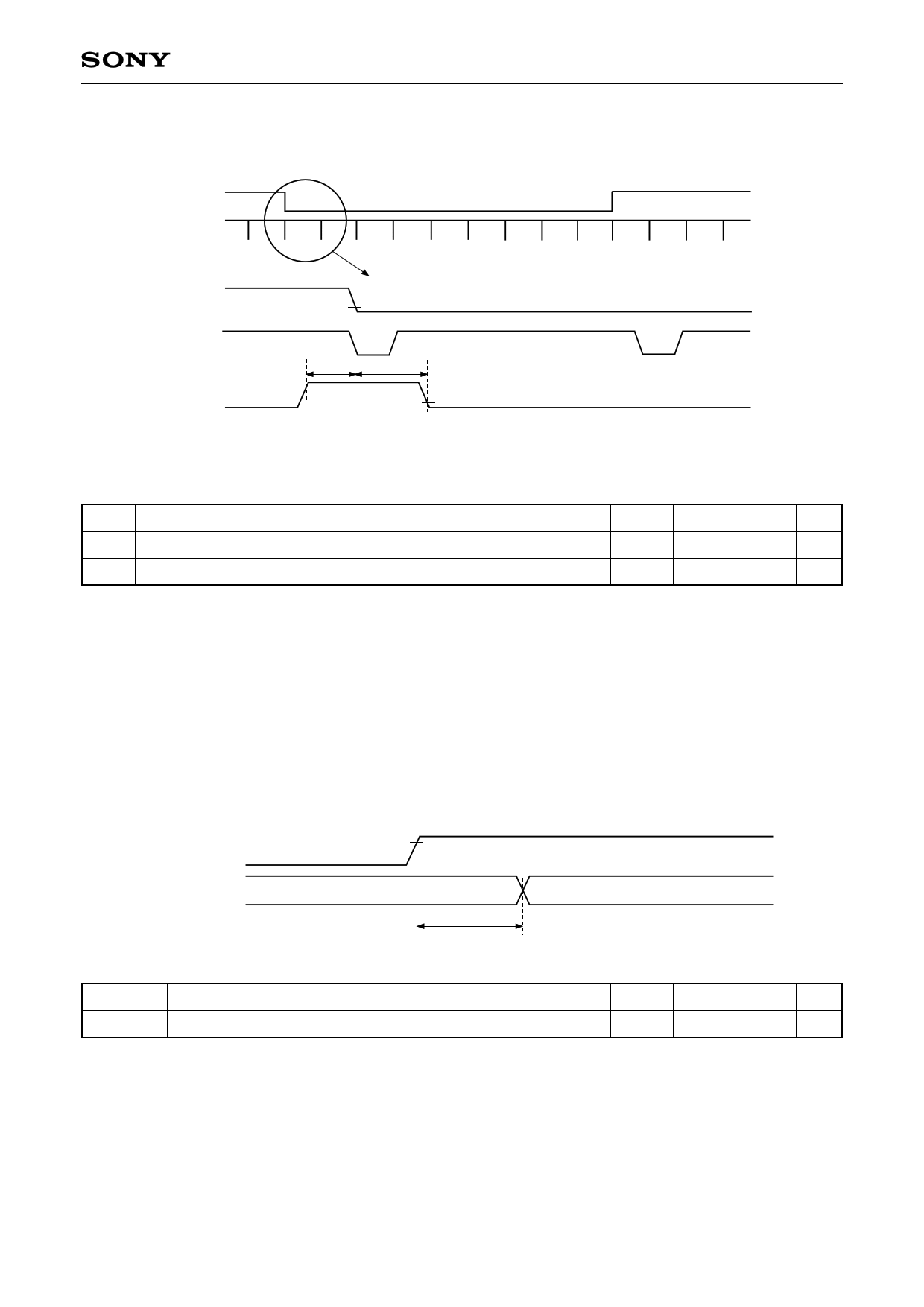

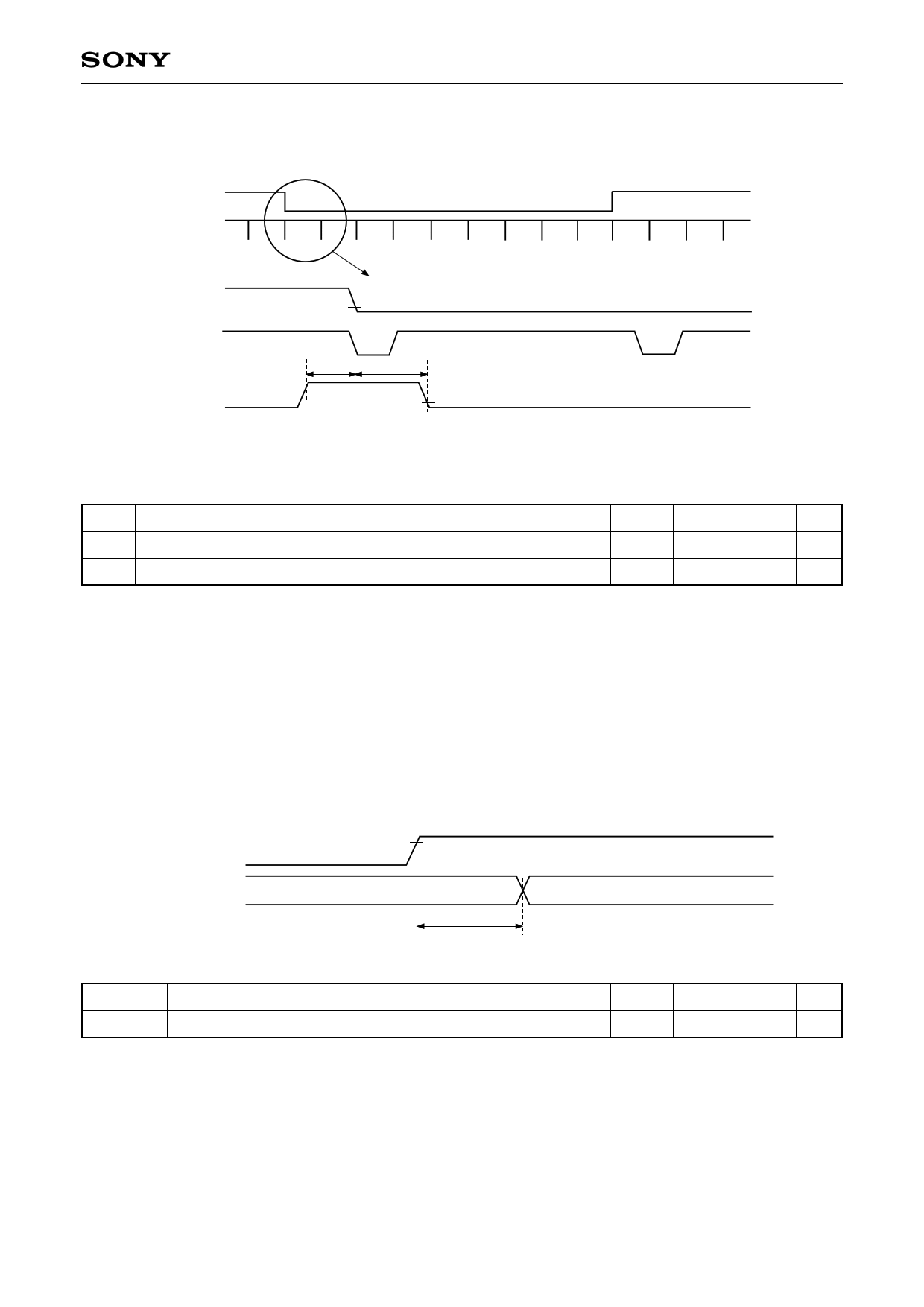

Serial interface clock internal loading characteristics (2)

Example: During frame mode

VD

HD

Enlarged view

VD

HD

SEN

0.2VDDc

0.8VDDc

ts1

th1

0.2VDDc

∗ Be sure to maintain a constantly high SEN logic level near the falling edge of VD.

(Within the recommended operating conditions)

Symbol

Definition

ts1 SEN setup time, activated by the falling edge of VD

th1 SEN hold time, activated by the falling edge of VD

Min. Typ. Max. Unit

0 ns

200 ns

∗ Restriction with an operating frequency of 22.5MHz.

Serial interface clock output variation characteristics

Normally, the serial interface data is loaded to the CXD2498R at the timing shown in “Serial interface clock

internal loading characteristics (1)” above. However, one exception to this is when the data such as STB is

loaded to the CXD2498R and controlled at the rising edge of SEN. See ”Description of Operation”.

SEN

0.8VDDc

Output signal

tpdPULSE

(Within the recommended operating conditions)

Symbol

Definition

tpdPULSE Output signal delay, activated by the rising edge of SEN

Min. Typ. Max. Uniy

5 70 ns

– 11 –

11 Page

|