|

|

PDF IDT72V81 Data sheet ( Hoja de datos )

| Número de pieza | IDT72V81 | |

| Descripción | 3.3 Volt CMOS DUAL ASYNCHRONOUS FIFO | |

| Fabricantes | Integrated Device Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IDT72V81 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

3.3 Volt CMOS DUAL ASYNCHRONOUS FIFO

DUAL 512 x 9, DUAL 1,024 x 9

DUAL 2,048 x 9, DUAL 4,096 X 9

DUAL 8,192 X 9

IDT72V81

IDT72V82

IDT72V83

IDT72V84

IDT72V85

FEATURES:

• The IDT72V81 is equivalent to two IDT72V01 - 512 x 9 FIFOs

• The IDT72V82 is equivalent to two IDT72V02 - 1,024 x 9 FIFOs

• The IDT72V83 is equivalent to two IDT72V03 - 2,048 x 9 FIFOs

• The IDT72V84 is equivalent to two IDT72V04 - 4,096 x 9 FIFOs

• The IDT72V85 is equivalent to two IDT72V05 - 8,192 x 9 FIFOs

• Low power consumption

— Active: 330 mW (max.)

— Power-down: 18 mW (max.)

• Ultra high speed—15 ns access time

• Asynchronous and simultaneous read and write

• Offers optimal combination of data capacity, small foot print

and functional flexibility

• Ideal for bidirectional, width expansion, depth expansion, bus-

matching, and data sorting applications

• Status Flags: Empty, Half-Full, Full

• Auto-retransmit capability

• High-performance CMOS™ technology

• Space-saving TSSOP package

• Industrial temperature range (–40°C to +85°C) is available

• Green parts available, see ordering information

DESCRIPTION:

The IDT72V81/72V82/72V83/72V84/72V85 are dual-FIFO memories that

load and empty data on a first-in/first-out basis. These devices are functional and

compatible to two IDT72V01/72V02/72V03/72V04/72V05 FIFOs in a single

package with all associated control, data, and flag lines assigned to separate

pins. The devices use Full and Empty flags to prevent data overflow and

underflow and expansion logic to allow for unlimited expansion capability in both

word size and depth.

The reads and writes are internally sequential through the use of ring

pointers, with no address information required to load and unload data. Data

is toggled in and out of the devices through the use of the Write (W) and Read

(R) pins.

The devices utilize a 9-bit wide data array to allow for control and parity

bitsattheuser’soption.Thisfeatureis especiallyusefulindatacommunications

applications where it is necessary to use a parity bit for transmission/reception

error checking. It also features a Retransmit (RT) capability that allows for reset

of the read pointer to its initial position when RT is pulsed low to allow for

retransmission from the beginning of data. A Half-Full Flag is available in the

single device mode and width expansion modes.

These FIFOs are fabricated using high-speed CMOS technology. They are

designed for those applications requiring asynchronous and simultaneous

read/writes in multiprocessing and rate buffer applications.

FUNCTIONAL BLOCK DIAGRAM

DATA INPUTS

(DA0-DA8)

RSA

WA

WRITE

CONTROL

WRITE

POINTER

RAM

ARRAY A

512 x 9

1,024 x 9

2,048 x 9

4,096 x 9

8,192 x 9

READ

POINTER

THREE-

STATE

BUFFERS

RA READ

CONTROL

FLAG

LOGIC

EXPANSION

LOGIC

XIA

XOA/HFA FFA EFA

DATA

OUTPUTS

(QA0-QA8)

RESET

LOGIC

FLA/RTA

WB

WRITE

CONTROL

DATA INPUTS

(DB0-DB8)

RSB

WRITE

POINTER

THREE-

STATE

BUFFERS

RAM

ARRAY A

512 x 9

1,024 x 9

2,048 x 9

4,096 x 9

8,192 x 9

READ

POINTER

READ

CONTROL

FLAG

LOGIC

EXPANSION

LOGIC

RB XIB

XOB/HFB FFB EFB

DATA

OUTPUTS

(QB0-QB8)

RESET

LOGIC

FLB/RTB

3966 drw 01

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc. The AsyncFIFO™ is a trademark of Integrated Device Technology, Inc.

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

1

© 2012 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice.

JUNE 2012

DSC-3966/5

1 page

IDT72V81/72V82/72V83/72V84/72V85 3.3V CMOS DUAL ASYNCHRONOUS FIFO

512 x 9, 1024 x 9, 2048 x 9, 4096 x 9, 8192 x 9

tRSC

RS tRS

tRSS

W

tRSS

R

tEFL

EF

tHFH, tFFH

HF, FF

NOTES:

1. EF, FF, HF may change status during Reset, but flags will be valid at tRSC.

2. W and R = VIH around the rising edge of RS.

Figure 2. Reset

COMMERCIAL ANDINDUSTRIAL

TEMPERATURERANGES

tRSR

3966 drw 04

R

Q0-Q8

W

D0-D8

tRC

tA tRR

tRPW

tA

tRLZ

tWPW

tDV

DATA OUT VALID

tWC

tWR

tRHZ

DATA OUT VALID

tDS tDH

DATA IN VALID

DATA IN VALID

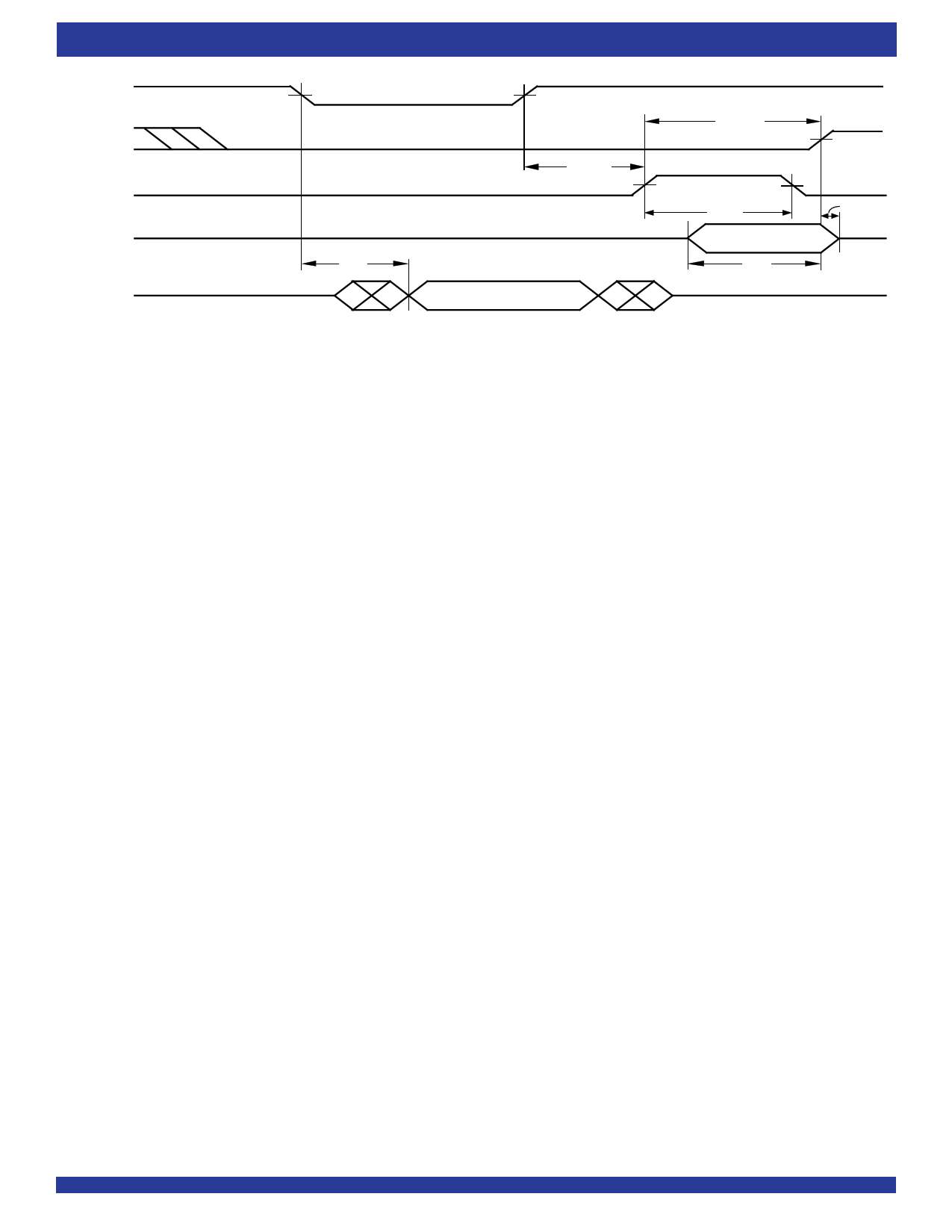

Figure 3. Asynchronous Write and Read Operation

3966 drw 05

LAST WRITE

IGNORED

WRITE

FIRST READ

ADDITIONAL FIRST

READS

WRITE

R

W

tWFF

FF

tRFF

Figure 4. Full Flag From Last Write to First Read

5

3966 drw 06

5 Page

IDT72V81/72V82/72V83/72V84/72V85 3.3V CMOS DUAL ASYNCHRONOUS FIFO

512 x 9, 1024 x 9, 2048 x 9, 4096 x 9, 8192 x 9

R

W

tRFF

FF

DATA IN

DATA OUT

tA

DATA OUT VALID

Figure 18. Write Data Flow-Through Mode

COMMERCIAL ANDINDUSTRIAL

TEMPERATURERANGES

tWPF

tWFF

DATA IN VALID

tDS

tDH

3966 drw 20

11

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet IDT72V81.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IDT72V801 | 3.3 VOLT DUAL CMOS SyncFIFO | Integrated Device Tech |

| IDT72V805 | 3.3 VOLT CMOS DUAL SyncFIFO DUAL 256 x 18/ DUAL 512 x 18/ DUAL 1/024 x 18/ DUAL 2/048 x 18 | Integrated Device Tech |

| IDT72V81 | 3.3 Volt CMOS DUAL ASYNCHRONOUS FIFO | Integrated Device Technology |

| IDT72V811 | 3.3 VOLT DUAL CMOS SyncFIFO | Integrated Device Tech |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |