|

|

PDF EDD2516AKTA-5-E Data sheet ( Hoja de datos )

| Número de pieza | EDD2516AKTA-5-E | |

| Descripción | 256M bits DDR SDRAM (16M words x16 bits DDR400) | |

| Fabricantes | Elpida Memory | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de EDD2516AKTA-5-E (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

( DataSheet : www.DataSheet4U.com )

DATA SHEET

256M bits DDR SDRAM

EDD2516AKTA-5-E (16M words × 16 bits, DDR400)

Description

The EDD2516AKTA-5 is a 256M bits DDR SDRAM

organized as 4,194,304 words × 16 bits × 4 banks.

Read and write operations are performed at the cross

points of the CK and the /CK. This high-speed data

transfer is realized by the 2 bits prefetch-pipelined

architecture. Data strobe (DQS) both for read and

write are available for high speed and reliable data bus

design. By setting extended mode register, the on-chip

Delay Locked Loop (DLL) can be set enable or disable.

It is packaged in 66-pin plastic TSOP (II).

Features

• Power supply: VDD, VDDQ = 2.6V ± 0.1V

• Data rate: 400Mbps (max.)

• Double Data Rate architecture; two data transfers per

clock cycle

• Bi-directional data strobe (DQS) is transmitted

/received with data for capturing data at the receiver

• Data inputs, outputs, and DM are synchronized with

DQS

• 4 internal banks for concurrent operation

• DQS is edge aligned with data for READs; center

aligned with data for WRITEs

• Differential clock inputs (CK and /CK)

• DLL aligns DQ and DQS transitions with CK

transitions

• Commands entered on each positive CK edge; data

and data mask referenced to both edges of DQS

• Data mask (DM) for write data

• Auto precharge option for each burst access

• SSTL_2 compatible I/O

• Programmable burst length (BL): 2, 4, 8

• Programmable /CAS latency (CL): 3

• Programmable output driver strength: normal/weak

• Refresh cycles: 8192 refresh cycles/64ms

7.8µs maximum average periodic refresh interval

• 2 variations of refresh

Auto refresh

Self refresh

• TSOP (II) package with lead free solder (Sn-Bi)

RoHS compliant

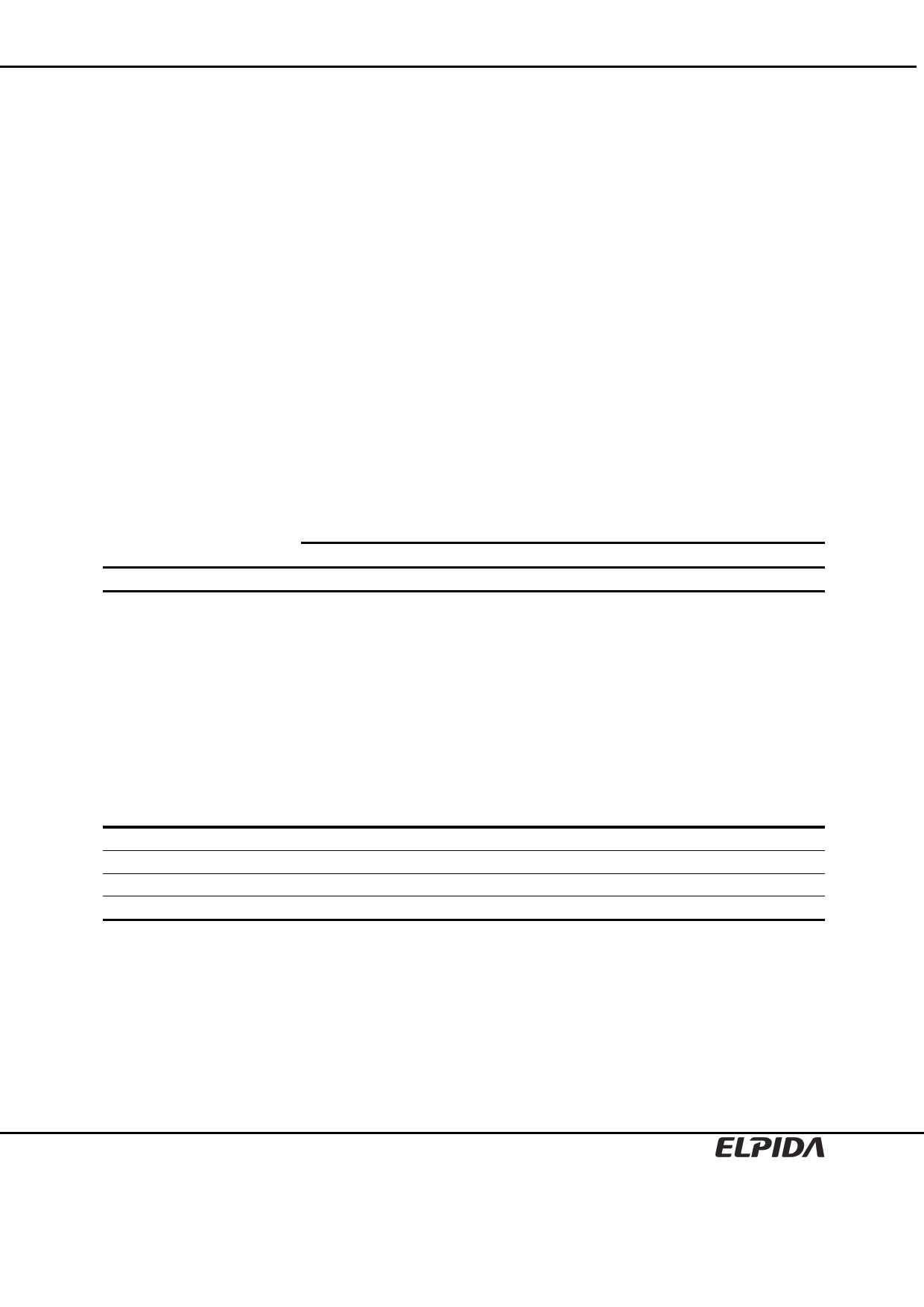

Pin Configurations

/xxx indicates active low signal.

66-pin Plastic TSOP(II)

VDD

DQ0

VDDQ

DQ1

DQ2

VSSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VSSQ

DQ7

NC

VDDQ

LDQS

NC

VDD

NC

LDM

/WE

/CAS

/RAS

/CS

NC

BA0

BA1

A10(AP)

A0

A1

A2

A3

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

66 VSS

65 DQ15

64 VSSQ

63 DQ14

62 DQ13

61 VDDQ

60 DQ12

59 DQ11

58 VSSQ

57 DQ10

56 DQ9

55 VDDQ

54 DQ8

53 NC

52 VSSQ

51 UDQS

50 NC

49 VREF

48 VSS

47 UDM

46 /CK

45 CK

44 CKE

43 NC

42 A12

41 A11

40 A9

39 A8

38 A7

37 A6

36 A5

35 A4

34 VSS

(Top view)

A0 to A12

BA0, BA1

DQ0 to DQ15

UDQS/LDQS

/CS

/RAS

/CAS

/WE

UDM/LDM

CK

/CK

CKE

VREF

VDD

VSS

VDDQ

VSSQ

NC

Address input

Bank select address

Data-input/output

Input and output data strobe

Chip select

Row address strobe command

Column address strobe command

Write enable

Input mask

Clock input

Differential clock input

Clock enable

Input reference voltage

Power for internal circuit

Ground for internal circuit

Power for DQ circuit

Ground for DQ circuit

No connection

Document No. E0638E20 (Ver. 2.0)

Date Published September 2005 (K) Japan

Printed in Japan

URL: http://www.elpida.com

Elpida Memory, Inc. 2005

www.DataSheet4U.com

1 page

EDD2516AKTA-5-E

DC Characteristics 1 (TA = 0 to +70°C, VDD, VDDQ = 2.6V ± 0.1V, VSS, VSSQ = 0V)

max.

Parameter

Symbol

Grade × 16

Unit Test condition

Operating current (ACT-PRE)

Operating current

(ACT-READ-PRE)

IDD0

IDD1

100

mA

CKE ≥ VIH,

tRC = tRC (min.)

135

mA

CKE ≥ VIH, BL = 4,CL = 3,

tRC = tRC (min.)

Idle power down standby current

IDD2P

3 mA CKE ≤ VIL

Floating idle standby current

Quiet idle standby current

IDD2F

IDD2Q

30

mA

CKE ≥ VIH, /CS ≥ VIH

DQ, DQS, DM = VREF

25

mA

CKE ≥ VIH, /CS ≥ VIH

DQ, DQS, DM = VREF

Active power down standby current IDD3P

20 mA CKE ≤ VIL

Active standby current

Operating current

(Burst read operation)

Operating current

(Burst write operation)

IDD3N

IDD4R

IDD4W

60

mA

CKE ≥ VIH, /CS ≥ VIH

tRAS = tRAS (max.)

230 mA CKE ≥ VIH, BL = 2, CL = 3

240 mA CKE ≥ VIH, BL = 2,CL = 3

Auto Refresh current

IDD5

170

mA

tRFC = tRFC (min.),

Input ≤ VIL or ≥ VIH

Self refresh current

Operating current

(4 banks interleaving)

IDD6

IDD7A

3

mA

Input ≥ VDD – 0.2 V

Input ≤ 0.2 V

350 mA BL = 4

Notes: 1. These IDD data are measured under condition that DQ pins are not connected.

2. One bank operation.

3. One bank active.

4. All banks idle.

5. Command/Address transition once per one clock cycle.

6. DQ, DM and DQS transition twice per one clock cycle.

7. 4 banks active. Only one bank is running at tRC = tRC (min.)

8. The IDD data on this table are measured with regard to tCK = tCK (min.) in general.

9. Command/Address transition once every two clock cycle.

10. Command/Address stable at ≥ VIH or ≤ VIL.

DC Characteristics 2 (TA = 0 to +70°C, VDD, VDDQ = 2.6V ± 0.1V, VSS, VSSQ = 0V)

Parameter

Input leakage current

Output leakage current

Output high current

Output low current

Symbol

ILI

ILO

IOH

IOL

min.

–2

–5

–15.2

15.2

max.

2

5

—

—

Unit Test condition

µA VDD ≥ VIN ≥ VSS

µA VDDQ ≥ VOUT ≥ VSS

mA VOUT = 1.95V

mA VOUT = 0.35V

Notes

1, 2, 9

1, 2, 5

4

4, 5

4, 10

3

3, 5, 6

1, 2, 5, 6

1, 2, 5, 6

1, 5, 6, 7

Note

Data Sheet E0638E20 (Ver. 2.0)

5

5 Page

EDD2516AKTA-5-E

Pin Function

CK, /CK (input pins)

The CK and the /CK are the master clock inputs. All inputs except DM, DQS and DQs are referred to the cross point

of the CK rising edge and the /CK falling edge. When a read operation, DQS and DQs are referred to the cross point

of the CK and the /CK. When a write operation, DQS and DQs are referred to the cross point of the DQS and the

VREF level. DQS for write operation is referred to the cross point of the CK and the /CK. CK is the master clock

input to this pin. The other input signals are referred at CK rising edge.

/CS (input pin)

When /CS is Low, commands and data can be input. When /CS is High, all inputs are ignored. However, internal

operations (bank active, burst operations, etc.) are held.

/RAS, /CAS, and /WE (input pins)

These pins define operating commands (read, write, etc.) depending on the combinations of their voltage levels.

See "Command operation".

A0 to A12 (input pins)

Row address (AX0 to AX12) is determined by the A0 to the A12 level at the cross point of the CK rising edge and the

/CK falling edge in a bank active command cycle. Column address (See “Address Pins Table”) is loaded via the A0

to the A8 at the cross point of the CK rising edge and the /CK falling edge in a read or a write command cycle. This

column address becomes the starting address of a burst operation.

[Address Pins Table]

Address (A0 to A12)

Part number

Row address

Column address

EDD2516AKTA

AX0 to AX12

AY0 to AY8

A10 (AP) (input pin)

A10 defines the precharge mode when a precharge command, a read command or a write command is issued. If

A10 = High when a precharge command is issued, all banks are precharged. If A10 = Low when a precharge

command is issued, only the bank that is selected by BA1/BA0 is precharged. If A10 = High when read or write

command, auto-precharge function is enabled. While A10 = Low, auto-precharge function is disabled.

BA0 and BA1 (input pins)

BA0, BA1 are bank select signals (BA). The memory array is divided into bank 0, bank 1, bank 2 and bank 3. (See

Bank Select Signal Table)

[Bank Select Signal Table]

BA0

BA1

Bank 0

L

L

Bank 1

H

L

Bank 2

L

H

Bank 3

H

H

Remark: H: VIH. L: VIL.

Data Sheet E0638E20 (Ver. 2.0)

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet EDD2516AKTA-5-E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| EDD2516AKTA-5-E | 256M bits DDR SDRAM (16M words x16 bits DDR400) | Elpida Memory |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |