|

|

PDF CLA90000 Data sheet ( Hoja de datos )

| Número de pieza | CLA90000 | |

| Descripción | High Density CMOS Gate Arrays | |

| Fabricantes | Zarlink Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CLA90000 (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

( DataSheet : www.DataSheet4U.com )

CLA90000 Series

High Density CMOS Gate Arrays

INTRODUCTZarlinkION

The CLA90000 family of gate arrays from Zarlink Semicon-

ductor consists of 14 fixed-size arrays with the option of

building optimized arrays with up to 1.1 million gates. This

family offers low-power, mixed voltage capability and a high

density silicon architecture. The CLA90000 series is easy

to use with and without synthesis tools and comes with

design utilities to provide customers with a faster time to

market.

FEATURES

I Low power, 0.5µW/MHz/gate at 3V supply (NAND 2

loads)

I High density of 5,425 available gates/mm2

I 3V and 5V I/O capability on the same device

I 150ps gate delay for 2-input NAND with two loads (5V)

I Accurate delay modelling for gates and tracks with sign

off quality CAE design libraries for QuickSim II and

Verilog-XL

I CAD libraries optimized for synthesis

I Up to 512K available gates and 352 pads with fixed

arrays

I Up to 1.1M available gates and 520 pads with optimized

arrays

I Double or triple layer metal on a 0.6µm (drawn) process

I Operation from 2.7V to 5.5V

I Methodologies for low clock skew

I Phase locked loop cells, both gate array variant and

embedded variant with on-chip filter

I Embedded RAM and ROM

I Expanding range of Zarlink SytemBuilder soft and

hard cells for complex functions including 85C30, 8051,

and 8251 devices

I Wide range of packaging options including Ball Grid

Arrays

I Commercial and military pad density options

DS5500

ISSUE 2.0

April 1997

BENEFITS

I Fast Customer Time To Market

- Direct sign-off on industry standard CAE tools

- Comprehensive industry-standard design tool flows

- SystemBuilder™ megacell libraries

- Worldwide design centre support

- Reliable prototype and production delivery

- Two silicon sources

I Cost-effective solutions

- Optimized silicon architecture for excellent silicon

utilization

- Statistical process control for optimum yield

- High quality and reliability, manufactured to MIL STD

883 methods and other industry recognized standards

OVERVIEW

The CLA90000 series product has a number of important

elements that assist designers.

Ease of design

Ease of design is an important feature of this new product,

as shown by the checking and verification utilities built into

the Zarlink design kits. Accurate simulation is essential for

good design, and the Zarlink 5th order pin to pin delay

model algorithms help ensure first time success. Various

design routes and industry-standard systems are avail-

able.

Cell Libraries

Cell libraries are optimized for synthesis and include a

complete range of soft and hard macros. Cells include

basic logic, oscillators, JTAG controllers and macros from

the extensive SystemBuilder™ library such as micropro-

cessors, memories, UARTs, and DSP elements, which

improve time to market through a shorter design cycle.

Embedded custom blocks can be inserted into a gate

array to produce dense memory or other compact high

performance components. Optimized arrays can offer gate

array cycle times if embedded blocks are defined early in

the design cycle.

www.DataSheet4U.com

www.DataSheet4U.com

1 page

DESIGN SUPPORT

I Flexible design routes

I Proven right first time design

I Local design support

Design and layout support for the CLA90000 arrays is

available from many local centres worldwide, each con-

nected to our headquarters via high speed data links. A

design centre engineer, as part of the Zarlink support

team, is assigned to each customer circuit to give full

assistance with all aspects of the design and to ensure a

smooth and efficient design flow.

Zarlink offers both customer and turnkey design routes, to

allow for varying types of customer interface while main-

taining our responsibility to ensure first time working

devices.

The design process incorporates a design audit procedure

to verify compliance with customer specification and to

ensure manufacturability. The procedure includes three

review meetings with the customer held at key stages of

the design. This is illustrated in the diagram on the next

page.

Design review one:

Held at the beginning of the design

cycle to check and agree on per-

formance, packaging, specifica-

tions and design timescales.

Design review two:

Held after logic simulation but prior

to layout to ensure satisfactory

functionality, timing performance,

and adequate fault coverage.

Design review three:

Held after layout and post-layout

simulation verification of satisfac-

tory design performance after

insertion of actual track loads. Final

check of all device specifications

before prototype manufacture.

CAE Support

I Synthesis with Synopsys, Mentor or Cadence

I Sign-off simulation with Mentor or Cadence

I VIEWlogic VCS simulator supported

I VITAL compliant library

I Full top-down design flow support

I Point tools supported, including Zycad and Powermill

I Direct route to layout and test

I Advanced delay modelling and netlist checking

It is Zarlink policy to fully support industry-standard CAE

systems that enable a customer to sign off their design

without resimulation on a golden simulator. This has the

benefit to the customer of not having to learn new tools,

and to use the tools they prefer and are familiar with. There

is no overhead in engineering effort or time taken recheck-

ing simulation results.

Zarlink offers libraries for synthesis tools such as Synop-

sys, Mentor Autologic II, and Cadence Synergy. This

allows a full hierarchical or top-down approach to logic

design. The Zarlink Universal Delay Compiler (UDC) is

supplied with all design kits for advanced delay modelling

and comprehensive netlist checking. The UDC matches

Synopsys and Mentor native delay calculation.

The advanced features of the synthesis and simulation

tools are used for nonlinear delay modelling for better sim-

ulation accuracy. This is implemented for optimum speed

depending on the particular tool. Other advanced features

are supported where they are available.

The information supplied by the customer in the approved

CAE vendor format is used as a direct input to the tools

that perform the layout and generate the test program.

5

5 Page

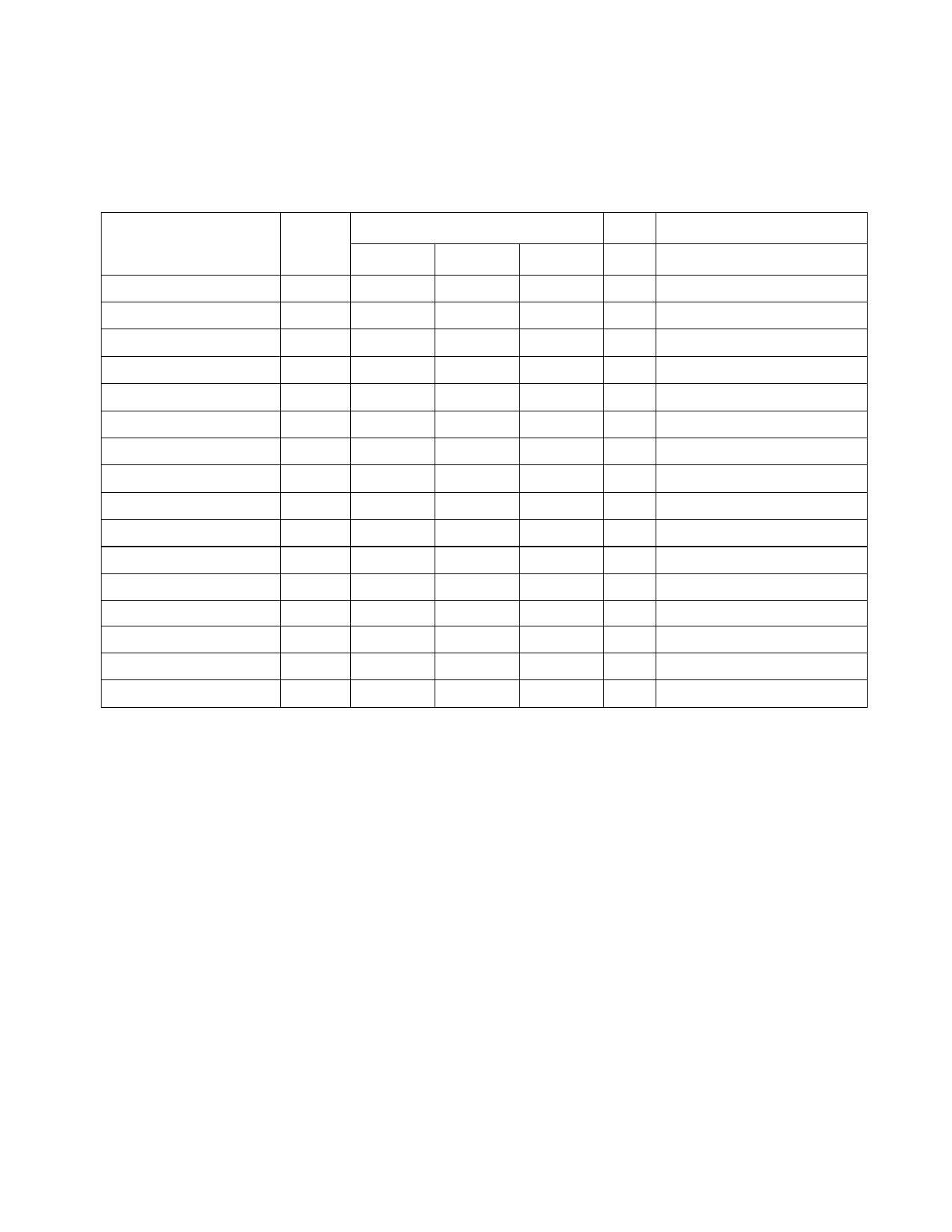

Input Switching Thresholds

All characteristics are for temperatures between -55 and 150°C (junction temperature).

Characteristic

Symbol

CMOS Schmitt - CS

Input low voltage

Input high voltage

Hysteresis

TTL Schmitt - TS

Input low voltage

Input high voltage

Hysteresis

Low voltage Schmitt - BS/NS

Input low voltage

Input high voltage

Hysteresis

Low voltage Schmitt - BS/NS

Input low voltage

Input high voltage

Hysteresis

VIL

VIH

VH

VIL

VIH

VH

VIL

VIH

VH

VIL

VIH

VH

Min.

0.7VDD

400

2.0

300

2.0

300

2.2

100

Value

Typ.

Max.

Unit

0.2VDD

V

V

mV

0.8 V

V

mV

0.2VDD

V

V

mV

0.2VDD

V

V

mV

Conditions

4.5 ≤ VDD ≤ 5.5V

4.5 ≤ VDD ≤ 5.5V

2.7 ≤ VDD ≤ 3.3V

3.0 £ VDD £ 3.6V

Note: CS cells are 5V CMOS compatible, TS cells are 5V TTL compatible and all other cells are 3V compatible.

11

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet CLA90000.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CLA90000 | High Density CMOS Gate Arrays | Zarlink Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |