|

|

PDF DP83843BVJE Data sheet ( Hoja de datos )

| Número de pieza | DP83843BVJE | |

| Descripción | PHYTER | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DP83843BVJE (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

July 1999

DP83843BVJE PHYTER

General Description

Features

The DP83843BVJE is a full feature Physical Layer device

with integrated PMD sublayers to support both 10BASE-T

and 100BASE-X Ethernet protocols.

This VLSI device is designed for easy implementation of

10/100 Mb/s Ethernet LANs. It interfaces directly to Twisted

Pair media through an external transformer or to fiber

media via industry standard electrical/optical fiber PMD

transceivers. This device also interfaces directly to the

MAC layer through the IEEE 802.3u standard Media Inde-

pendent Interface (MII), ensuring interoperability between

products from different vendors.

The DP83843 is designed with National Semiconductor's

advanced CMOS process. Its system architecture is based

on the integration of several of National's industry proven

core technologies:

— IEEE 802.3 ENDEC with AUI/10BASE-T transceiver

module to provide the 10 Mb/s functions

— Clock Recovery/Generator Modules from National's Fast

Ethernet and FDDI products

— FDDI Stream Cipher scrambler/descrambler for

TP-PMD

— 100BASE-X physical coding sub-layer (PCS) and control

logic that integrates the core modules into a dual speed

Ethernet physical layer controller

— ANSI X3T12 Compliant TP-PMD Transceiver

technology with Baseline Wander (BLW) compensation

— IEEE 802.3 ENDEC with AUI/10BASE-T transceivers

and built-in filters

— IEEE 802.3u 100BASE-TX compatible - directly drives

standard Category 5 UTP, no need for external

100BASE-TX transceiver

— Fully Integrated and fully compliant ANSI X3.263 TP-

PMD physical sublayer which includes adaptive equal-

ization and BLW compensation

— IEEE 802.3u 100BASE-FX compatible - connects direct-

ly to industry standard Electrical/Optical transceivers

— IEEE 802.3u Auto-Negotiation for automatic speed se-

lection

— IEEE 802.3u compatible Media Independent Interface

(MII) with Serial Management Interface

— Integrated high performance 100 Mb/s clock recovery

circuitry requiring no external filters

— Full Duplex support for 10 and 100 Mb/s data rates

— MII Serial 10 Mb/s mode

— Fully configurable node/switch and 100Mb/s repeater

modes

— Programmable loopback modes for flexible system diag-

nostics

— Flexible LED support

— Single register access to complete PHY status

— MDIO interrupt support

— Individualized scrambler seed for 100BASE-TX applica-

tions using multiple PHYs

— Low power consumption for multi-port applications

— Small footprint 80-pin PQFP package

System Diagram

10BASE-T or

100BASE-TX

MII

10 AND/OR 100 Mb/s

ETHERNET MAC OR

100Mb/s REPEATER

CONTROLLER

DP83843

10/100 Mb/s

ETHERNET PHYSICAL LAYER

10BASE-T

RJ-45

or

100BASE-TX

25 MHz

CLOCK

STATUS

LEDS

ThunderLAN® is a registered trademark of Texas Instruments.

TWISTER™ is a trademark of National Semiconductor Corporation.

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

© 1999 National Semiconductor Corporation

100BASE-FX/

AUI

www.national.com

1 page

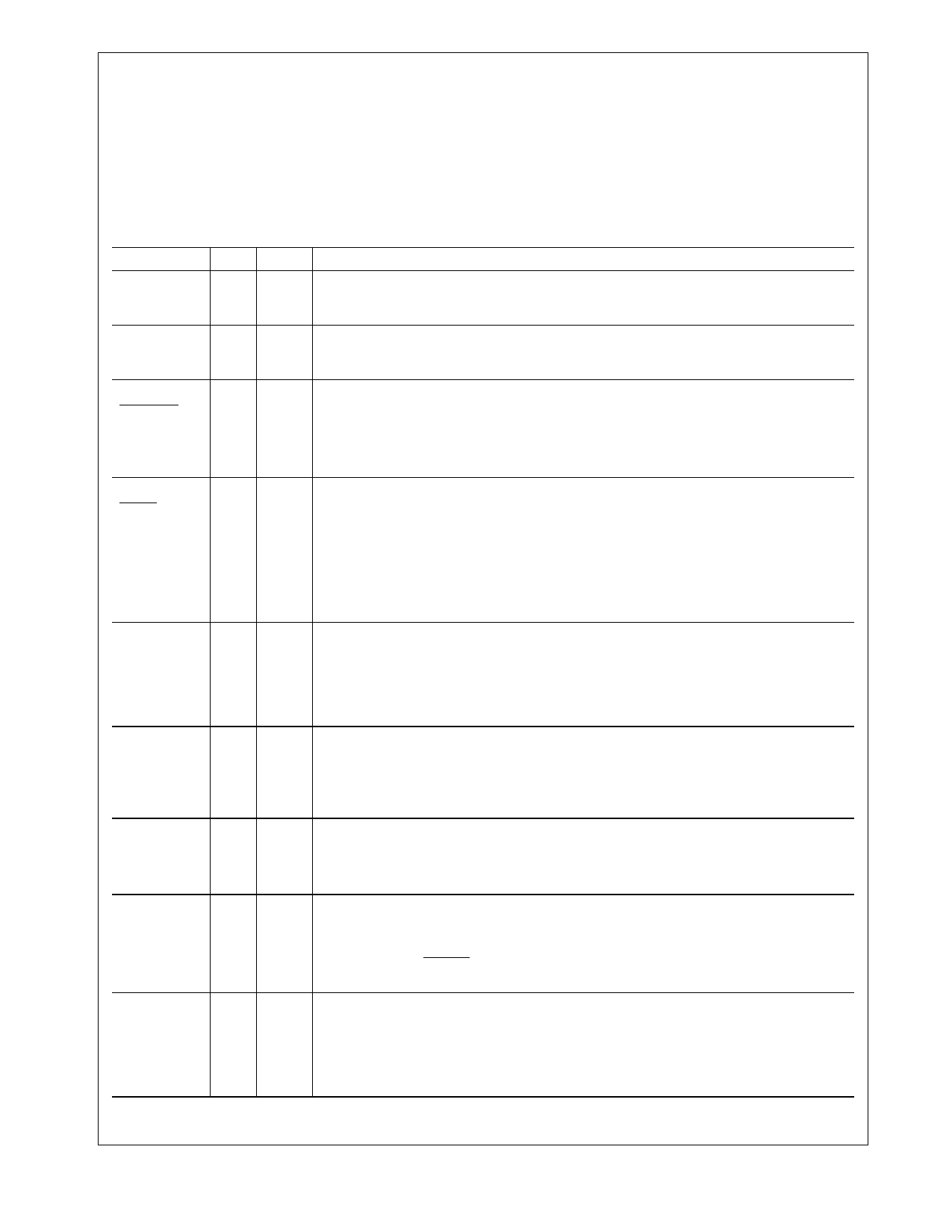

1.0 Pin Descriptions

The DP83843 pins are classified into the following interface

categories. Each interface is described in the sections that

follow.

— MII INTERFACE

— 10/100 Mb/s PMD INTERFACE

— CLOCK INTERFACE

1.1 MII Interface

— DEVICE CONFIGURATION INTERFACE

— LED INTERFACE

— PHY ADDRESS INTERFACE

— RESET

— POWER AND GROUND PINS

— SPECIAL CONNECT PINS

Signal Name Type Pin #

Description

MDC

I 35 MANAGEMENT DATA CLOCK: Synchronous clock to the MDIO management data in-

put/output serial interface which may be asynchronous to transmit and receive clocks.

The maximum clock rate is 2.5 MHz. There is no minimum clock rate.

MDIO

I/O, Z 34

MANAGEMENT DATA I/O: Bi-directional management instruction/data signal that may

be sourced by the station management entity or the PHY. This pin requires a 1.5 kΩ pul-

lup resistor.

CRS

(SYMBOL)

I/O, Z 22

CARRIER SENSE: This pin is asserted high to indicate the presence of carrier due to

receive or transmit activities in 10BASE-T or 100BASE-X Half Duplex modes.

In Repeater or Full Duplex mode, this pin is asserted high to indicate the presence of

carrier due only to receive activity.

In Symbol mode this pin indicates the signal detect status of the TP-PMD (active high).

COL

(FXEN)

I/O, Z 21

COLLISION DETECT: Asserted high to indicate detection of collision condition (asser-

tion of CRS due to simultaneous transmit and receive activity) in 10 Mb/s and 100 Mb/s

Half Duplex modes.

While in 10BASE-T Half Duplex mode with Heartbeat enabled (bit 7, register 18h), this

pin is also asserted for a duration of approximately 1 µs at the end of transmission to

indicate heartbeat (SQE test). During Repeater mode the heartbeat function is disabled.

In Full Duplex mode, for 10 Mb/s or 100 Mb/s operation, this signal is always logic 0.

There is no heartbeat function during 10 Mb/s full duplex operation.

TX_CLK

O, Z 33

TRANSMIT CLOCK: Transmit clock output from the DP83843:

25 MHz nibble transmit clock derived from Clock Generator Module's (CGM) PLL in

100BASE-TX mode.

2.5 MHz transmit clock in 10BASE-T Nibble mode.

10 MHz transmit clock in 10BASE-T Serial mode.

TXD[3]

TXD[2]

TXD[1]

TXD[0]

I 28 TRANSMIT DATA: Transmit data MII input pins that accept nibble data during normal

29 nibble-wide MII operation at either 2.5 MHz (10BASE-T mode) or 25 MHz (100BASE-X

mode).

30

In 10 Mb/s Serial mode, the TXD[0] pin is used as the serial data input pin, and TXD[3:1]

31 are ignored.

TX_EN

I 25 TRANSMIT ENABLE: Active high input indicates the presence of valid nibble data on

TXD[3:0] for both 100 Mb/s or 10 Mb/s nibble mode.

In 10 Mb/s Serial mode, active high indicates the presence of valid 10 Mb/s data on

TXD[0].

TX_ER

(TXD[4])

I 24 TRANSMIT ERROR: In 100 Mb/s mode, when this signal is high and TX_EN is active

the HALT symbol is substituted for the actual data nibble.

In 10 Mb/s mode, this input is ignored.

In Symbol mode (Symbol=0), TX_ER becomes the TXD [4] pin which is the MSB for the

transmit 5-bit data symbol.

RX_CLK

O, Z 18

RECEIVE CLOCK: Provides the recovered receive clock for different modes of opera-

tion:

25 MHz nibble clock in 100 Mb/s mode

2.5 MHz nibble clock in 10 Mb/s nibble mode

10 MHz receive clock in 10 Mb/s serial mode

5 www.national.com

5 Page

1.0 Pin Descriptions (Continued)

1.6 PHY Address Interface

(00000) will result in a PHY isolation condition as a

The DP83843 PHYAD[4:0] inputs provide up to 32 unique result of power-on/reset, as specified in IEEE 802.3u.

PHY address options. An address selection of all zeros

Signal Name

PHYAD[0]

(LED_COL)

Type

I/O

PHYAD[1]

(LED_TX)

I/O

PHYAD[2]

(LED_RX)

I/O

PHYAD[3]

(LED_LINK)

I/O

PHYAD[4]

I/O

(LED_FDPOL)

1.7 Reset

Pin #

Description

42 PHY ADDRESS [0]: PHY address sensing pin for multiple PHY applications. PHY

address sensing is achieved by strapping a pull-up/pull-down resistor (typically 10

kΩ) to this pin as required.

The pull-up/pull-down status of this pin is latched into the PHYCTRL register (ad-

dress 19h, bit 0) during power up/reset.

41 PHY ADDRESS [1]: PHY address sensing pin for multiple PHY applications. PHY

address sensing is achieved by strapping a pull-up/pull-down resistor (typically 10

kΩ) to this pin as required.

The pull-up/pull-down status of this pin is latched into the PHYCTRL register (ad-

dress 19h, bit 1) during power up/reset.

40 PHY ADDRESS [2]: PHY address sensing pin for multiple PHY applications. PHY

address sensing is achieved by strapping a pull-up/pull-down resistor (typically 10

kΩ) to this pin as required.

The pull-up/pull-down status of this pin is latched into the PHYCTRL register (ad-

dress 19h, bit 2) during power up/reset.

39 PHY ADDRESS [3]: PHY address sensing pin for multiple PHY applications. PHY

address sensing is achieved by strapping a pull-up/pull-down resistor (typically 10

kΩ) to this pin as required.

The pull-up/pull-down status of this pin is latched into the PHYCTRL register (ad-

dress 19h, bit 3) during power up/reset.

38 PHY ADDRESS [4]: PHY address sensing pin for multiple PHY applications. PHY

address sensing is achieved by strapping a pull-up/pull-down resistor (typically 10

kΩ) to this pin as required.

The pull-up/pull-down status of this pin is latched into the PHYCTRL register (ad-

dress 19h, bit 4) during power up/reset.

Signal Name Type

RESET

I

Pin #

Description

1 RESET: Active high input that initializes or reinitializes the DP83843. Asserting this

pin will force a reset process to occur which will result in all internal registers reini-

tializing to their default states as specified for each bit in section 7.0, and all strap-

ping options are reinitialized. Refer to section 5.0 for further detail regarding reset.

11 www.national.com

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet DP83843BVJE.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DP83843BVJE | PHYTER | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |