|

|

PDF S3076 Data sheet ( Hoja de datos )

| Número de pieza | S3076 | |

| Descripción | Multi-Rate Sonet/SDH Clock Recovery Unit | |

| Fabricantes | Applied Micro Circuits | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de S3076 (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

®

mDEVICE

.coSMPEUCLITFIIC-RATAIOTEN SONET/SDH CLOCK RECOVERY UNIT

BMiUCLMTOI-SRAPTEECLSOCNLEOTC/KSDGHECNLEORCAKTORRECOVERY UNIT

S3076

S3076

et4UFEATURES

he• SiGe BiCMOS technology

S• Complies with Bellcore and ITU-T specifica-

tations for jitter tolerance, jitter transfer and

ajitter generation

.D• On-chip high frequency PLL with internal

w loop filter for clock recovery

w • Supports clock recovery for:

w OC-48 (2488.32 Mbps) (with FEC)

Fibre Channel (2125 Mbps) (with FEC)

mOC-24 (1244.16 Mbps) (with FEC)

Gigabit Ethernet (1250 Mbps) (with FEC)

oFibre Channel (1062.5 Mbps) (with FEC)

.cOC-12 (622.08 Mbps) (with FEC)

OC-3 (155.52 Mbps) (with FEC) NRZ data

• Selectable reference frequencies

U19.44 MHz or 155.52 MHz

(or equivalent Fibre Channel/

t4Gigabit Ethernet frequencies)

• Lock detect—monitors frequency of

eincoming data

e• Low-jitter serial interface

• +3.3 V supply

h• Compact 48 pin TQFP TEP package

S• Typical power 620 mW

• Available in Die form also

GENERAL DESCRIPTION

The function of the S3076 clock recovery unit is to

derive high speed timing signals for SONET/SDH-

based equipment. The S3076 is implemented using

AMCC’s proven Phase Locked Loop (PLL) technology.

Figure 1 shows a typical network application.

The S3076 receives an OC-48, OC-24, OC-12, OC-3,

Fibre Channel or Gigabit Ethernet scrambled NRZ sig-

nal with FEC capability up to 8 bytes per 255-byte

block and recovers the clock from the data. The chip

outputs a differential bit clock and retimed data.

The S3076 utilizes an on-chip PLL which consists

of a phase detector, a loop filter, and a Voltage

Controlled Oscillator (VCO). The phase detector

compares the phase relationship between the VCO

output and the serial data input. A loop filter con-

verts the phase detector output into a smooth DC

voltage, and the DC voltage is input to the VCO

whose frequency is varied by this voltage. A block

diagram is shown in Figure 2.

ataFigure 1. System Block Diagram

.D16 16

OTX

ORX S3076

wS3057

w16

w www.DataSheet4U.comS3076 ORX

OTX

S3057

16

October 23, 2000 / Revision A

1

1 page

MULTI-RATE SONET/SDH CLOCK RECOVERY UNIT

S3076

FIBRE CHANNEL

JITTER CHARACTERISTICS

Performance

The S3076 PLL complies with the jitter specifications

proposed for Fibre Channel equipment defined by the

fibre channel methodology for Jitter specification.

Input Jitter Tolerance

Input jitter tolerance is defined as the peak to

peak amplitude of sinusoidal jitter applied on the

input signal that causes an equivalent 1 dB opti-

cal/electrical power penalty. Fibre Channel input

jitter tolerance requirements are shown in

Table 3.

Jitter Generation

The jitter of the serial clock and serial data outputs

shall not exceed the value specified in Table 4 when

a serial data input with no jitter is presented to the

serial data inputs.

Figure 5. Fibre Channel System Node Definition

Table 3. Input Jitter Tolerance Specification at

node αR

Parameters

Description

Min Max Units

Frequency Dependent

t Jitter Tolerance

0.10 – UI p-p

FDJ

(637 kHz to ≥ 5 MHz)

Deterministic Jitter

tDJ Tolerance

0.38 – UI p-p

(637 kHz – 531 MHz)

tRJ

Random Jitter

(637 kHz – 531 MHz)

0.22 – UI p-p

tTJ Total Jitter

0.70 – UI p-p

Table 4. Total Jitter Generation Specification at

node αT

Parameters

Description

Min Max Units

DJ Deterministic Jitter

0.08 UI p-p

TJ Total Jitter

0.23 UI p-p

SYSTEM

HOST ADAPTOR

SERDES

αT = Component Transmitter Node

Componet Receiver Node = αR

SYSTEM

STORAGE

DISK DRIVE

SERDES

BACKPLANE

PBC

REPEAETERS

CABLES

CONNECTORS

October 23, 2000 / Revision A

5

5 Page

MULTI-RATE SONET/SDH CLOCK RECOVERY UNIT

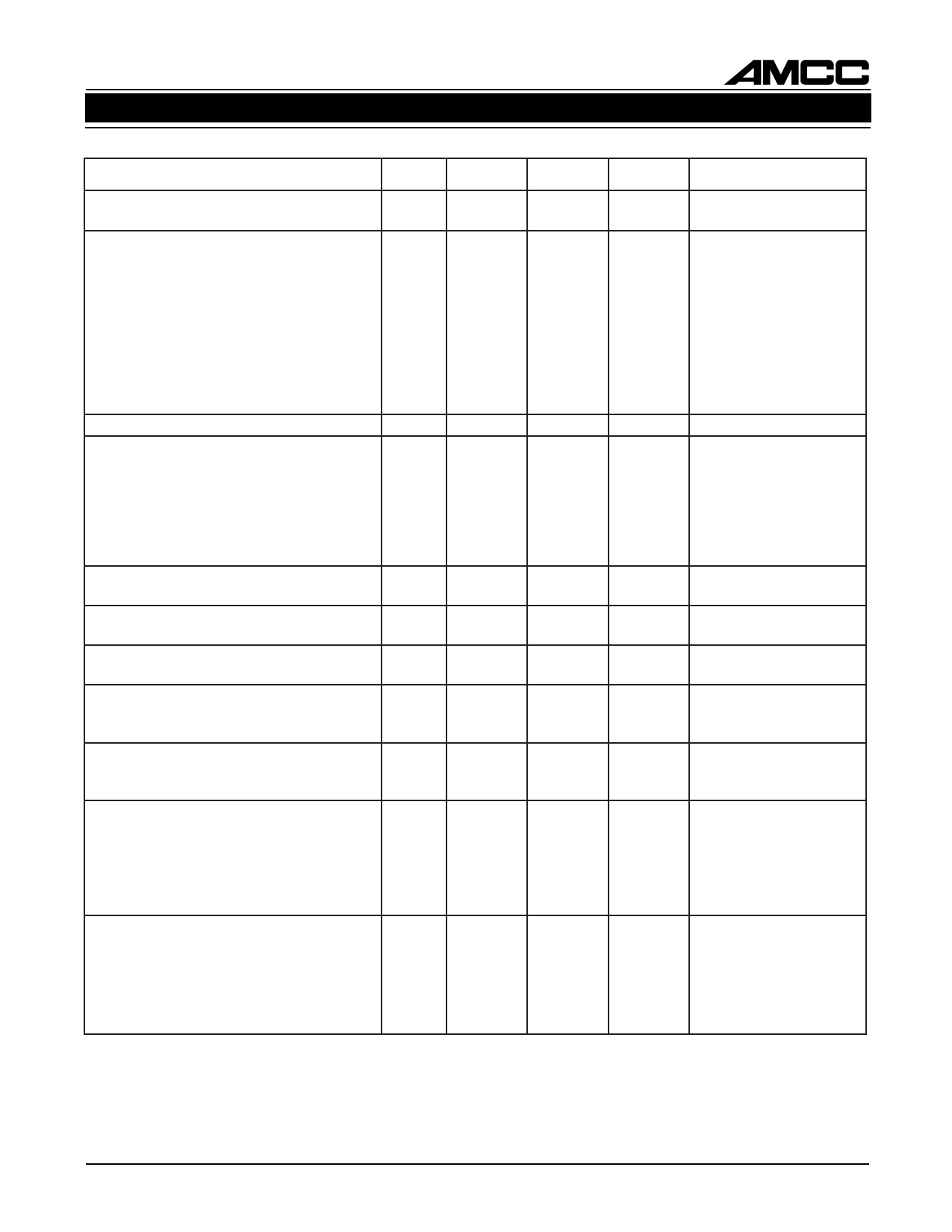

Table 7. Performance Specifications

Parameter

Min Typ

Max

VCO Operating Frequency

Data Output Jitter with VCO locked to

SERDATIP/N

OC-48

2.125 2.488

2.67

0.0038

0.005

OC-24

OC-12

0.002

0.005

OC-3

0.002

0.005

Reference Clock Frequency Tolerance

-100

+100

Acquisition Lock Time (OC-48)

19.44 MHz REFCLK

155.52 MHz REFCLK

1800

250

Reference Clock

Input Duty Cycle

Reference Clock Rise & Fall Times

40

CML Output Rise & Fall Times

Frequency difference at which the PLL

goes out of lock (REFCLK compared to the

divided down VCO clock)

Frequency difference at which the receive

PLL goes into lock (REFCLK compared to

the divided down VCO clock)

tSU

OC-48/Fibre Channel (2125 Mbps)

OC-24/Fibre Channel (1062.5 Mbps)

OC-12

OC-3

tH

450

220

100

250

500

2500

OC-48/Fibre Channel (2125 Mbps)

OC-24/Fibre Channel (1062.5 Mbps)

OC-12

OC-3

100

250

500

2500

60

600

300

60

1.5

120

770

390

S3076

Units Condition

GHz

UI (rms) rms jitter

Not specified in GR-253

UI (rms) rms jitter

UI (rms) rms jitter

ppm

µsec

Minimum transition

density of 20%.

Guaranteed but not

tested.

With device already

powered up and valid

ref. clk.

% of UI

ns

20% to 80% of

amplitude.

ps

20% to 80%, 50 Ω load,

1 pF cap.

ppm

ppm

ps See Figure 8.

ps See Figure 8.

October 23, 2000 / Revision A

11

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet S3076.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S307 | Silicon Power Rectifier | Microsemi Corporation |

| S30720 | Silicon Power Rectifier | Microsemi Corporation |

| S30740 | Silicon Power Rectifier | Microsemi Corporation |

| S3076 | Multi-Rate Sonet/SDH Clock Recovery Unit | Applied Micro Circuits |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |