|

|

PDF TDA8261TW Data sheet ( Hoja de datos )

| Número de pieza | TDA8261TW | |

| Descripción | Satellite Zero-IF QPSK/8PSK downconverter with PLL synthesizer | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de TDA8261TW (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

TDA8261TW

Satellite Zero-IF QPSK/8PSK

downconverter with PLL

synthesizer

Product specification

Supersedes data of 2004 Oct 25

2004 Dec 02

1 page

Philips Semiconductors

Satellite Zero-IF QPSK/8PSK

downconverter with PLL synthesizer

Product specification

TDA8261TW

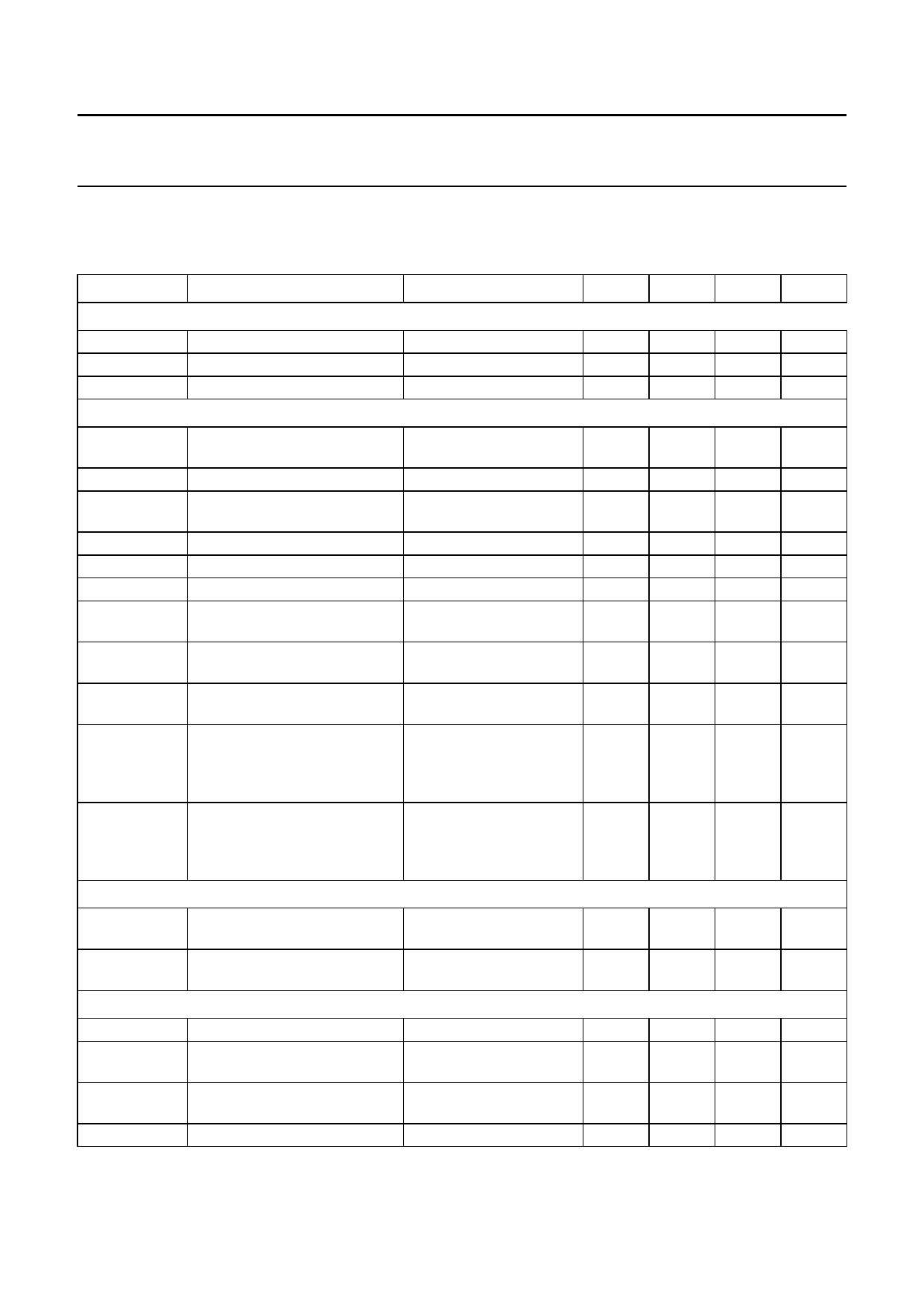

PINNING

SYMBOL

XT1

XT2

VCC(PLL)

PLLGND

AGCIN

BIASN1

RFGND1

VCC(RF)

RFA

RFB

RFGND2

QOUT

BBGND1

QBBIN

VCC(BB)

QBBOUT

IBBOUT

BIASN2

IBBIN

BBGND2

IOUT

VCOGND

TKB

TKA

VCC(VCO)

BVS

VT

CP

AS

SCL

SDA

XTOUT

PIN DESCRIPTION

1 4 MHz crystal oscillator input 1

2 4 MHz crystal oscillator input 2

3 supply voltage for PLL circuit (5 V)

4 ground for PLL circuit

5 AGC input from satellite

demodulator and decoder

6 RF isolation input 1 (5 V)

7 ground 1 for RF circuit

8 supply voltage for RF stage (5 V)

9 RF signal input A

10 RF signal input B

11 ground 2 for RF circuit

12 quadrature output for external

filtering

13 ground 1 for baseband stage

14 quadrature baseband input after

external filtering

15 supply voltage for baseband stage

(5 V)

16 quadrature baseband output to

satellite demodulator and decoder

17 in-phase baseband output to

satellite demodulator and decoder

18 RF isolation input 2 (5 V)

19 in-phase baseband input after

external filtering

20 ground 2 for baseband stage

21 in-phase output for external filtering

22 ground for VCO circuit

23 VCO tank circuit input B

24 VCO tank circuit input A

25 supply voltage for VCO circuit (5 V)

26 bus voltage select input

27 tuning voltage output for VCO

28 charge pump output

29 address selection input

30 I2C-bus clock input

31 I2C-bus data input and output

32 4 MHz crystal oscillator output to

satellite demodulator and decoder

handbook, halfpage

XT1 1

32 XTOUT

XT2 2

31 SDA

VCC(PLL) 3

PLLGND 4

30 SCL

29 AS

AGCIN 5

28 CP

BIASN1 6

27 VT

RFGND1 7

26 BVS

VCC(RF) 8

25 VCC(VCO)

TDA8261TW

RFA 9

24 TKA

RFB 10

23 TKB

RFGND2 11

22 VCOGND

QOUT 12

21 IOUT

BBGND1 13

20 BBGND2

QBBIN 14

19 IBBIN

VCC(BB) 15

QBBOUT 16

18 BIASN2

17 IBBOUT

MBL855

Fig.2 Pin configuration.

2004 Dec 02

5

5 Page

Philips Semiconductors

Satellite Zero-IF QPSK/8PSK

downconverter with PLL synthesizer

Product specification

TDA8261TW

CHARACTERISTICS

Tamb = 25 °C; VCC = 5 V; unless otherwise specified; RL = 1 kΩ on base band output IBBOUT and QBBOUT;

Vo(p-p) = 750 mV on IBBOUT and QBBOUT.

SYMBOL

PARAMETER

CONDITIONS

MIN. TYP. MAX. UNIT

Supply

VCC

ICC

VPOR

supply voltage

supply current

voltage limit where POR active

4.75

−

−

Performances from pins RFA or RFB to pins IBBOUT or QBBOUT

LOleak

LO leakage through pins RFA

and RFB

−

∆Gv

Gv(max)

dynamic voltage gain range

maximum voltage gain

VAGC = 0 to 3 V

VAGC = 3 V;

see Figs 4 and 5

48

55

Vo(p-p)

IP2i

IP3i

F

Zo

output voltage (peak-to-peak)

2nd-order interception point

3rd-order interception point

noise figure

output impedance on pin IOUT

and QOUT

recommended value

at RF input; VAGC = 0 V

at RF input; VAGC = 0 V

at maximum gain;

VAGC = 3 V; see Fig.6

−

−

−

−

−

Zi input impedance on pin IBBIN

and QBBIN

−

Gv(I-Q)

voltage gain mismatch between

I and Q

in 22.5 MHz band with

bypass capacity 100 nF

between IOUT and IBBIN,

QOUT and QBBIN

−

∆Φ

absolute quadrature error

VAGC = 1.5 V;

Vo = 750 mV (peak to

peak value); measured in

baseband

−

5.00

130

2.7

−75

50

57

750

19

14

18

35

1.0

−

0

5.25

−

−

−

−

−

−

−

−

−

−

−

1

3

V

mA

V

dBm

dB

dB

mV

dBm

dBm

dB

Ω

kΩ

dB

deg

Pulling sensitivity

3/4LO

sensitivity to pulling on the third see Table 9 and Fig.8

harmonic of the external VCO

5/4LO

sensitivity to pulling on the fifth see Table 9 and Fig.8

harmonic of the external VCO

−

−

−40 −35 dBc

−40 −35 dBc

VCO and synthesizer

fosc

ϕn(osc)

oscillator frequency

oscillator phase noise in the

satellite band

ϕn phase noise on baseband

outputs

MDR

main divider ratio

foffset = 100 kHz; out of

PLL loop bandwidth

foffset = 1 and 10 kHz;

fCOMP = 1 MHz; see Fig.7

950

−

−

64

−

−100

−

−

2 175

−94

MHz

dBc/Hz

−78 dBc/Hz

32 767

2004 Dec 02

11

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet TDA8261TW.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TDA8261TW | Satellite Zero-IF QPSK/8PSK downconverter with PLL synthesizer | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |