|

|

PDF DS1205S Data sheet ( Hoja de datos )

| Número de pieza | DS1205S | |

| Descripción | MultiKey Chip | |

| Fabricantes | Dallas Semiconducotr | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DS1205S (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

DS1205S

DS1205S

MultiKey Chip

FEATURES

• Three secure read/write data partitions of 384 bits

each

• One non-secure read/write data partition of 512 bits

• Secure data cannot be deciphered by reverse engi-

neering

• Guaranteed unique, 48-bit, laser etched serial

number

• 64-bit password and I.D. fields provide positive identi-

fication and security for each secure data partition

• Maximum data transfer rate of 2 million bits/second

• Low-power CMOS circuitry

• Access via 3-wire or 1-wire interface

• Applications include proprietary data, financial trans-

actions, secure personnel areas, and systems ac-

cess control

PIN ASSIGNMENT

VCCI

NC

RST

DQ

NC

CLK

NC

GND

1

2

3

4

5

6

7

8

VCCO

16

15 NC

14 I/O

13 GND

12 NC

11 DQOE

10 NC

9 BAT

DS1205S 16-Pin SOIC (300 mil)

See Mech. Drawings

Section

PIN DESCRIPTION

VCCI

RST

– +5V Supply (Battery Backup Mode)

– Reset (3-Wire)

DQ – Data (3-Wire)

CLK – Clock (3-Wire)

GND

– Ground

BAT – Battery (+) (Battery Backup Mode)

DQOE

– Data Available (3-Wire)

I/O – Data I/O (1-Wire)

VCCO

– Battery (+) (Battery Powered Mode)

DESCRIPTION

The DS1205S MultiKey Chip is an enhanced version of

the DS1204U Electronic Key which has both a standard

3-wire interface (data, clock, and reset) and a 1-wire in-

terface. The DS1205S MultiKey has three secure read/

write subkeys which are each 384 bits in length. In addi-

tion, there is a 512-bit read/write scratchpad which can

be used as a non-secure data area or as a holding regis-

ter for data transfer to one of the three subkeys. Each

subkey within the part is uniquely addressable on byte

boundaries.

OPERATING MODES

There are two modes of operation for powering the

DS1205S MultiKey Chip. In the Normal Mode (Battery

Backup), VCC power is supplied to the part on the VCCI

pin, while the battery backup source is applied to the

BAT pin. In this mode of operation, the chip supply is

switched internally between VCCI and BAT (depending

on which is higher) and this level is presented internally

to the VCCO pin. In the Battery Operate Mode, the bat-

tery supply is connected directly to the VCCO pin while

the VCCI and BAT pins are grounded.

021798 1/17

1 page

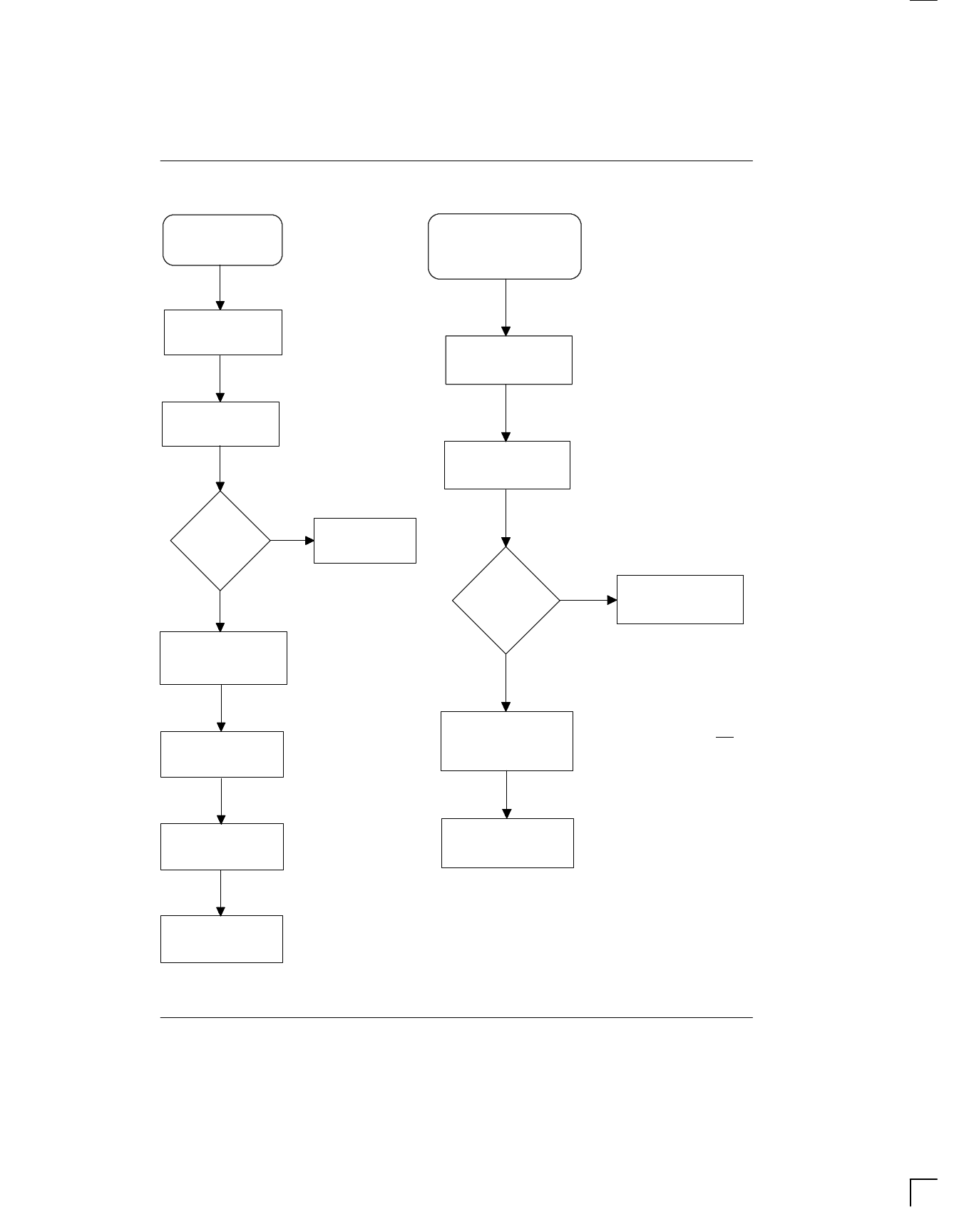

SET SECURITY MATCH Figure 5

WRITE SET PASSWORD

IN COMMAND WORD

(SPECIFY WHICH

SECURE PARTITION)

SET SECURE DATA Figure 6

WRITE SET SECURE DATA

IN COMMAND WORD (SPECIFY

WHICH SECURE PARTITION AND

STARTING BYTE ADDRESS)

DS1205S

READ I.D. FIELD FROM

SECURE PARTITION

(64 BITS)

WRITE 64 BITS OF DATA

TO DS1205

(OLD I.D.)

READ I.D. FIELD FROM

SECURE PARTITION

(64 BITS)

WRITE 64 BITS OF DATA

TO DS1205

IS DATA = I.D?

NO

YES

ERASE I.D. AND PASSWORD

FIELD, SECURE DATA

FIELD FOR SELECTED

SECURE PARTITION.

TERMINATE

TRANSACTION

WRITE 64 BITS OF DATA

FOR NEW I.D. FIELD DATA

IS DATA =

PASSWORD?

NO

TERMINATE

TRANSACTION

YES

WRITE DATA TO SECURE

DATA FIELD (STARTING

ADDRESS SPECIFIED IN

COMMAND WORD)*

*Data is written to the DS1205S beginning

at the specified address and continuing

until either Bit 511 is written or the RST

line is brought low.

WRITE 64 BITS OF DATA

FOR NEW PASSWORD

FIELD DATA

TERMINATE TRANSACTION

TERMINATE

TRANSACTION

021798 5/17

5 Page

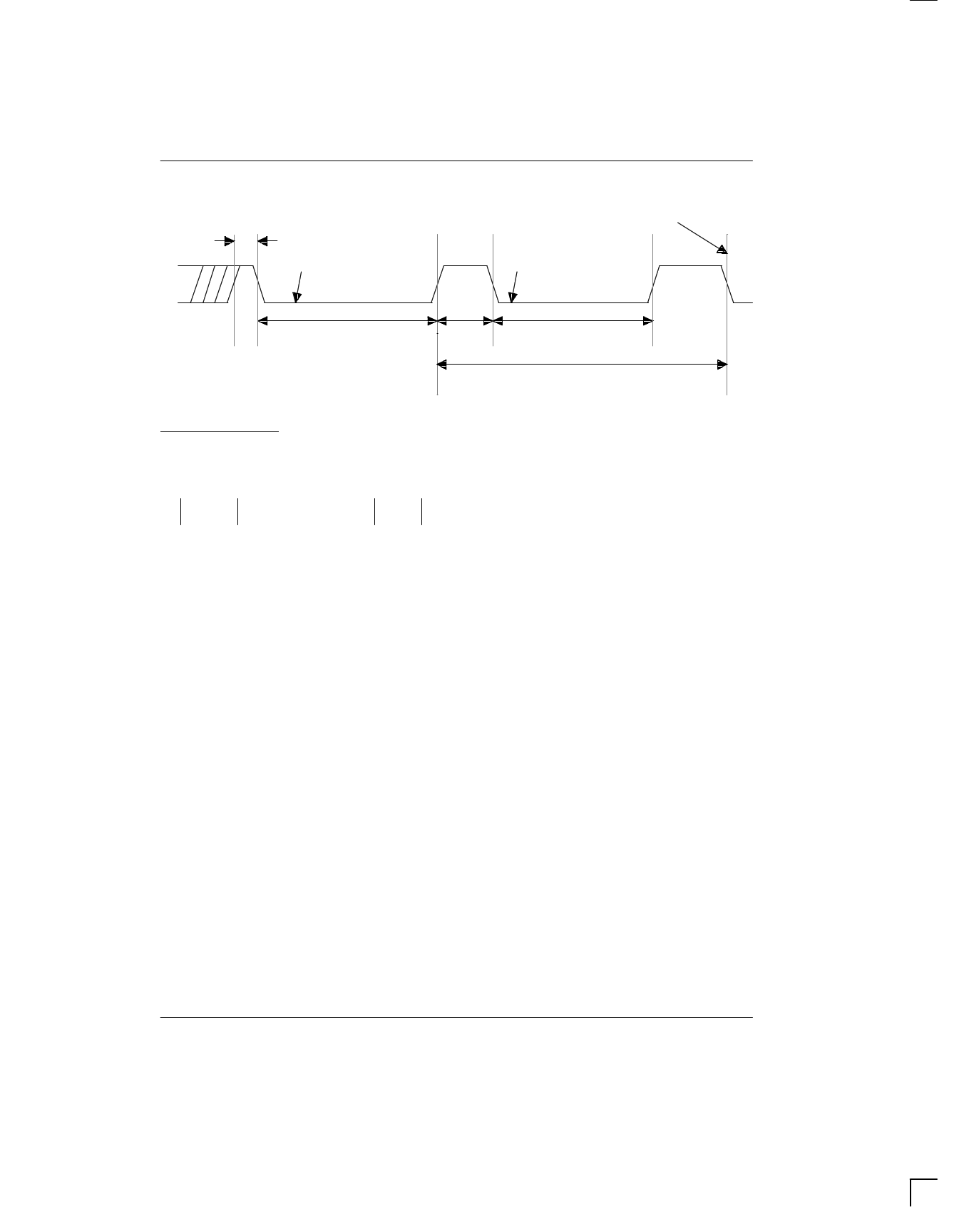

RESET/PRESENCE DETECT SEQUENCE Figure 17

tSYC

RESET PULSE

DRIVEN LOW

BY HOST

IDLE

STATE

DS1205S

FIRST BIT OF 1–WIRE

PROTOCOL

PRESENCE DETECT

DRIVEN BY 1–WIRE

DEVICE

tRSTL

tPDH

tPDL

tRSTH

1-Wire I/O Commands - Once the bus master has de-

tected a presence, it can issue one of the four different

1-wire I/O commands. These commands deal with the

laser-etched ROM code which has the following format.

Type ID

8 bits

Unique Serial Number CRC

48 bits

8 bits

All 1-wire commands are eight bits long. A list of these

commands are as follows:

CCh Pass Thru Mode

This command saves time by allowing direct ac-

cess to the DS1205S without identifying it by

ROM ID number. This command can only be used

when there is a single slave on the bus. If more

than one device is present, there will be bus con-

tention.

33h Read ROM Data

This command allows the bus master to read the

DS1205S’s unique 48-bit ID number and CRC.

This command can only be used if there is a

single DS1205S on the bus. If more than one is

present, there will be bus contention.

55H Match ROM Data

This mode allows the bus master to single out a

specific DS1205S on a multidrop bus. The bus

master selects the specific slave by the ROM ID

number for the transaction. This command can be

used with a single or multiple device on the bus.

F0h Search ROM Data

When a system is initially brought up, the bus

master might not know the number or types of de-

vices on the bus. By invoking the Search ROM

Data command the bus master can, by process of

elimination, find the ID numbers of all the devices

on the bus. Once this is known, the bus master

can then go back and read the device type that

corresponds to each ID number.

The ROM search process is the repetition of a simple

3-step routine: read a bit, read the complement of the

same bit, then write the desired value of that bit. The bus

master performs this simple 3-step routine on each bit of

the ROM. After one complete pass, the bus master

knows the contents of the ROM in one device. The bus

is reset and the process is repeated again, selecting a

different set of bit values. The bus master controls the

search according to what values are written as select

bits.

The following example of the ROM search process as-

sumes four different devices are connected to the same

1-wire bus. The ROM data of the four devices is as

shown:

ROM1

ROM2

ROM3

ROM4

00110101...

10101010...

11110101...

00010001...

The search process is as follows:

1. The bus master begins by resetting all devices pres-

ent on the 1-wire bus. After this, the bus master will

attempt to read the family code, serial number, and

CRC value for the part.

2. The bus master will then issue the Search ROM

Data command on the 1-wire bus.

3. The bus master performs two reads and receives

two 0 bits. This indicates that both 1 bits and 0 bits

exist as the first bit of the devices on the bus.

021798 11/17

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet DS1205S.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS1205S | MultiKey Chip | Dallas Semiconducotr |

| DS1205V | MultiKey | Dallas Semiconducotr |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |